Multi-cycle non-pipeline CPU debugging method based on finite state machine

A finite state machine and debugging method technology, applied in the computer field, can solve problems such as complex circuits, large consumption, CPU operating status and efficiency impact, and achieve the effect of less additional circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

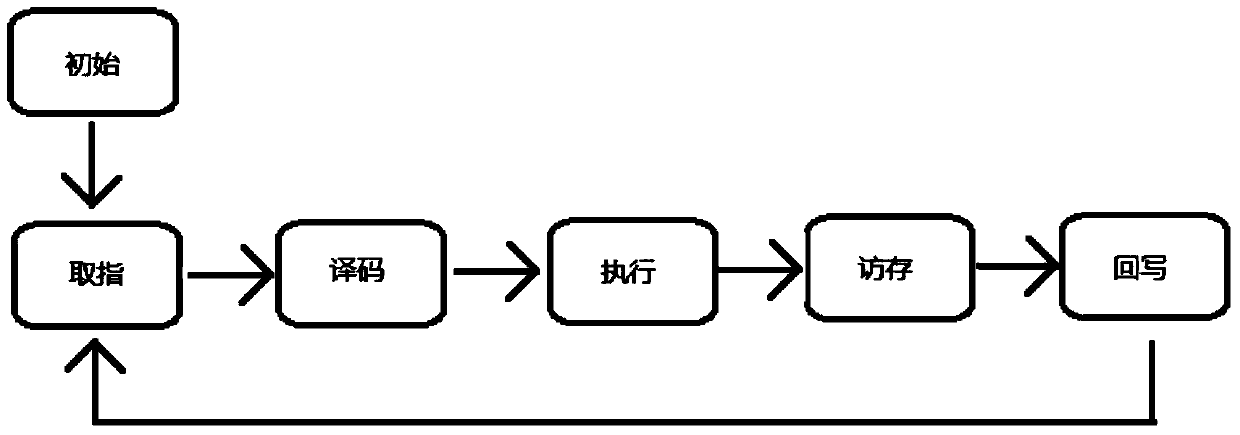

[0019] Such as figure 1 As shown, the steps for the CPU to process each instruction are instruction fetching, decoding, execution, memory access, and write-back in sequence; the jump between steps is realized by a finite state machine;

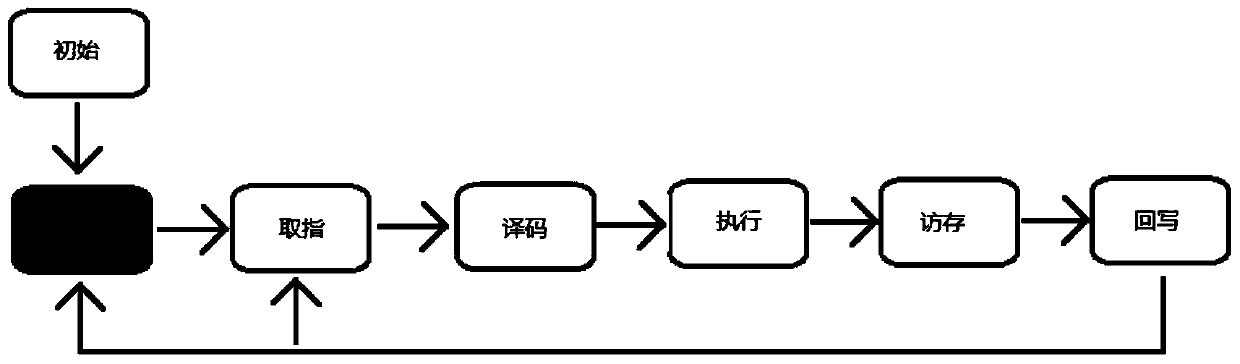

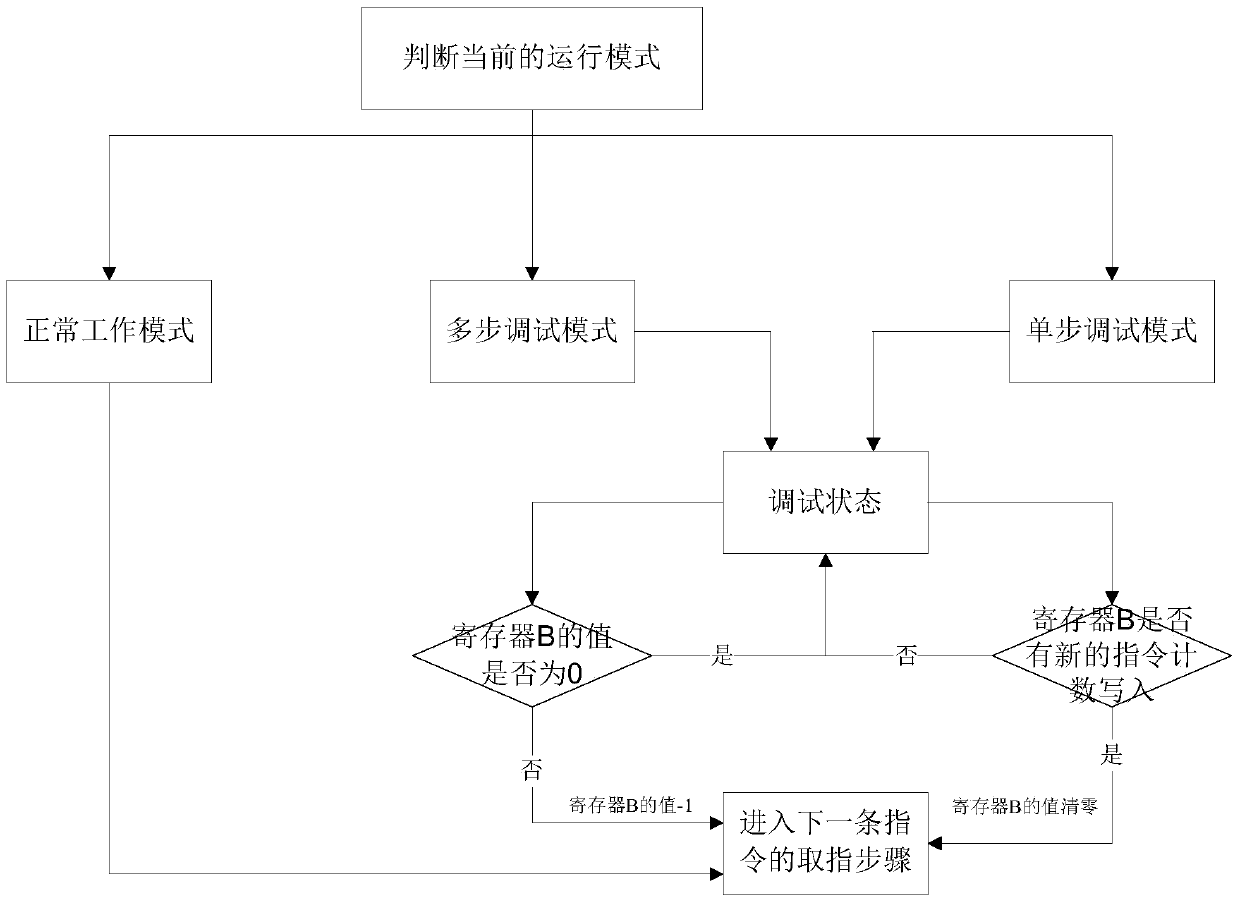

[0020] In the embodiment of the present invention, CPU debugging is realized by introducing register A and register B. At the same time, a decision state is inserted into the finite state machine, such as figure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More