Method for forming fin field effect transistor

A fin field effect and transistor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that the performance of fin field effect transistors needs to be improved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] As mentioned in the background technology, the performance of the fin field effect transistor formed by the prior art still needs to be improved, for example, the stress exerted by the stress source region and the drain region on the channel region of the fin field effect transistor formed by the prior art is still relatively limited .

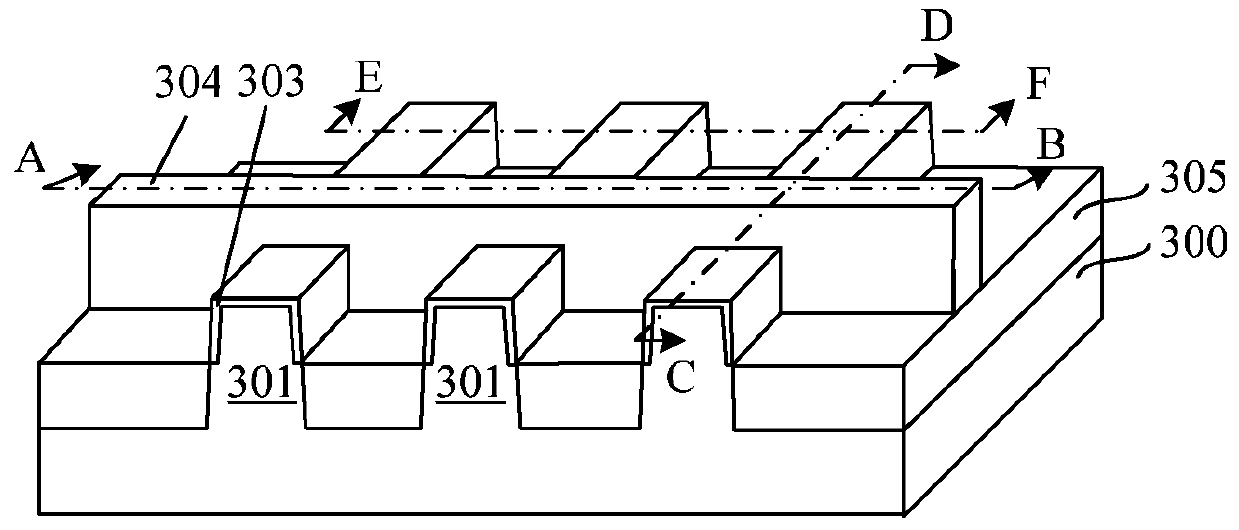

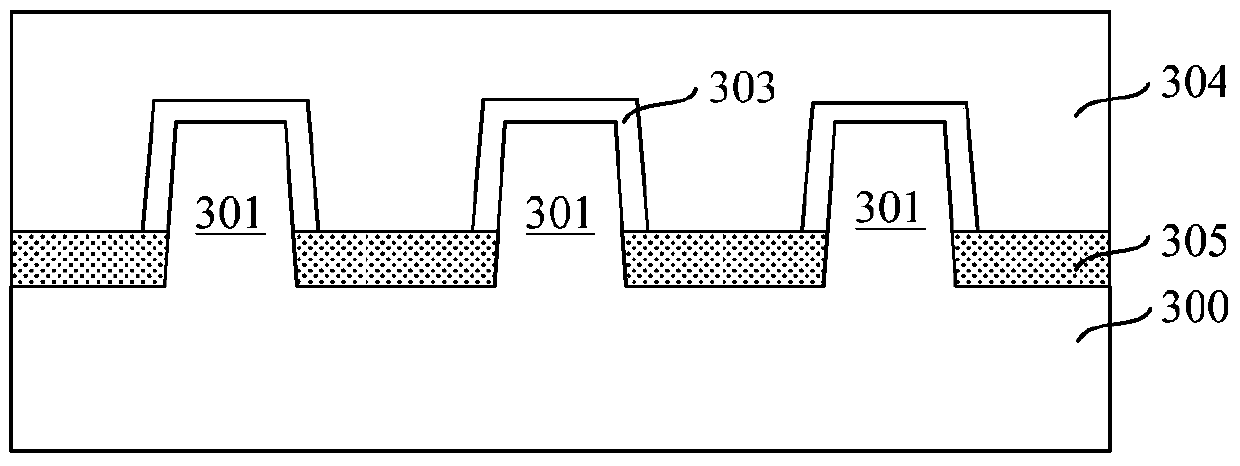

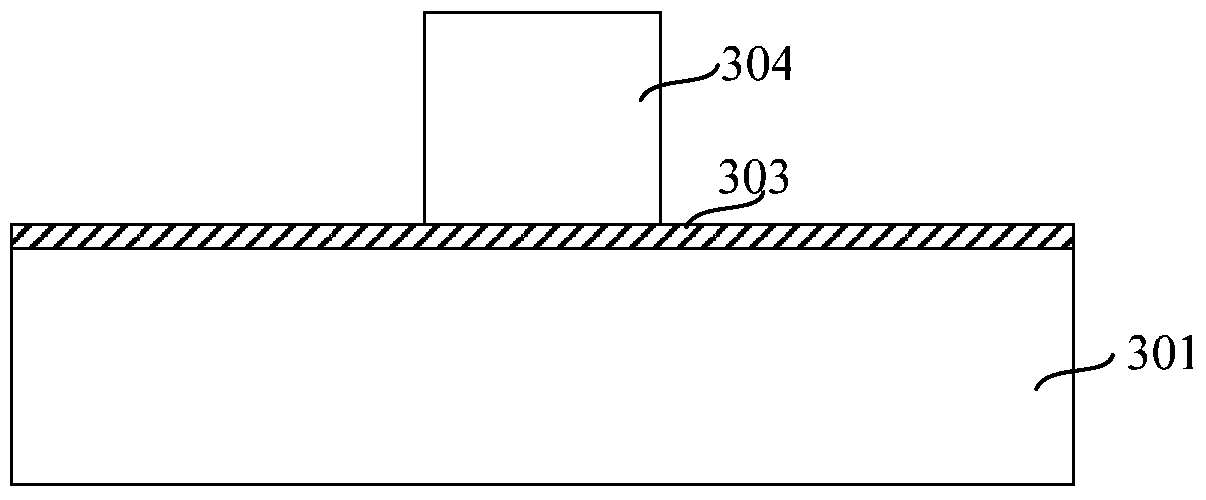

[0036] The formation process of the prior art fin field effect transistor is studied, including: providing a semiconductor substrate on which a raised fin is formed; forming a sidewall and a top surface across a portion of the fin The gate structure includes a gate dielectric layer located on the sidewall and top surface of the fin and a gate electrode located on the gate dielectric layer, the material of the gate dielectric layer is silicon oxide, and the formation process is thermal Oxidation, the material of the gate electrode is polysilicon; Re-oxidize the sidewall of the gate electrode to repair the etching damage; Form an offset s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More