Integrated circuit with optimized layout

A technology of integrated circuits and power lines, applied in the field of circuit design, can solve the problem of high cost, achieve the effect of reducing conflicts, reducing costs, and reducing the number of metal layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

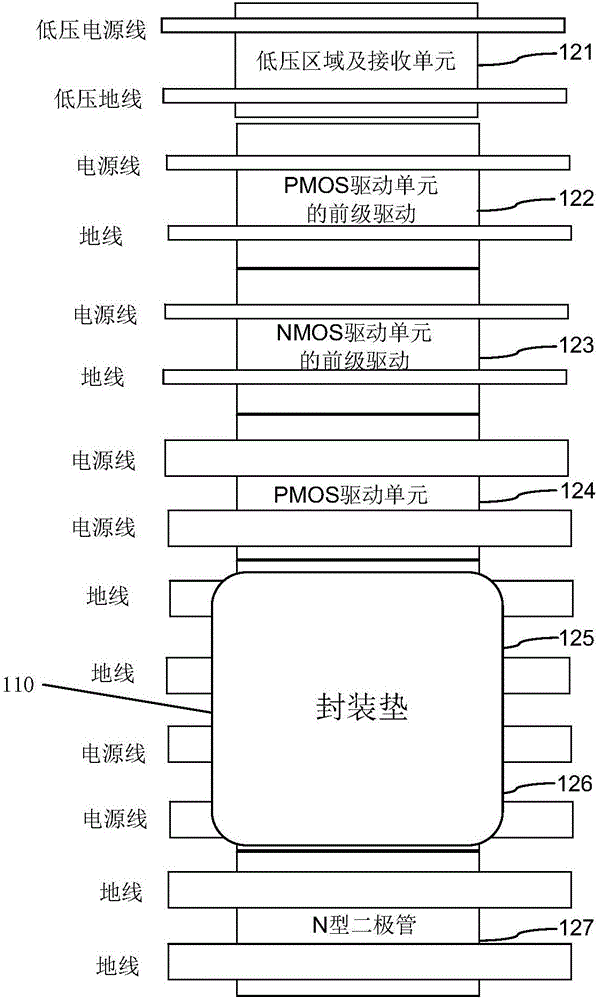

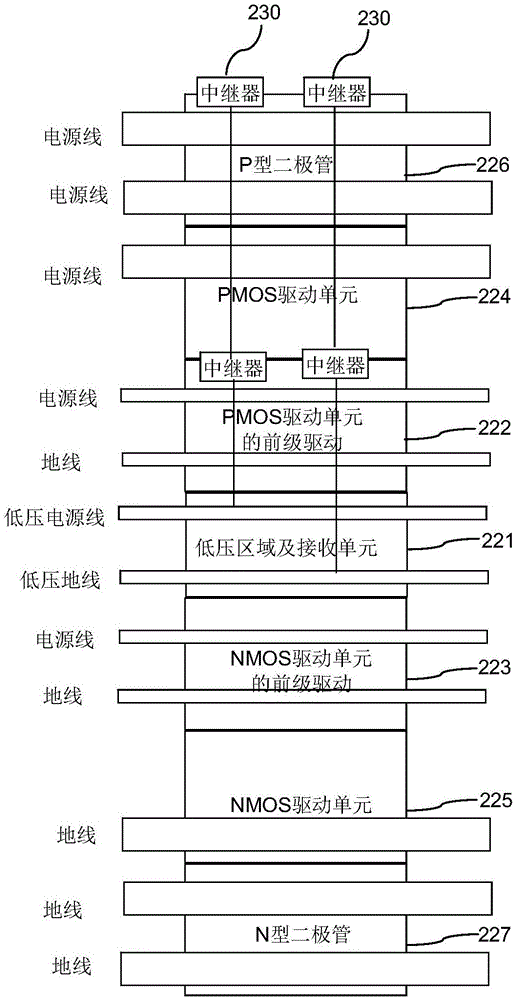

[0023] The present invention changes the layout of the traditional interface unit so that the main power line / ground area in the interface unit is separated from the package pad area, thereby reducing the conflict between the package pad and the power line / ground line in the interface unit, thereby reducing the overall The number of metal layers reduces costs.

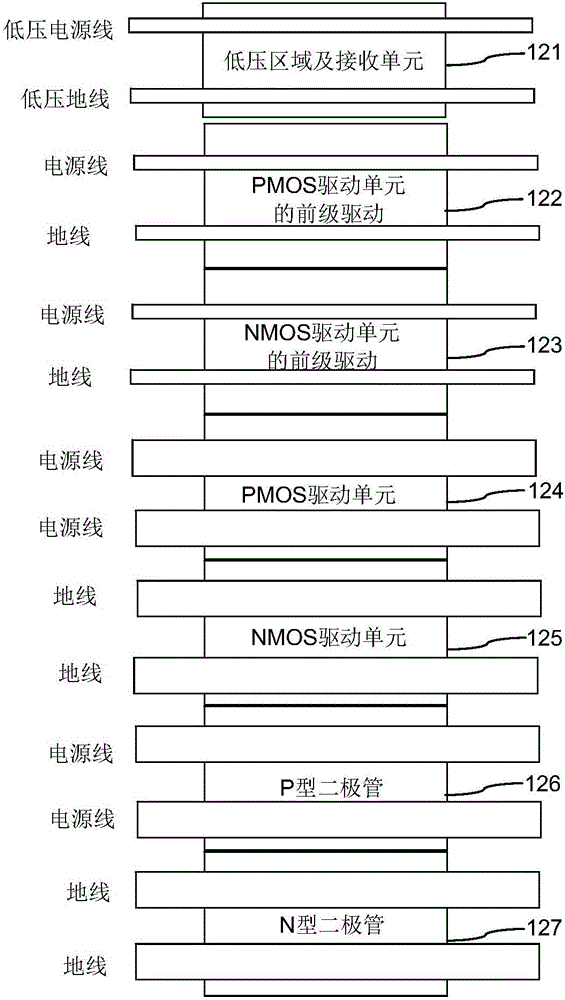

[0024] Please refer to image 3 As shown, it is a schematic diagram of the layout layout of the signal unit that does not show the package pad in one embodiment of the present invention; please refer to Figure 4 shown in the image 3 A schematic diagram of the layout layout of the signal unit after adding the package pad in . Depend on image 3 and Figure 4 It can b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More