A Hardware-Based Adaptive Network Architecture and Adaptive Network Method

A self-adaptive network and hardware technology, applied in electrical components, digital transmission systems, secure communication devices, etc., can solve problems such as increased system burden, complex data processing procedures, and many changes to network protocol stacks to meet network adaptation requirements. , the effect of reducing system load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

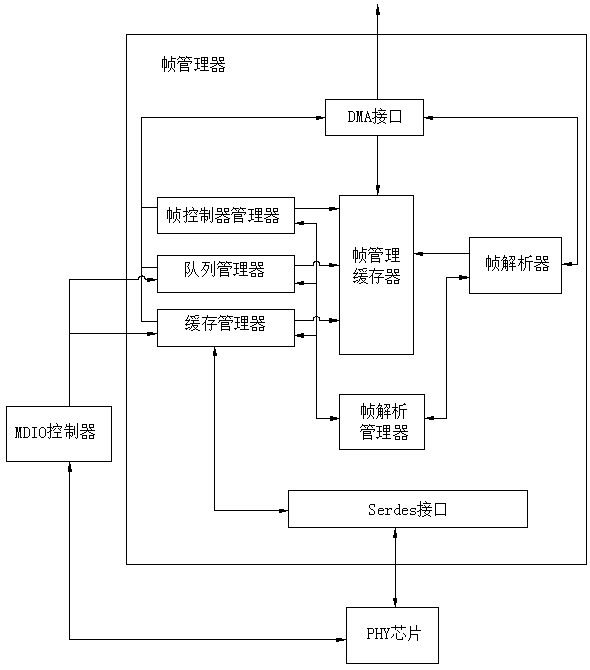

[0018] A hardware-based adaptive network architecture of the present invention, its structure includes a PHY chip, an MDIO controller and a frame manager, and the frame manager includes a frame management controller, a queue manager, a buffer manager, a frame analysis manager, a frame Parser, frame management buffer, Serdes interface and DMA interface, PHY chip is connected with Serdes interface and MDIO controller respectively, Serdes interface is connected with buffer manager, MDIO controller is connected with buffer manager and queue manager respectively, buffer management The device, the queue manager, the frame management controller and the frame parser are all connected with the frame parsing manager, and the buffer manager, the queue manager, the frame management controller and the frame parser are all connected with the frame management buffer, and the buffer manager, The queue manager, the frame management controller, the frame parser and the frame management buffer ar...

Embodiment 2

[0027] A hardware-based adaptive network method of the present invention uses the hardware-based adaptive network architecture in Embodiment 1 to analyze and transmit network messages, and the steps are:

[0028] (1) Read the network status of the PHY chip through the MDIO controller;

[0029] (2) According to the network status of the PHY chip, the MDIO controller controls the frame buffer manager and the queue manager to adjust the resolution rate of the network message in the frame manager;

[0030] (3) According to the network status of the PHY chip, the MDIO controller controls the frame buffer manager and the queue manager to adjust the transmission rate of the network message in the DMA interface, and the transmission rate of the network message in the DMA interface can adapt to the external communication of the PHY chip. transmission rate.

[0031] Among them, the step of adjusting the resolution rate of the network message in the frame analyzer in step (2) is: accord...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More