A chip input pin testing method and device

A test device and test method technology, applied in the direction of measuring device, single semiconductor device test, semiconductor/solid-state device test/measurement, etc., can solve problems such as waste of material and financial resources, high test cost, and complicated chip replacement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to explain in detail the technical content, structural features, achieved goals and effects of the technical solution, the following will be described in detail in conjunction with specific embodiments and accompanying drawings.

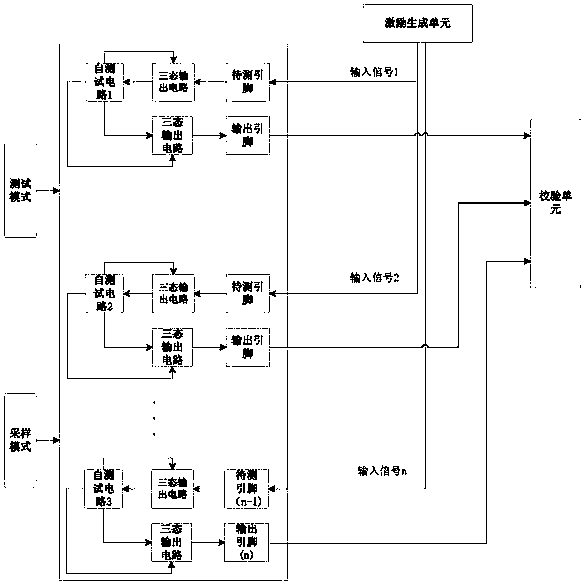

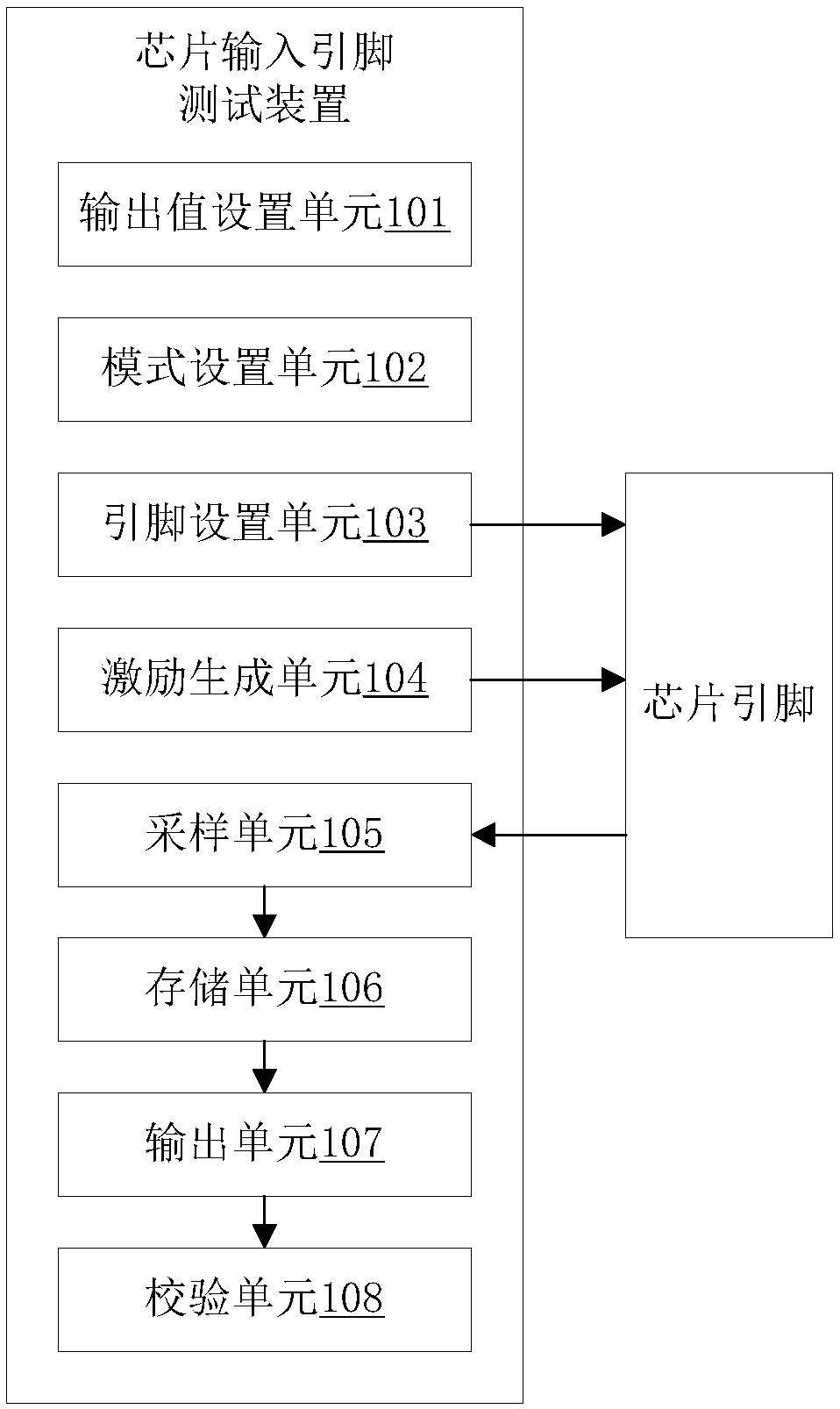

[0043] see figure 1 , a schematic diagram of a chip input pin testing device according to an embodiment of the present invention.

[0044] The chip includes at least one pin to be tested, and the device includes an output value setting unit 101, a mode setting unit 102, a pin setting unit 103, an excitation generating unit 104, a sampling unit 105, a storage unit 106, an output unit 107 and a calibration unit. Test unit 108. Pins, also known as pins, are the wiring from the internal circuit of the integrated circuit (chip) to the peripheral circuit, and all the pins constitute the external interface of the chip.

[0045] The output value setting unit 101 is used to set an output preset value;

[0046] The mode setting unit 102 is u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More