An electric fuse storage unit and an electric fuse storage array

A technology of memory cells and memory arrays, applied in the field of semiconductors, to achieve the effect of improving the speed of read operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

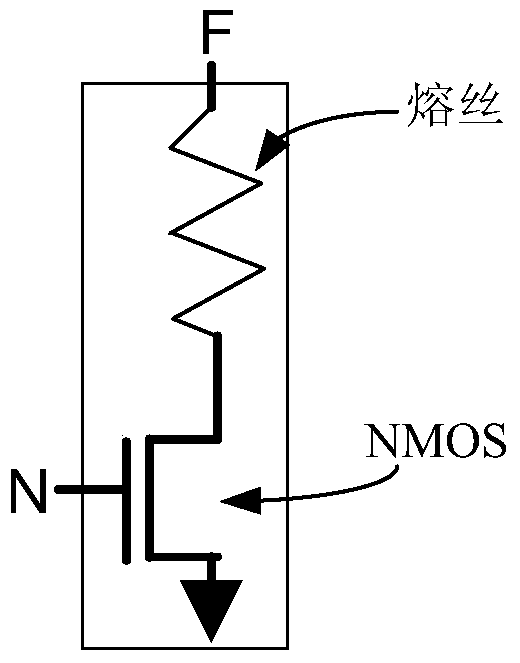

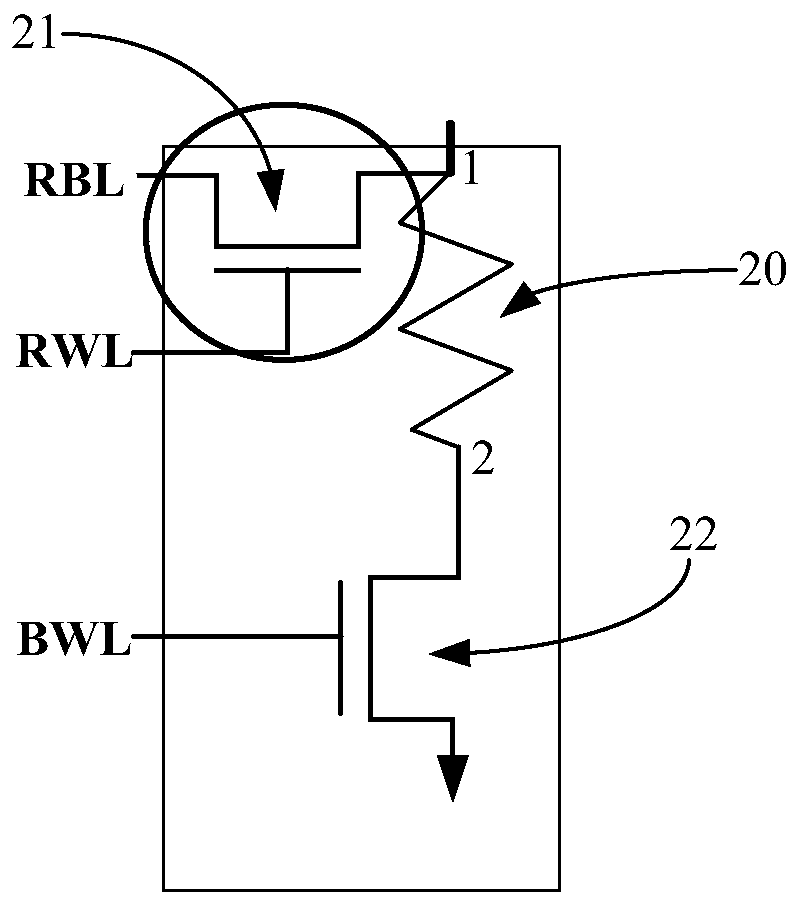

[0048] Below, refer to figure 2 An eFuse storage unit proposed by an embodiment of the present invention will be described.

[0049] Exemplarily, as figure 2 The shown eFuse storage unit of the present invention comprises the following elements:

[0050] An electric fuse 20 is included, and the electric fuse 20 has a first end 1 and a second end 2 opposite to the first end 1 . The first end of the electric fuse is connected to a second bit line (not shown).

[0051] Exemplarily, the material of the electric fuse 20 may include polysilicon. Wherein the first end 1 is the anode of the electric fuse 20 , and the second end is the cathode of the electric fuse 20 .

[0052] It also includes a first transistor 21, the drain of the first transistor 21 is connected to the first terminal 1 of the electric fuse 20, the gate of the first transistor 21 is connected to the read word line RWL, and the first A source of a transistor 21 is connected to the read bit line RBL.

[0053] ...

Embodiment 2

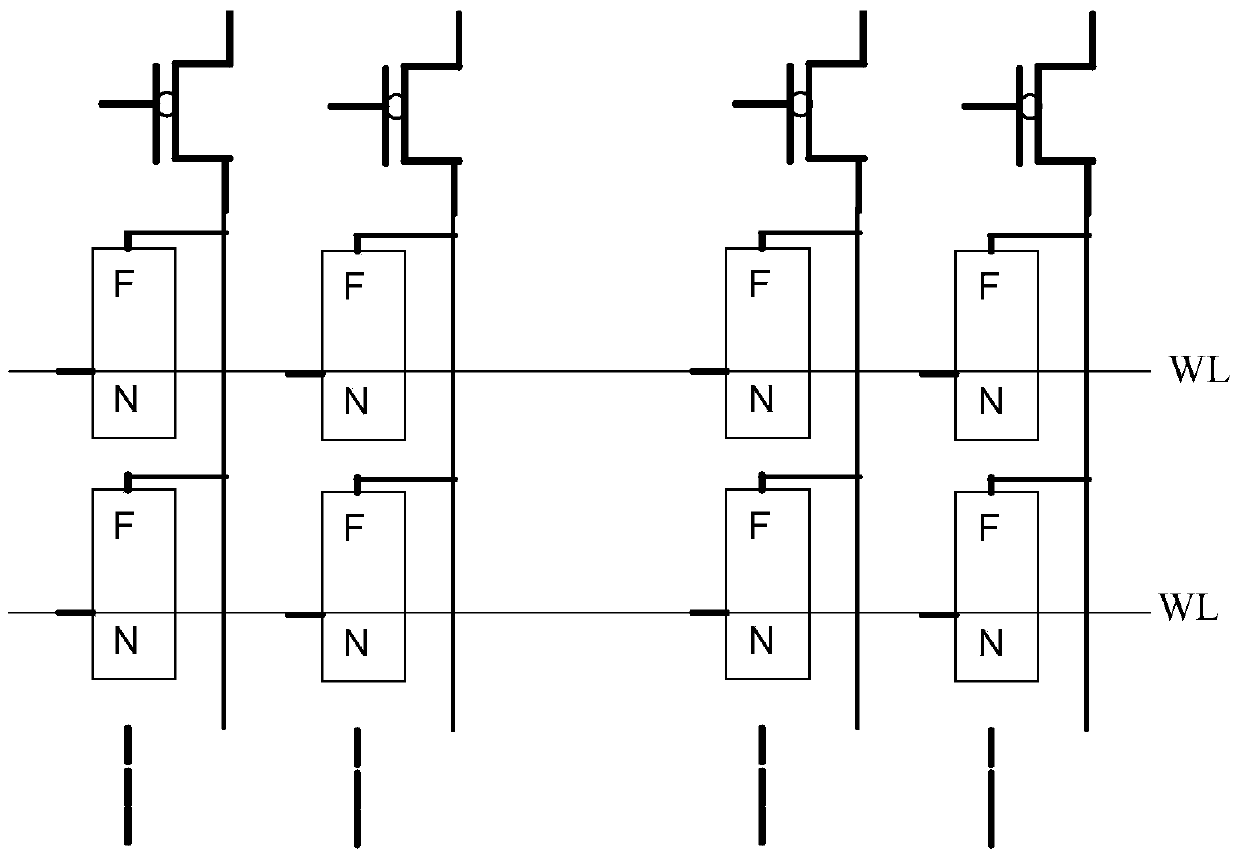

[0062] Another embodiment of the present invention further provides an electric fuse storage array, which includes the electric fuse storage unit in the foregoing embodiments.

[0063] Specifically, refer to image 3 The electric fuse memory array in the embodiment of the present invention is described in detail.

[0064] The electric fuse storage array of this embodiment includes several electric fuse memory cells 30, and the several electric fuse memory cells 30 are arranged in multiple rows and multiple columns, for example, arranged in m rows and n columns, wherein m and n is an integer.

[0065] The electric fuse memory array in the embodiment of the present invention also includes several rows of read bit lines RBL (for example, read bit line RBL1, read bit line RBL2, etc.), several rows of read word lines RWL (for example, read word line RWL1, read word line line RWL2, etc.), several rows of burnt word lines BWL (for example, burnt word line BWL1, burnt word line BWL2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More