On-board direct current voltage reduction chip failure analysis method

A technology of DC voltage reduction and failure analysis, applied in the field of vehicle, can solve problems such as failure location and uneconomical efficiency, and achieve the effect of high speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

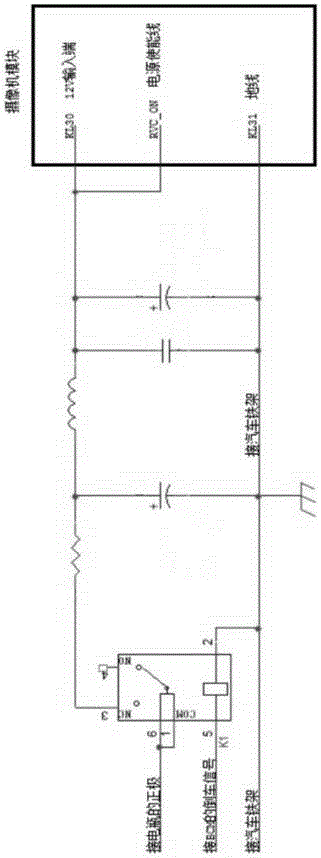

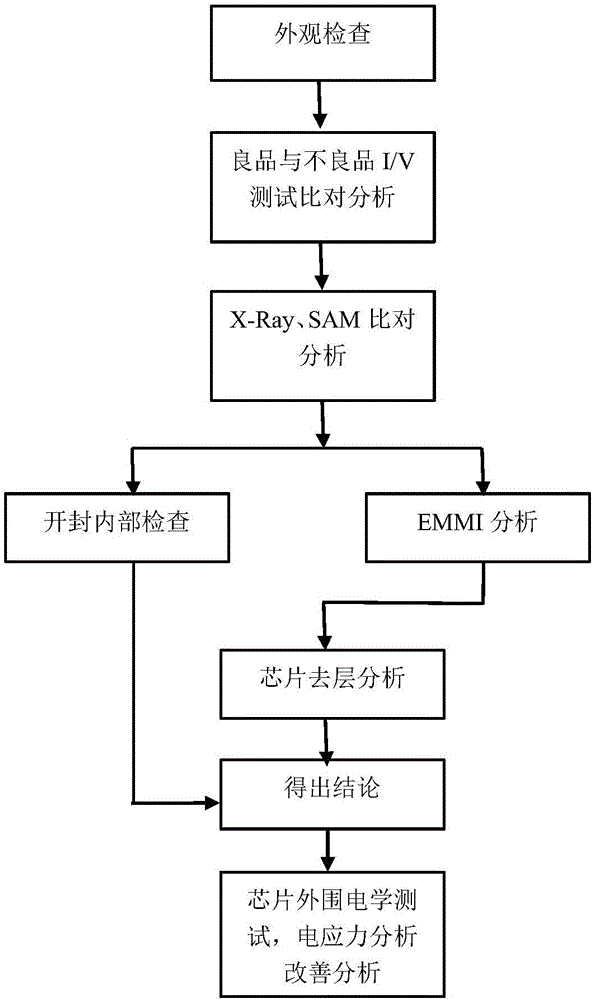

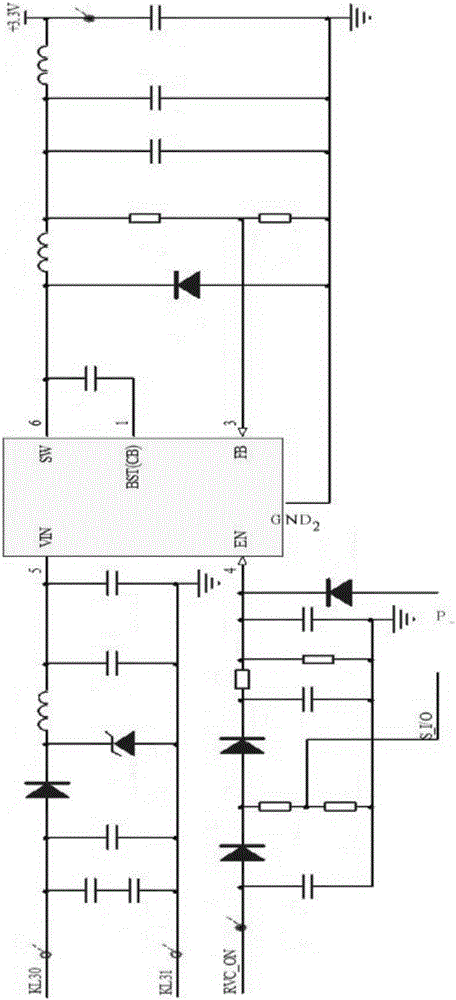

[0023] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0024] refer to figure 1 As shown, a failure analysis method for a vehicle-mounted DC step-down chip includes the following steps:

[0025] Step 1) Appearance inspection, by observing the appearance of the circuit board, to see whether there is obvious damage on the outside, to determine whether the circuit board itself has any problems that affect the use, and there is no external damage in this embodiment, record;

[0026] Step 2) Comparative analysis of the I / V...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More