MOS-used adaptive body bias dynamic threshold generator

A body and threshold technology, applied in the field of MOS, which can solve the problems such as the increase of the maximum stable operating frequency of the chip, the low threshold of the MOS transistor, and the high leakage current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] One or more embodiments are described below. These described embodiments are merely examples of implementation techniques as defined only by the appended claims. Furthermore, in order to provide a focused description, unrelated features of an actual implementation may not be described in this specification.

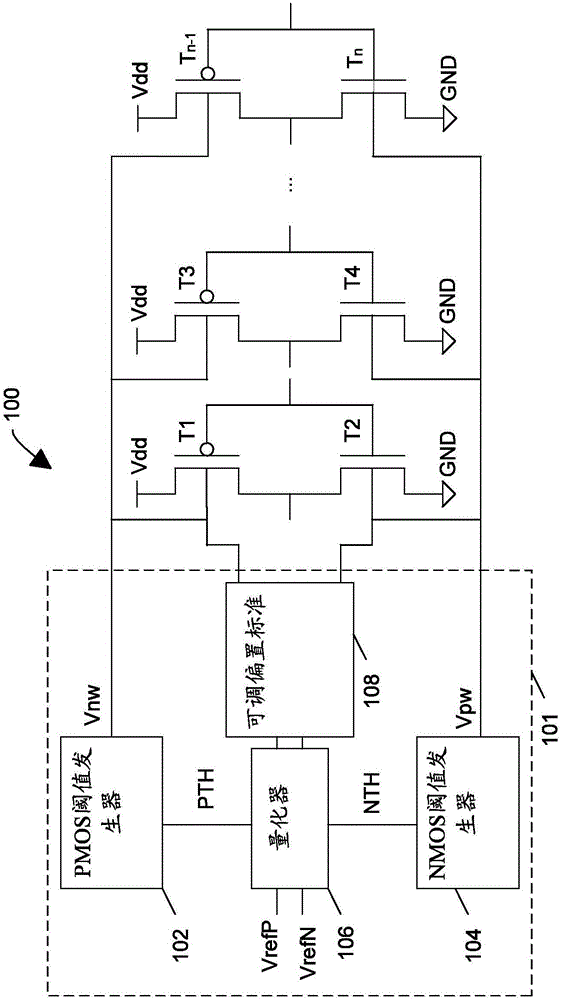

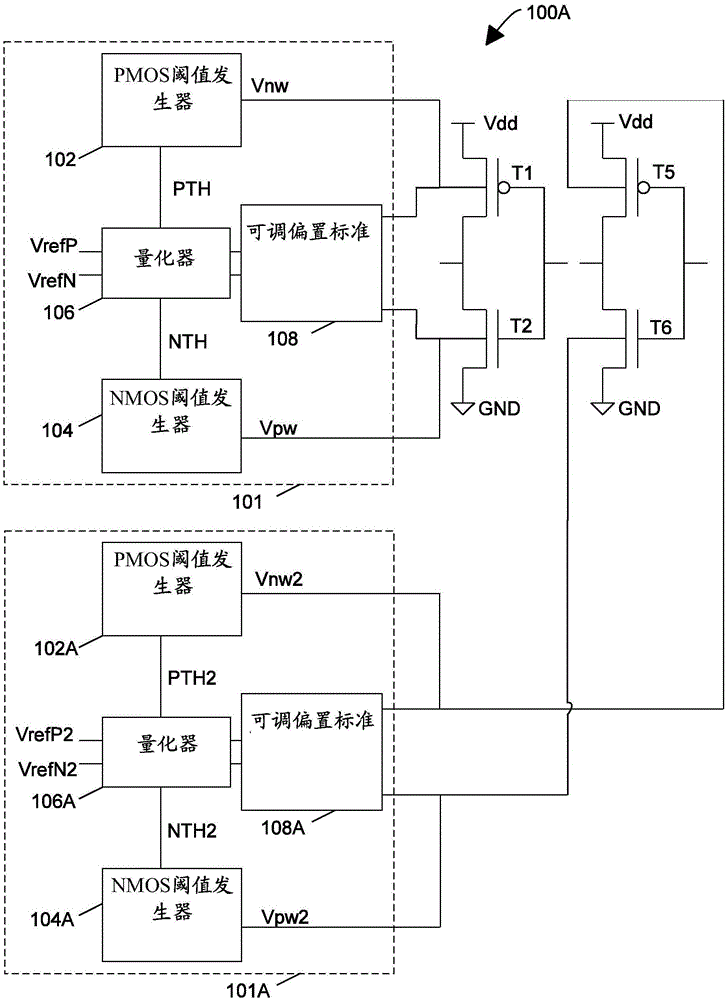

[0033] first reference figure 1 , the electronic device 100 is now described. The electronic device 100 is an integrated circuit and comprises two pairs of CMOS transistors T1 , T2 and T3 , T4 and a body bias circuit 101 for biasing the bodies of these transistors thereby setting their threshold voltages. It should be understood that transistor pairs T1 , T2 and T3 , T4 are so represented for simplicity, and that the electronic device 100 may have any number of transistor pairs Tn−1 , Tn. The body bias circuit 101 in the electronic device 100 may bias any number of CMOS transistors.

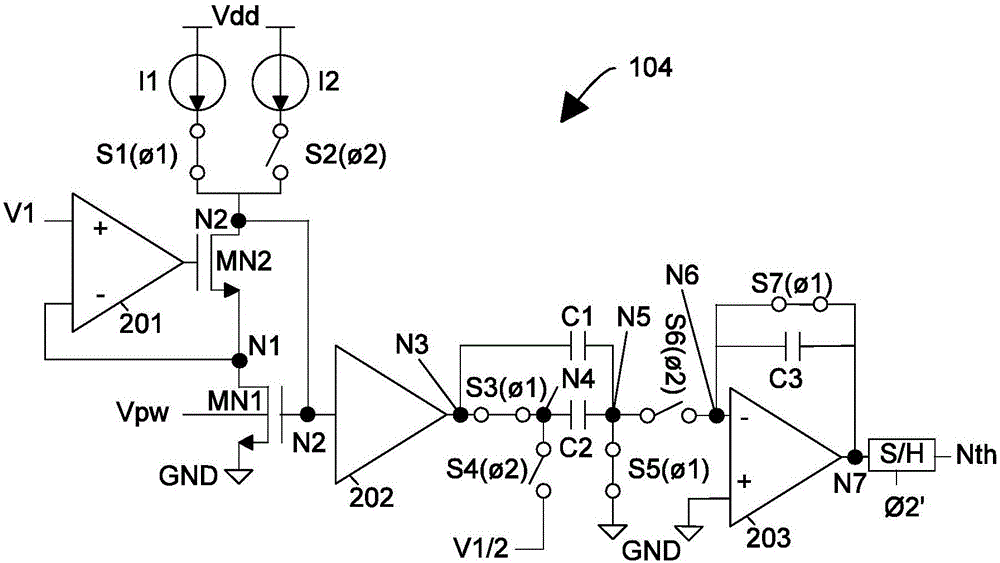

[0034] The body bias circuit 101 includes a PMOS threshold generator 102 and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More