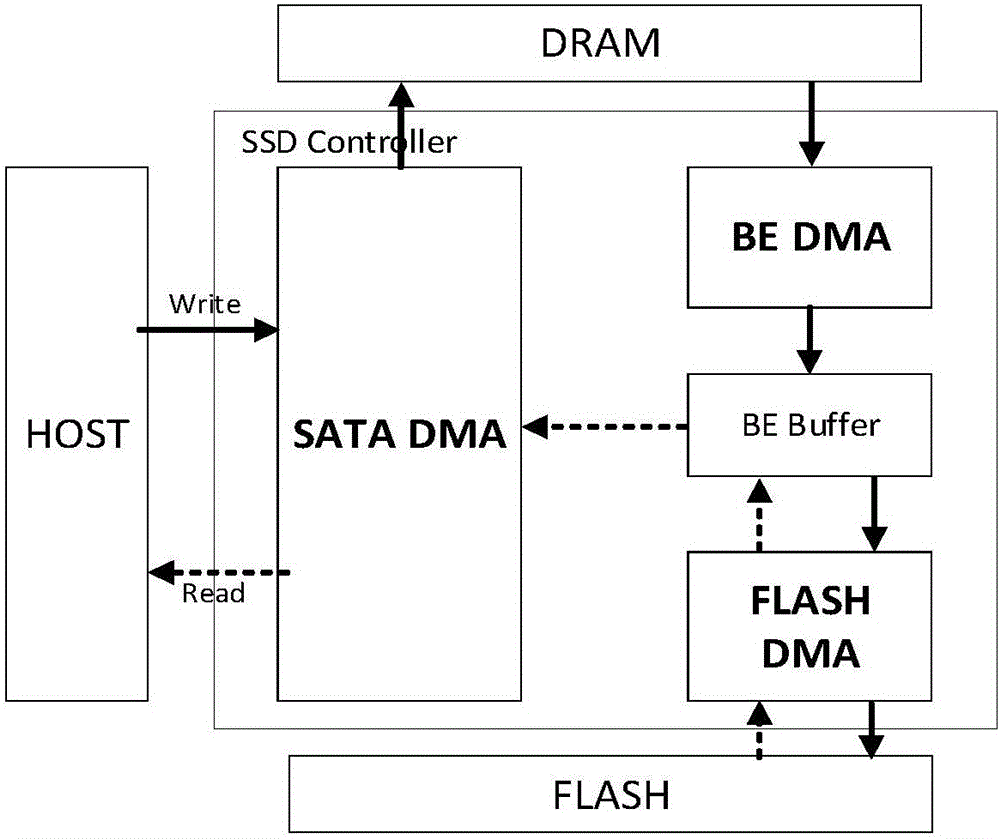

SSD master control BE Buffer, SSD master control, data transmission management device and data transmission management method

A technology of data transmission and management device, which is applied in electrical digital data processing, input/output process of data processing, input/output to record carrier, etc., and can solve the problems of large IO transmission efficiency deterioration, long invalid waiting time between DMAs, etc. , to achieve the effect that the transmission efficiency will not deteriorate, the invalid waiting time will be reduced, and the CPU time resources will be saved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

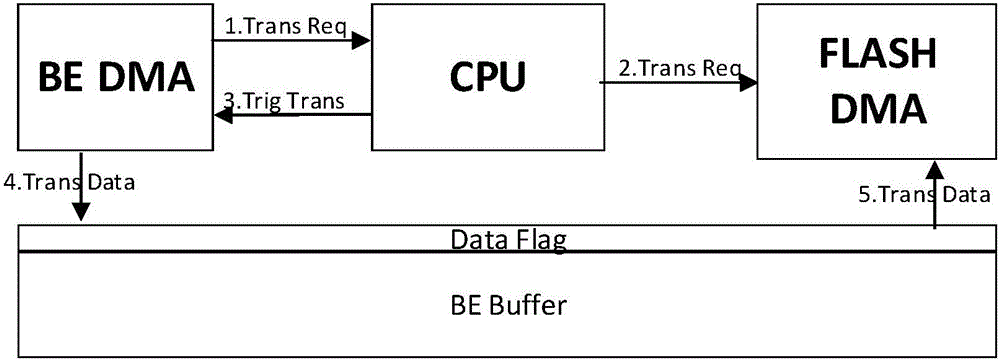

[0039] Such as image 3 , the realization process of the present invention is as follows:

[0040] 1. Agree on the specified size of the storage unit and the Data Flag space. The Buffer between DMAs is composed of multiple storage units. Each storage unit has its own 1-bit or multi-bit information corresponding to it in the Data Flag. If the Data Flag of a certain storage unit is in state 0, it means that the storage unit is not full; if the Data Flag of a certain storage unit is in state 1, it means that the data in this storage unit is full. as in image 3 The agreed storage unit is 512B in size, and each storage unit has its own 1-bit information corresponding to it in the Data Flag. Status 0 indicates that the Data Flag value of the storage unit is 0, and status 1 indicates that the Data Flag value of the storage unit is 0. Buffer between DMAs is BE Buffer.

[0041] 2. On the basis of 1, when Write DMA needs to write a storage unit in the buffer, if its Data Flag is in st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More