LDPC (Low-Density Parity-Check) decoding algorithm based on variable-node lazy serial layered scheduling

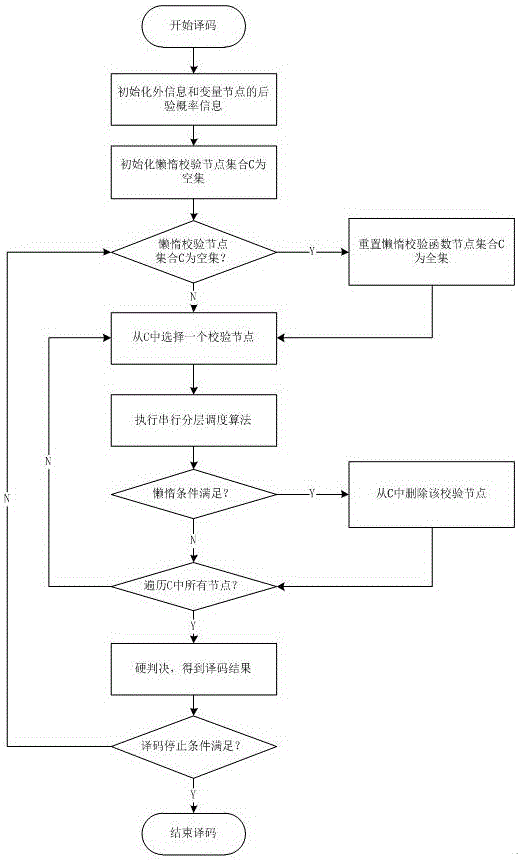

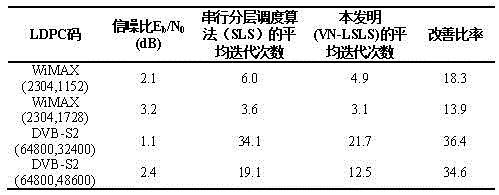

A variable node, hierarchical scheduling technology, applied in the field of low-density parity-check code decoding algorithms, can solve the problems of high delay and power consumption, slow convergence, etc., to reduce delay, power consumption, and improve error The effect of code performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

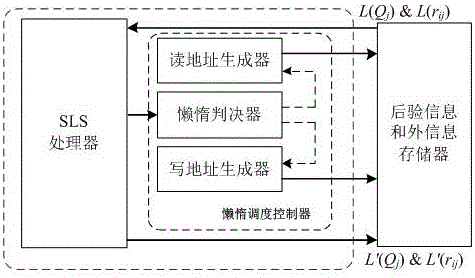

[0045] LDPC code decoding algorithm among the present invention can be realized in FPGA platform, figure 2 The functional block diagram of its realization is given. The decoder includes a serial hierarchical scheduling processor (SLS processor), a lazy scheduling controller, a posteriori information (L(Q j )) and extrinsic information (L(r ij)) memory. The serial hierarchical scheduling processor (SLS processor) updates the posterior information of the variable nodes adjacent to the check node according to the posterior information and extrinsic information, and its process is consistent with the traditional serial hierarchical scheduling algorithm, and generates intermediate variables min(i) and smin(i) for the lazy scheduling controller to make decisions. The lazy scheduling controller includes a read address generator, a write address generator and a lazy judger. The lazy judger judges whether a certain variable node satisfies the lazy judgment condition according to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More