Method and system for extracting parasitic capacitance

A parasitic capacitance, integrated circuit technology, applied in the field of extracting parasitic capacitance, can solve the problems of geometric pattern deviation, inaccurate extraction of parasitic capacitance, etc., and achieve the effect of improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

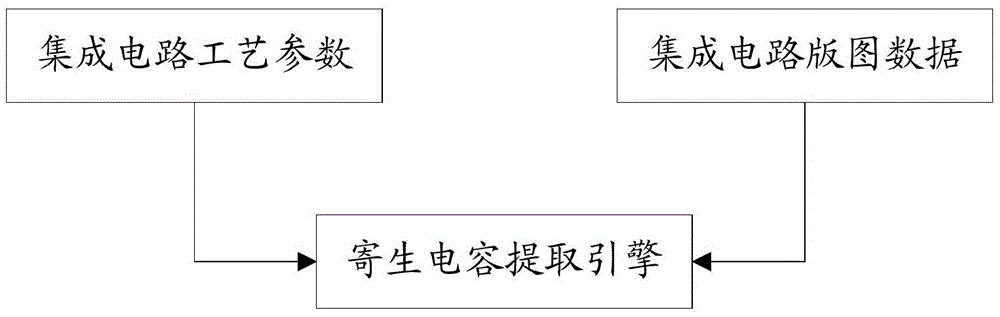

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] In order to enable those skilled in the art to better understand the solutions of the embodiments of the present invention, the embodiments of the present invention will be further described in detail below in conjunction with the drawings and implementations.

[0061] In the integrated circuit manufacturing process under the advanced integrated circuit technology, there is a deviation between the geometric figures actually manufactured and the geometric figures in the layout data obtained by design, which directly affects the accuracy of extracting parasitic capacitance and may cause the performance of circuit optimization The result is inaccurate.

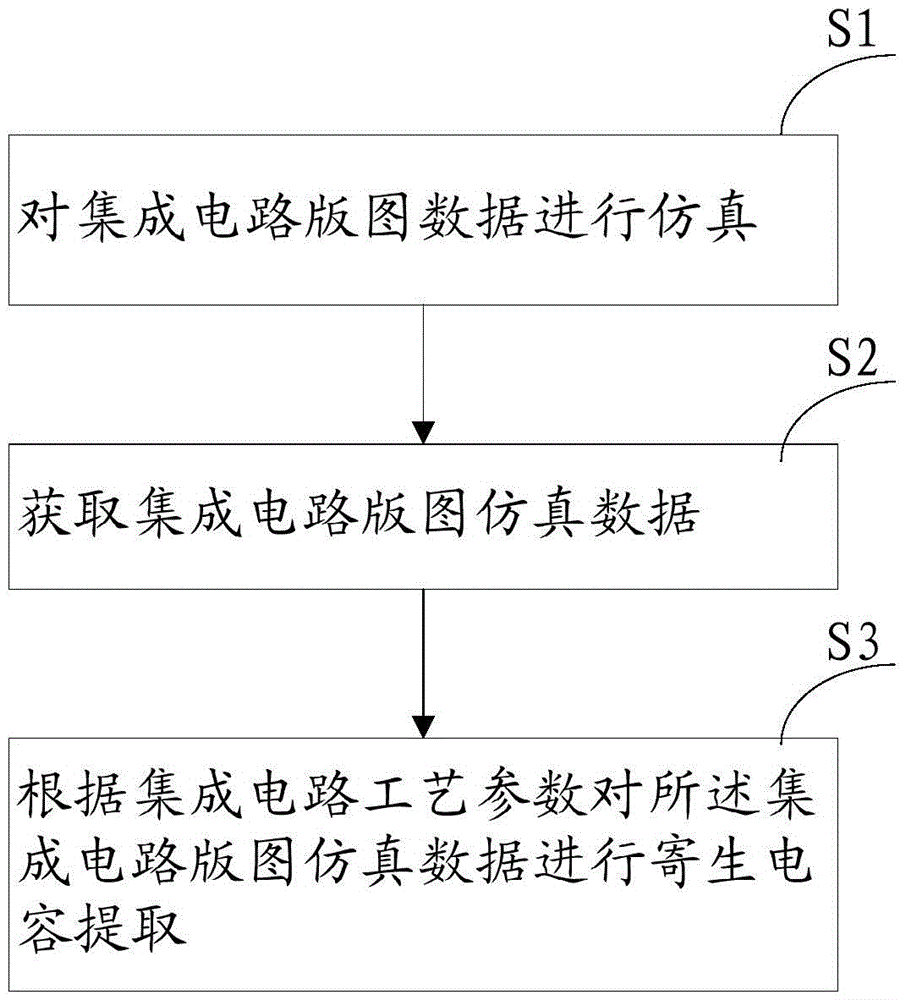

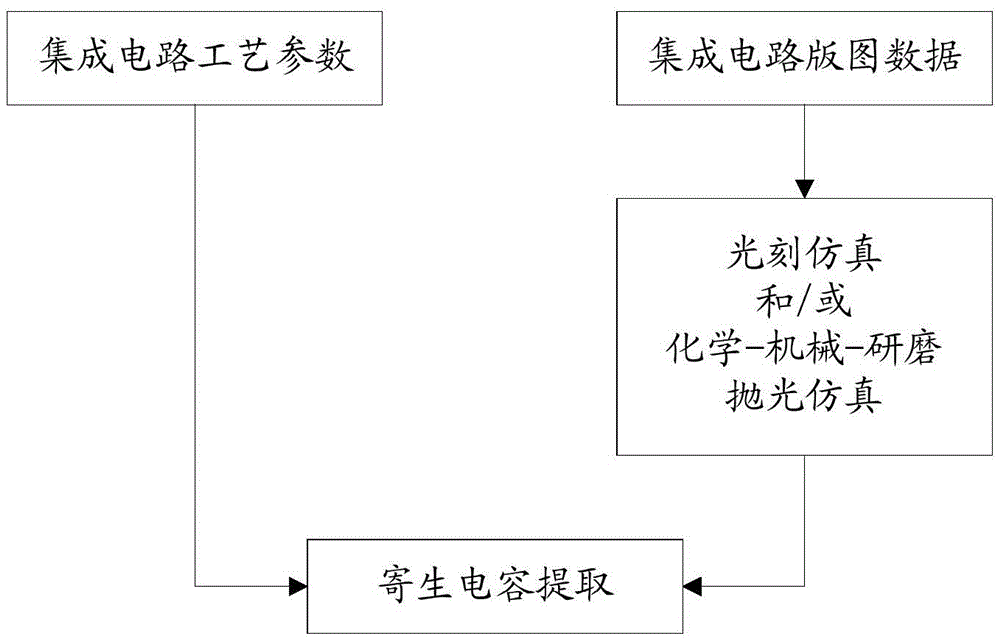

[0062] Such as figure 2 As shown, it is a flow chart of a method for extracting parasitic capacitance provided by the present invention. Include the following steps:

[0063] S1: Simulate the layout data of the integrated circuit;

[0064] S2: Acquiring integrated circuit layout simulation data;

[0065] S3: Perform p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More