Memory access methods, memory controllers and processor cores

A memory controller and processor core technology, applied in the information field, can solve problems such as bandwidth waste, poor real-time memory access scheduling, unpredictable memory access characteristics, etc., and achieve the effect of improving overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention. Obviously, the described embodiments are part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

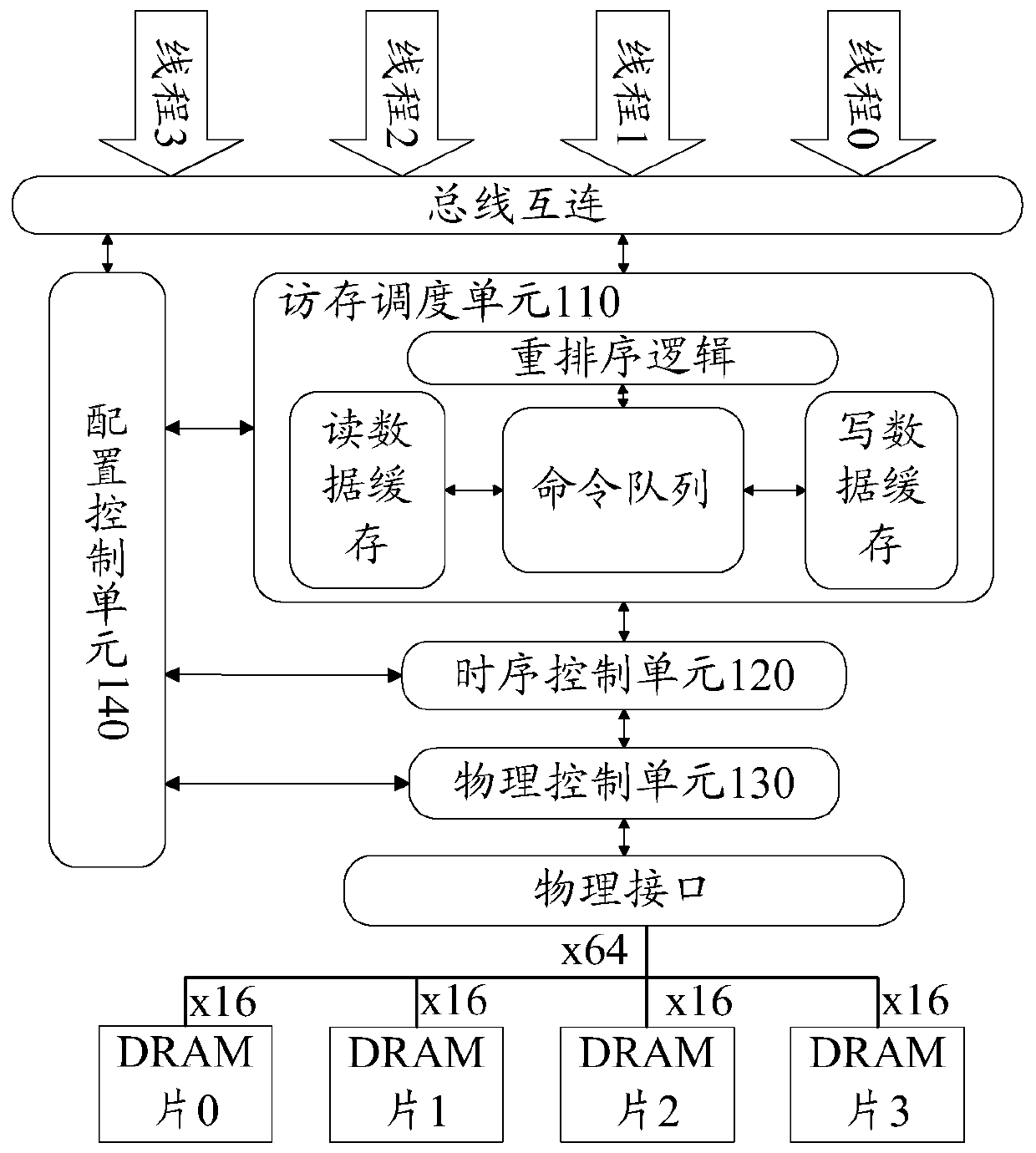

[0062] figure 1 It is a schematic diagram of the main structure of the memory controller. Such as figure 1 As shown, the memory controller mainly includes a memory access scheduling unit 110 , a timing control unit 120 , a physical control unit 130 and a configuration control unit 140 .

[0063] The memory access scheduling unit 110 schedules the memory access requests, and sends the processed address information and data to the timing control unit 120 .

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More