Multi-region power semiconductor devices

A region and gate region technology used in the field of power semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] As required, detailed embodiments of the present invention are disclosed herein; however, it is to be understood that the disclosed embodiments are merely exemplary of the invention, which may be embodied in various and alternative forms. The figures are not necessarily to scale; some features may be exaggerated or minimized to show details of particular components. Therefore, specific structural and functional details disclosed herein are not to be interpreted as limiting, but merely as a representative basis for teaching one skilled in the art to variously employ the present invention.

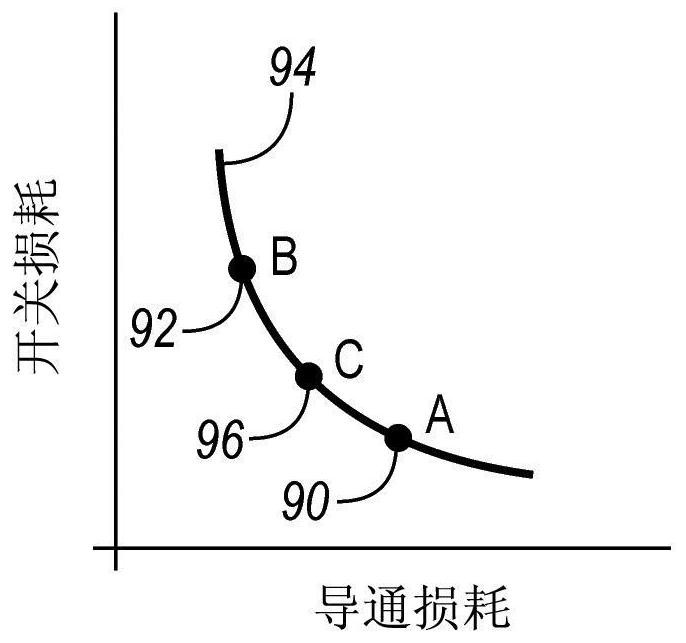

[0020] Power semiconductor devices (especially bipolar power semiconductor devices using minority carrier conduction) are designed according to the balance curve between conduction loss and switching loss. Products designed to enable high-frequency switching typically utilize relatively high on-state on-state voltages to optimize switching loss performance, and vice versa.

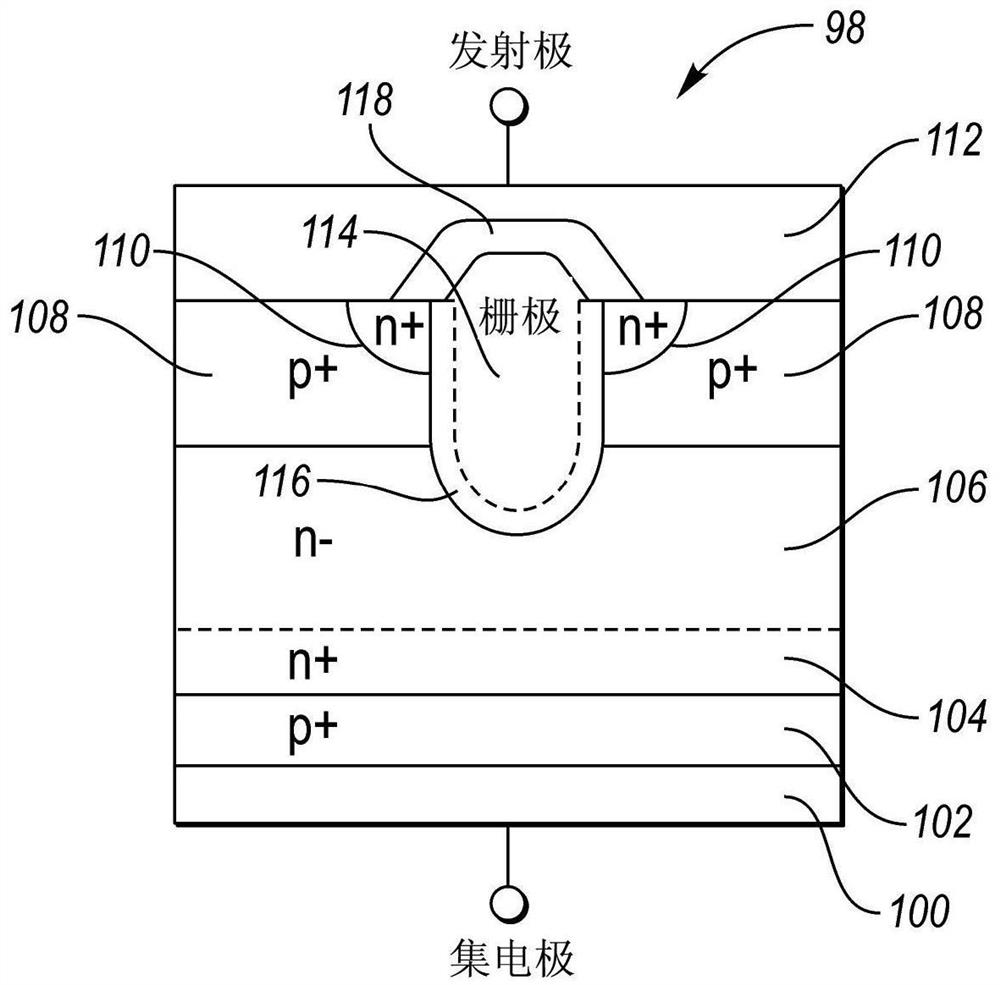

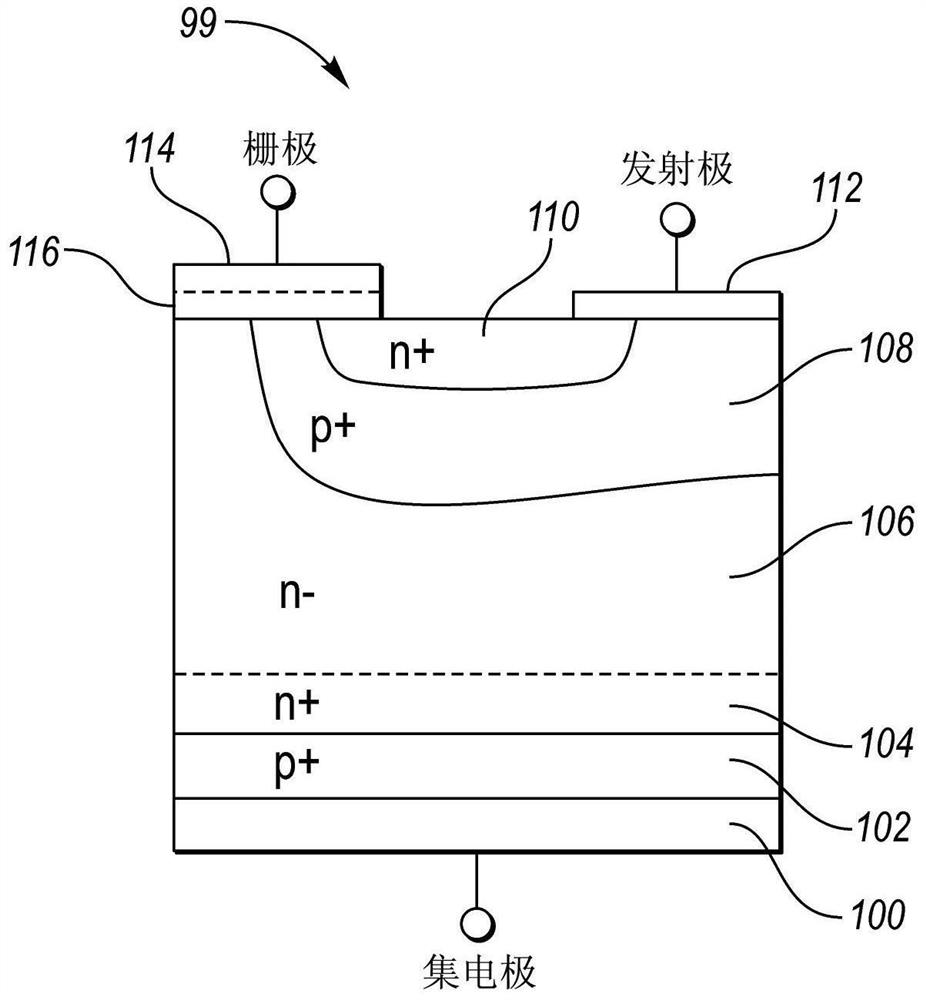

[0021] I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More