Neural network processor based on efficient multiplex data stream, and design method

A neural network and design method technology, applied in neural learning methods, electrical digital data processing, biological neural network models, etc., can solve the problems of slow operation speed, operation speed bottleneck, and occupation of resources, etc., to improve energy efficiency, reduce On-chip data bandwidth, the effect of improving data sharing rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

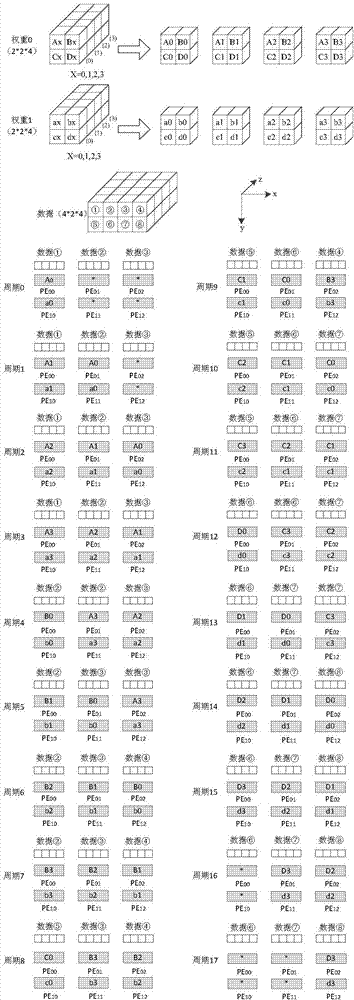

[0029] The purpose of the present invention is to provide a neural network processor and design method based on efficient multiplexing data streams. The processor adopts the time dimension-space dimension data stream and weight compression method in the existing neural network processor system, reducing the The on-chip data bandwidth is improved, the data sharing rate is improved, and invalid calculations are reduced, thereby improving the computing speed and operating energy efficiency of the neural network processor.

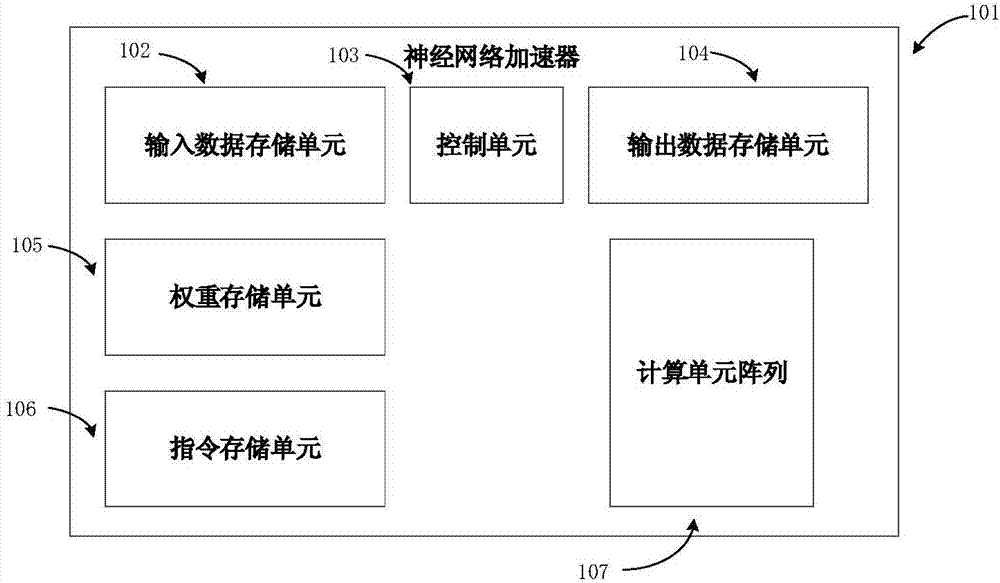

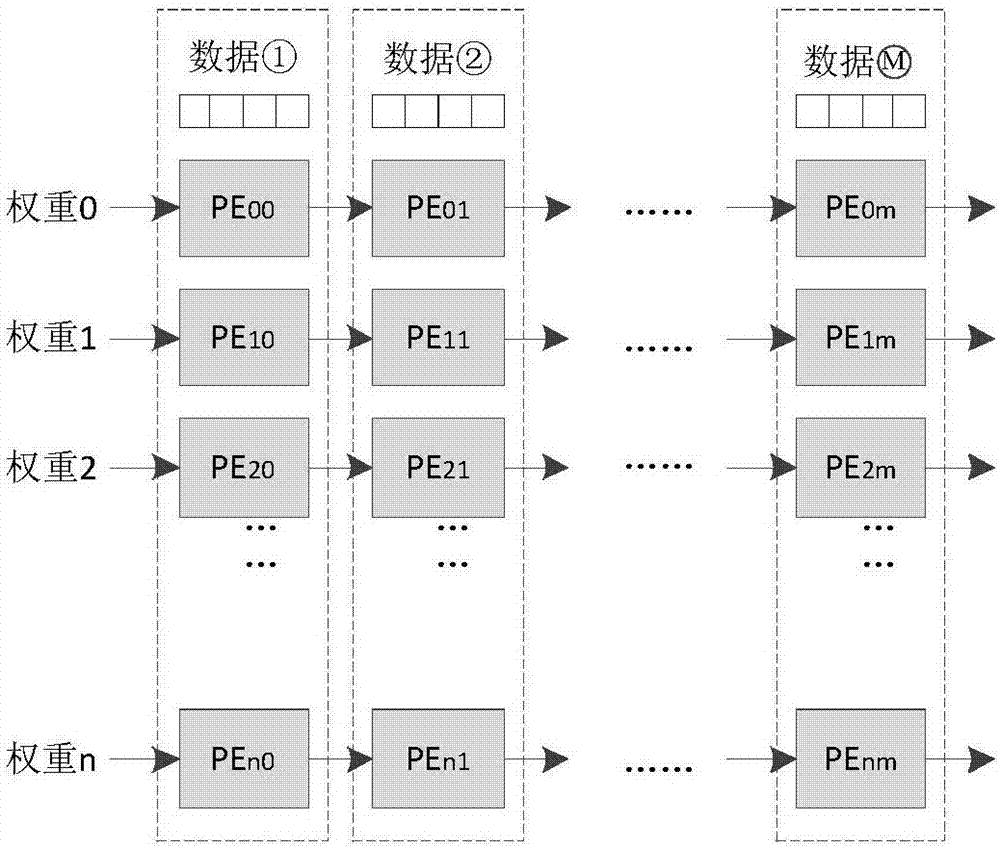

[0030] In order to achieve the above object, the neural network processor based on the efficient multiplexing data stream provided by the present invention includes:

[0031] At least one storage unit for storing operation instructions and operation data;

[0032] At least one calculation unit, used to perform neural network calculations; and a control unit, connected to the at least one storage unit and the at least one calculation unit, for obtaining the inf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More