Dynamically patched high-performance on-chip cache fault-tolerant architecture

An on-chip cache and high-performance technology, which is applied to the generation of response errors and non-redundancy-based fault handling, etc., can solve the problems of ineffective response to intermittent bit failures and untimely processing, so as to ensure performance and performance fluctuations Small, guaranteed stable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

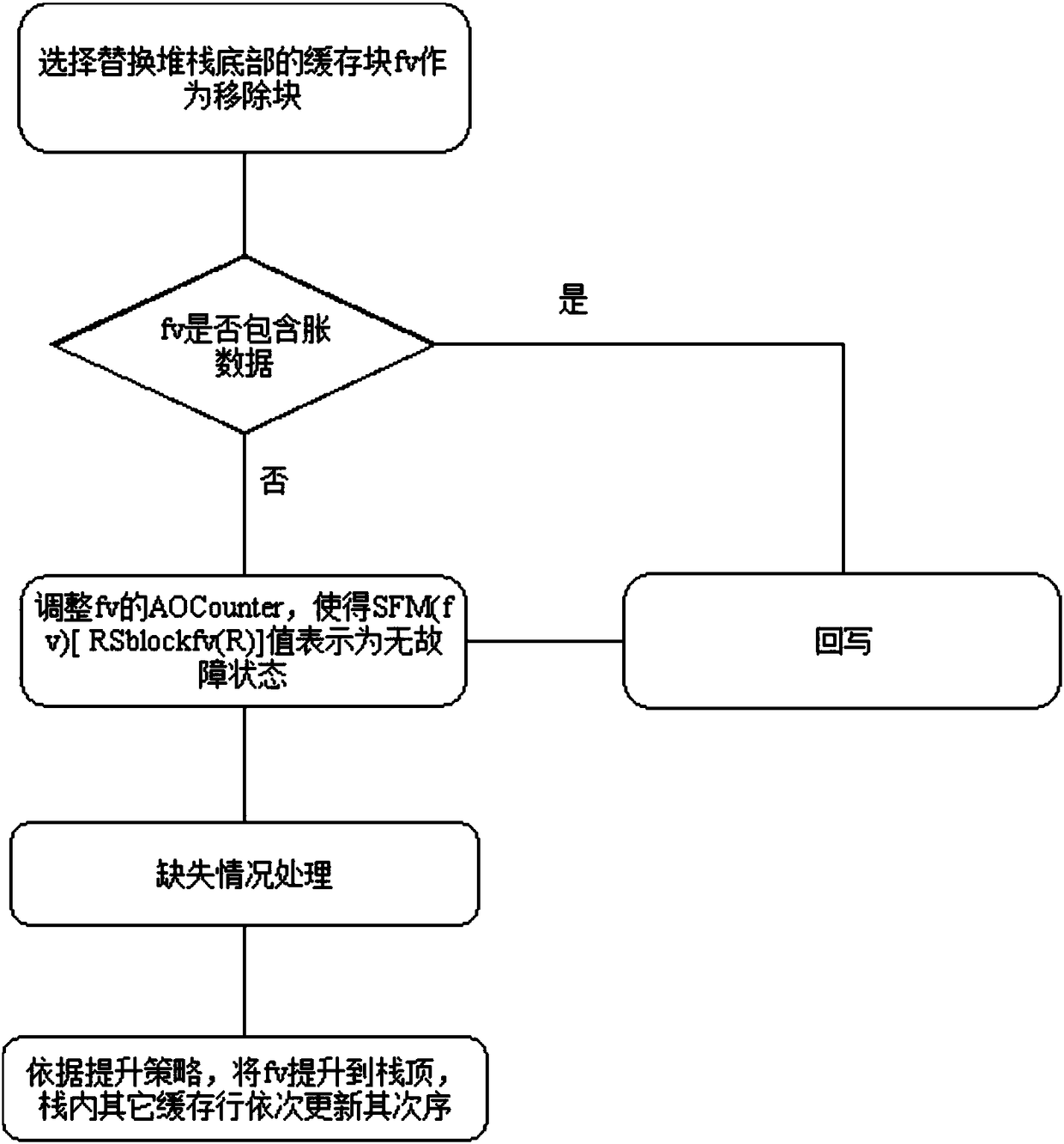

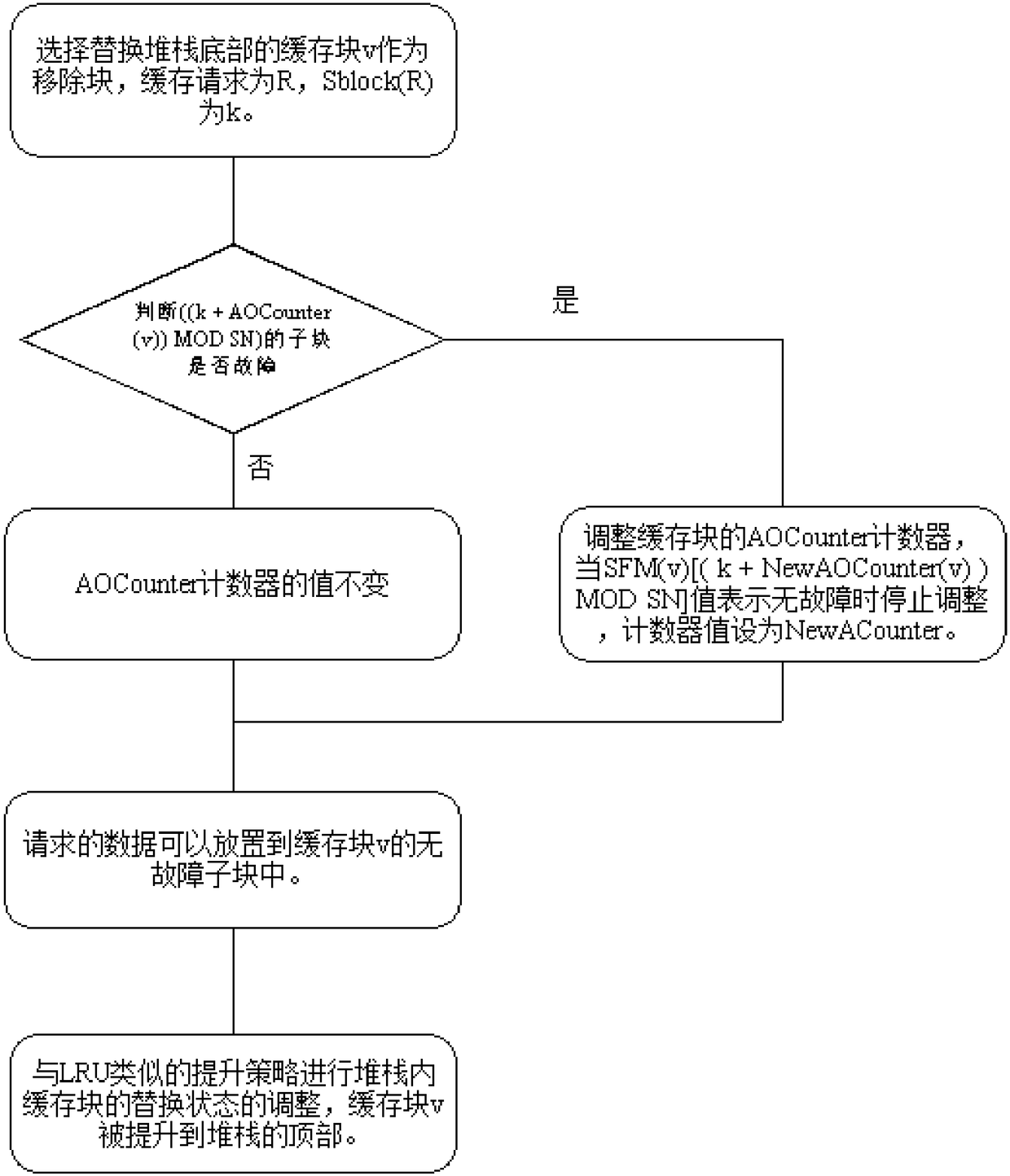

[0051] The following example specifically illustrates the sensitive mechanism algorithm:

[0052] Suppose an ordinary cache group with an associativity of 4 in the L1 cache, that is, a cache group contains four cache lines, the contents of the initial cache line, the reliability status identifier Line-Status of the cache line, and the corresponding counter values are as follows Figure 8 shown. Each cache line is composed of a tag part and a data part. The tag part includes a flag flag bit, a subblock fault bitmap field, a cache disabled field, a data modified field, a subblock offset adjustment field, and a pointer field to a repair array. , to replace the flag bit, the data part uses 8-byte continuous space as a sub-block, and a cache group contains 8 sub-blocks. The content of the initial cache line is that the 3rd and 5th sub-blocks of the first cache line are faulty, the 5th and 6th sub-blocks of the second cache line are faulty, the 3rd sub-block of the third cache li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More