A method for adjusting the threshold of a cmos device and a cmos device

A device and threshold technology, applied in semiconductor devices, electrical solid state devices, semiconductor/solid state device manufacturing, etc., can solve the problems affecting the uniformity of small-sized metal gate filling and threshold control effect, NMOS and PMOS related parasitic effects, PMOS metal gate To solve the problems of complex laminated structure, it can improve the effect of threshold control, improve filling uniformity, and improve the accuracy of threshold control.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The embodiment of the present application provides a method for adjusting the threshold of a CMOS device and a CMOS device, which solves the problem of complex threshold adjustment process of CMOS devices in the prior art, the associated parasitic influence between NMOS and PMOS, low threshold control accuracy, and PMOS metal The gate stack structure is complex, which affects the filling uniformity and threshold control effect of small-sized metal gates.

[0040] The technical solution of the embodiment of the present application is to solve the above-mentioned technical problems, and the general idea is as follows:

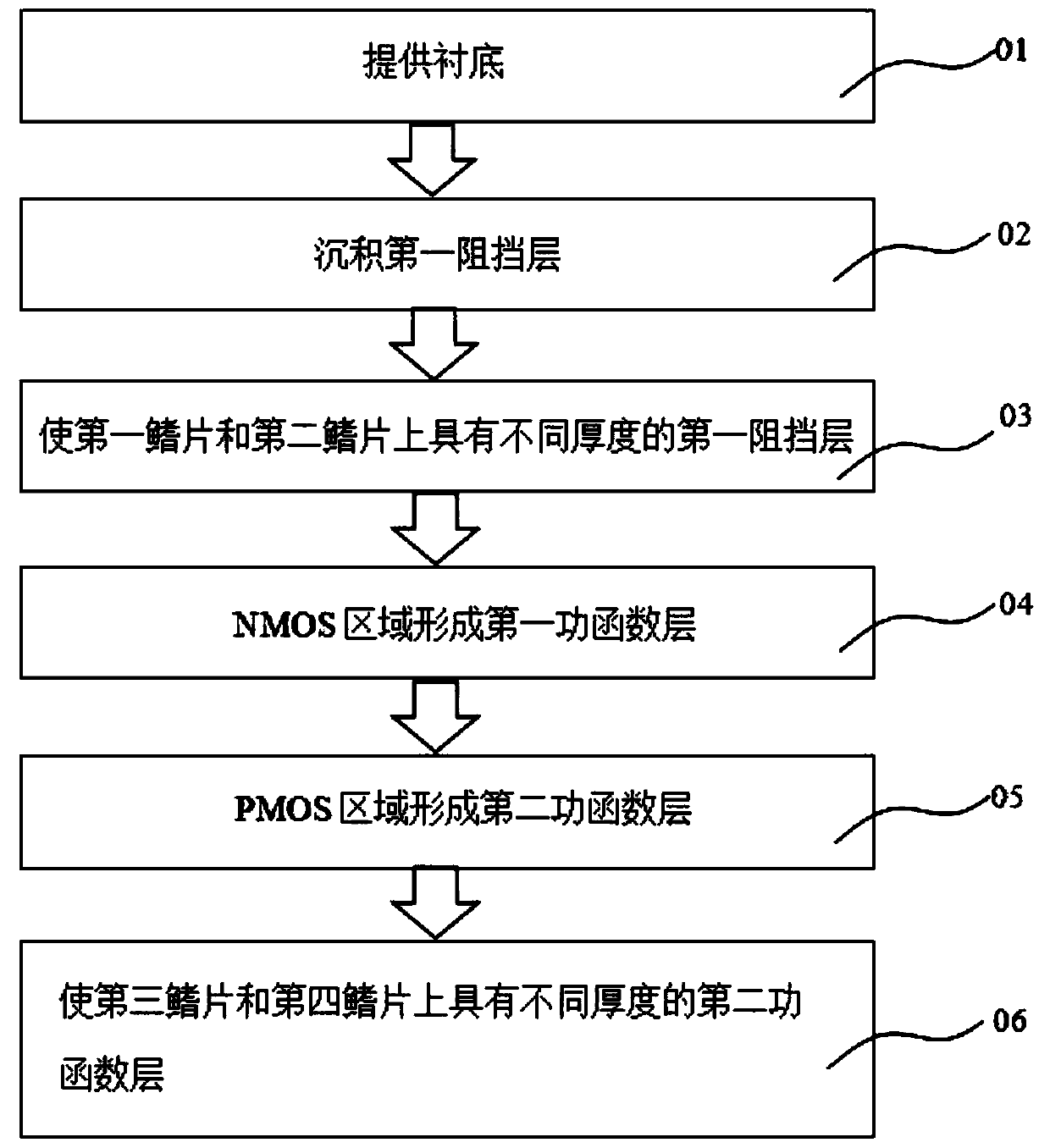

[0041] A method of adjusting the threshold of a CMOS device, comprising:

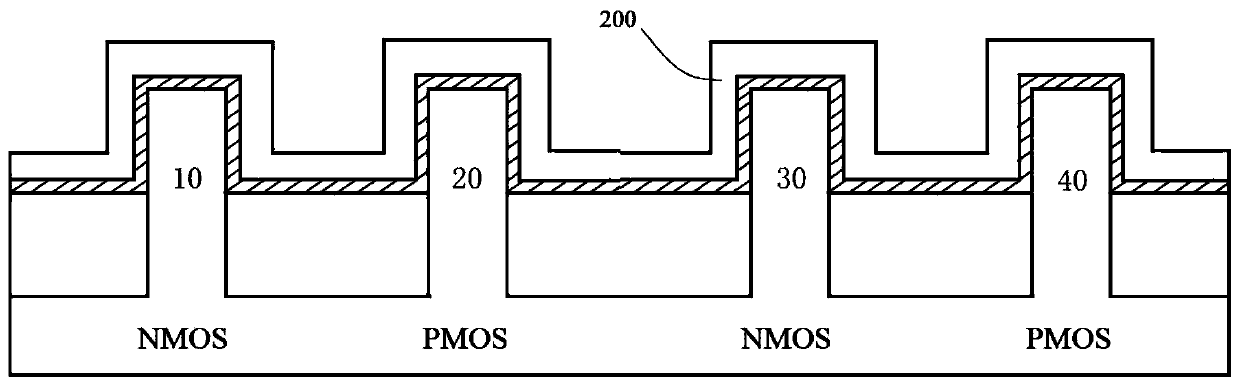

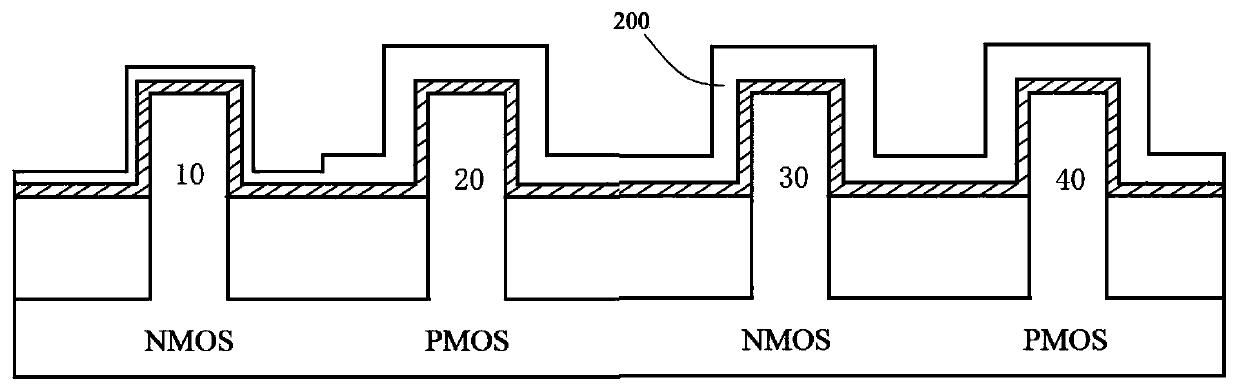

[0042] providing a substrate, the substrate including an NMOS area and a PMOS area, the NMOS area includes a first fin and a second fin, and the PMOS area includes a third fin and a fourth fin;

[0043] depositing a first barrier layer;

[0044] performing local processing on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More