Display panel and display device

A display panel and substrate technology, which is applied in the direction of instruments, semiconductor devices, electrical components, etc., can solve the problems of being susceptible to corrosion, abnormal display of the display panel, interruption of display panel working signal transmission, etc., to achieve good isolation effect and prevent poor display Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

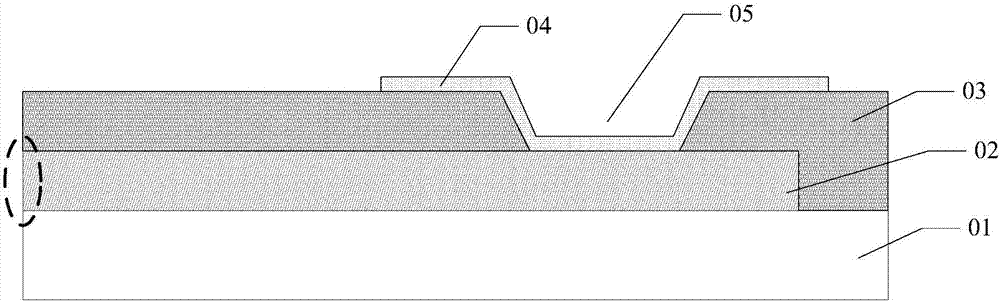

[0032] see Figure 4 The display panel provided by Embodiment 1 of the present application includes: a substrate 1, at least one signal lead-out line 2 arranged on the substrate 1, one end of the signal lead-out line 2 is exposed (such as Figure 4 shown in the dotted line box), and there is a disconnection on the signal lead-out line 2, the disconnection is connected through the heavily doped polysilicon 3, and the heavily doped polysilicon 3 is arranged between the substrate 1 and the signal lead-out line 2, and the signal lead-out A second insulating layer 4 is provided on the wire 2 , and a bonding PAD5 is provided on the second insulating layer 4 . The bonding PAD5 is connected to the non-exposed portion of the signal lead-out wire 2 through the second via hole 6 on the second insulating layer 4 . Preferably, the second insulating layer 4 has been planarized.

[0033] Since the signal lead-out line 2 is provided with a disconnection, the disconnection is connected throug...

Embodiment 2

[0045]The display panel provided in Embodiment 2 of the present application is similar to the display panel provided in Embodiment 1 of the present application, and the same parts will not be repeated here, and only the different parts will be described below.

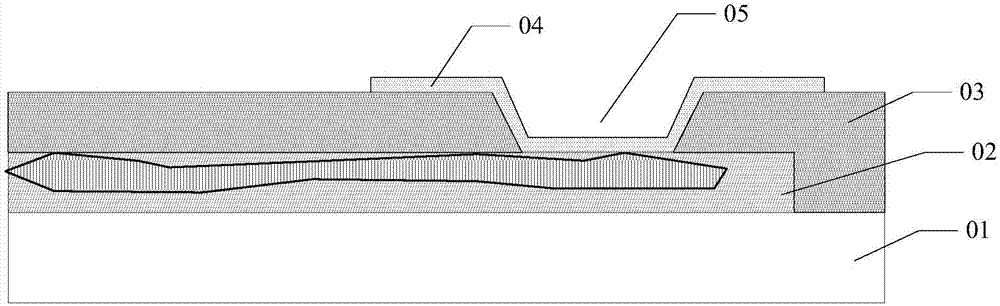

[0046] see Figure 5 , in the display panel provided in Embodiment 2 of the present application, the heavily doped polysilicon 3 is disposed above the signal lead-out lines 2 .

[0047] Since the heavily doped polysilicon 3 is not adjacent to the substrate 1, the buffer layer 9 may not be provided in the display panel.

Embodiment 3

[0049] The display panel provided in the third embodiment of the present application is similar to the display panel provided in the first embodiment of the present application, and the same parts will not be repeated here, and only the different parts will be described below.

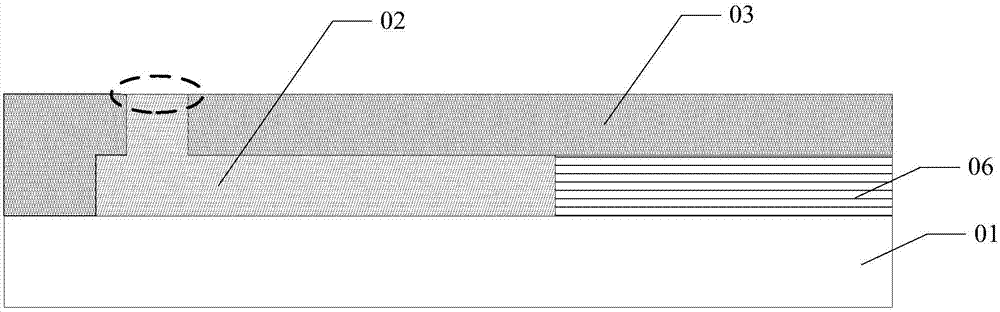

[0050] see Figure 6 , in the display panel provided in Embodiment 3 of the present application, the heavily doped polysilicon 3 is arranged in the same layer as the signal lead-out line 2, that is, the heavily-doped polysilicon 3 is arranged in the opening of the signal lead-out line 2 and connected to the signal lead-out line 2 Disconnected two-part connection.

[0051] Since the heavily doped polysilicon 3 and the signal lead-out lines 2 are arranged in the same layer, the first insulating layer 7 may not be provided in the display panel.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More