Pixel circuit, driving method of pixel circuit, display panel and display device

A technology for pixel circuits and driving transistors, applied in the fields of pixel circuits, display panels and display devices, can solve problems such as image sticking, threshold voltage shift, etc., and achieve the effect of restoring threshold voltage shift and avoiding sticking phenomenon.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

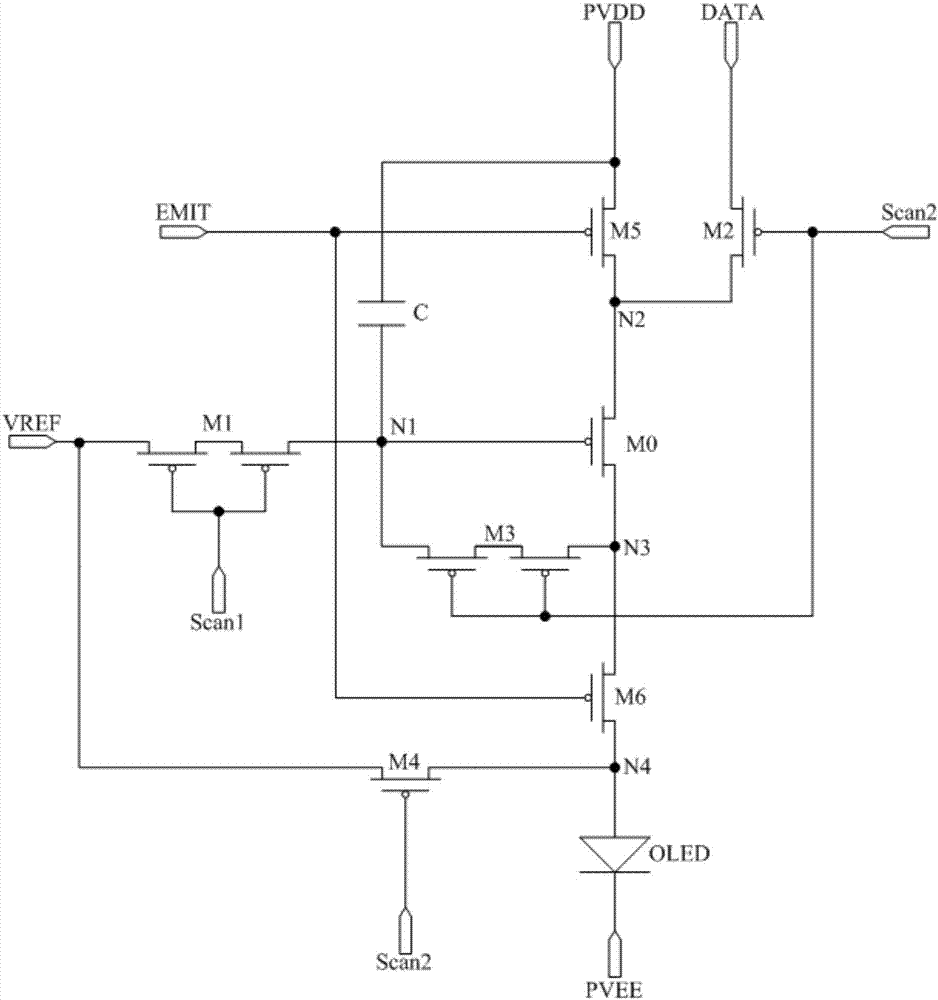

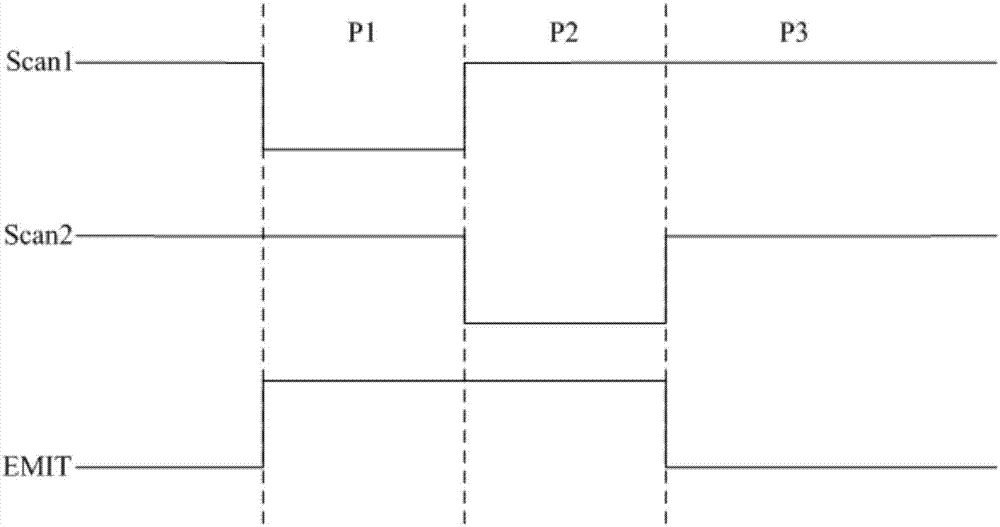

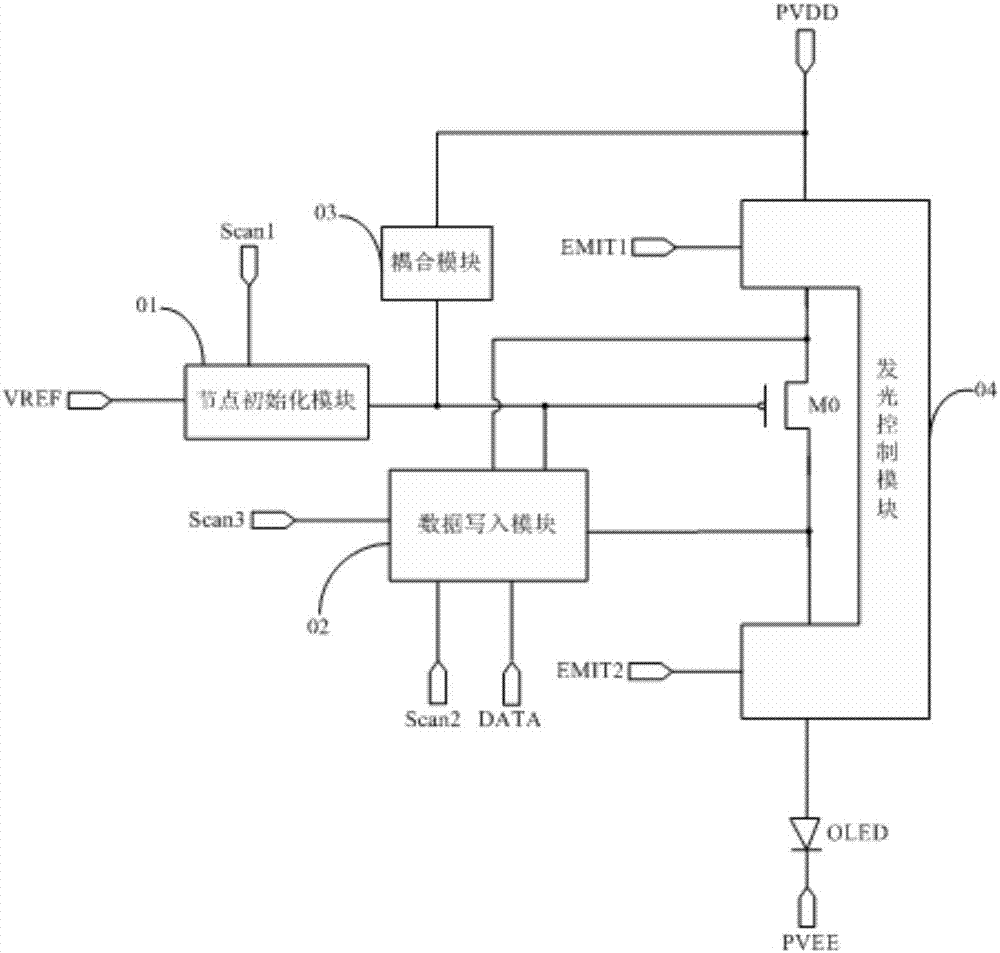

[0075] by Figure 4 Take the pixel circuit shown as an example, and the corresponding input and output timings are as follows Figure 8a shown. Specifically, choose the Figure 8a The three stages of T1, T2, and T3 in the input timing diagram shown.

[0076] In node initialization phase T1, Scan1=0, Scan2=1, Scan3=0, EMIT1=1, EMIT2=0.

[0077] Since Scan1=0, the first switching transistor M1 is turned on to provide the reference signal of the reference signal terminal VREF to the gate of the driving transistor M0, and the potential of the gate of the driving transistor M0 is VREF. Since Scan3=0, the third switching transistor M3 is turned on to provide the reference signal received by the gate of the driving transistor M0 to the second pole of the driving transistor M0, the potential of the second pole of the driving transistor M0 is VREF, and the driving transistor M0 The gate of M0 and the second pole of the driving transistor M0 are initialized and reset. Since EMIT2=0...

example 2

[0086] by Figure 5 Take the pixel circuit shown as an example, and the corresponding input and output timings are as follows Figure 9a shown. Specifically, choose the Figure 9a The three stages of T1, T2, and T3 in the input timing diagram shown.

[0087] In node initialization phase T1, Scan1=0, Scan2=1, EMIT1=1, EMIT2=0.

[0088] Since Scan1=0, the first switching transistor M1 is turned on to provide the reference signal of the reference signal terminal VREF to the gate of the driving transistor M0, and the potential of the gate of the driving transistor M0 is VREF. Since EMIT1=1, the third switching transistor M3 is turned on to provide the reference signal received by the gate of the driving transistor M0 to the second pole of the driving transistor M0, the potential of the second pole of the driving transistor M0 is VREF, and the driving transistor M0 The gate of M0 and the second pole of the driving transistor M0 are initialized and reset. Since EMIT2=0, the fif...

example 3

[0097] by Image 6 Take the pixel circuit shown as an example, and the corresponding input and output timings are as follows Figure 10a shown. Specifically, choose the Figure 10a The three stages of T1, T2, and T3 in the input timing diagram shown.

[0098] In node initialization phase T1, Scan1=1, Scan2=0, EMIT1=0, EMIT2=1.

[0099] Since Scan1=1, the first switching transistor M1 is turned on to provide the reference signal of the reference signal terminal VREF to the gate of the driving transistor M0, and the potential of the gate of the driving transistor M0 is VREF. Since EMIT1=0, the third switching transistor M3 is turned on to provide the reference signal received by the gate of the driving transistor M0 to the second pole of the driving transistor M0, the potential of the second pole of the driving transistor M0 is VREF, and the driving transistor M0 The gate of M0 and the second pole of the driving transistor M0 are initialized and reset. Since EMIT2=1, the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More