Chip fan-out packaging structure, multi-chip integrated module and wafer-level packaging method

A packaging structure and chip technology, which is applied in the direction of antenna support/mounting device, circuit, electric solid device, etc., can solve the problems of difficult ground connection of conductive layer, continuity of difficult conductive layer, rough surface, etc., and achieves low cost and low production cost The effect of cost reduction and simple production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to understand the technical content of the present invention more clearly, the following examples are given in detail, the purpose of which is only to better understand the content of the present invention but not to limit the protection scope of the present invention. The components in the structures in the drawings of the embodiments are not scaled according to the normal scale, so they do not represent the actual relative sizes of the structures in the embodiments.

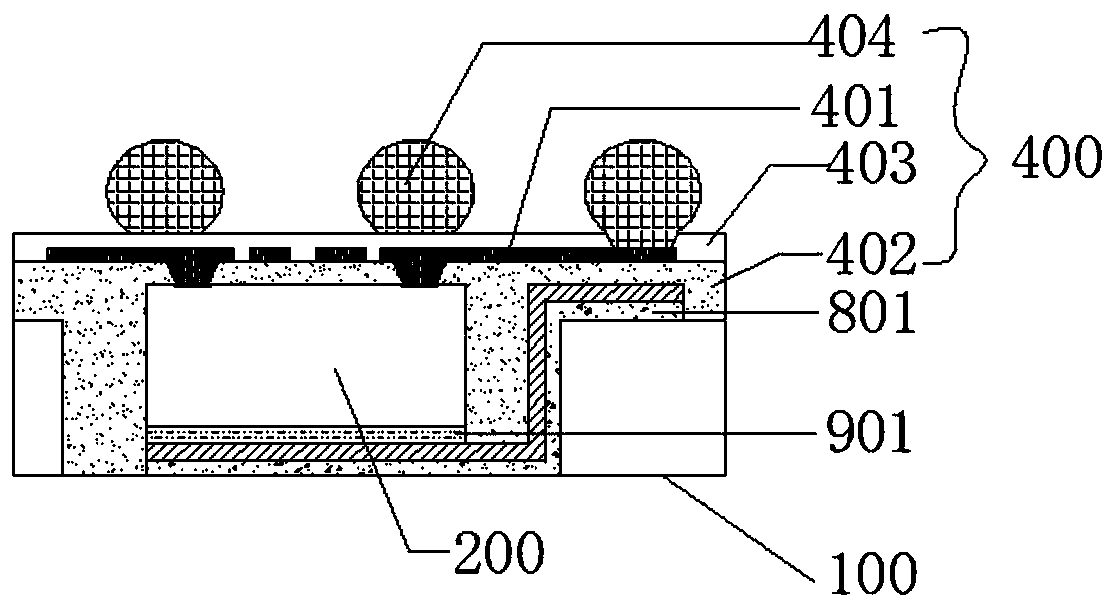

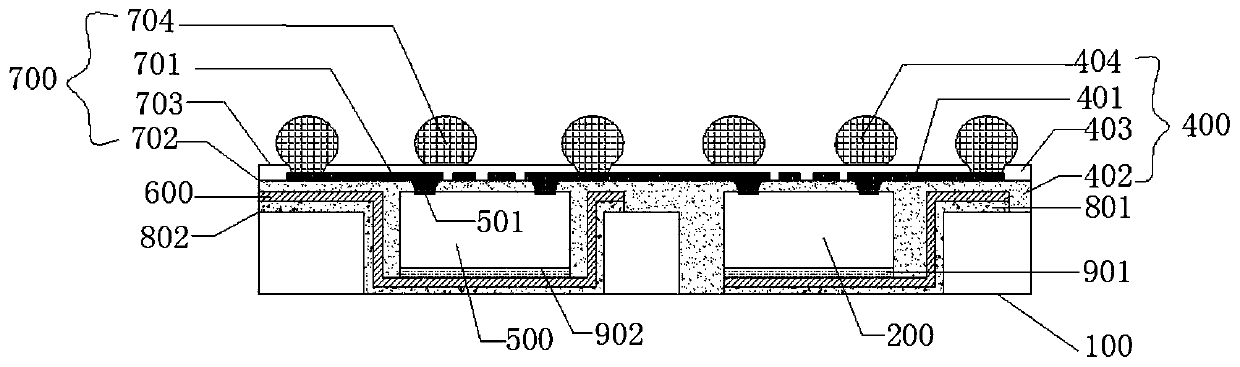

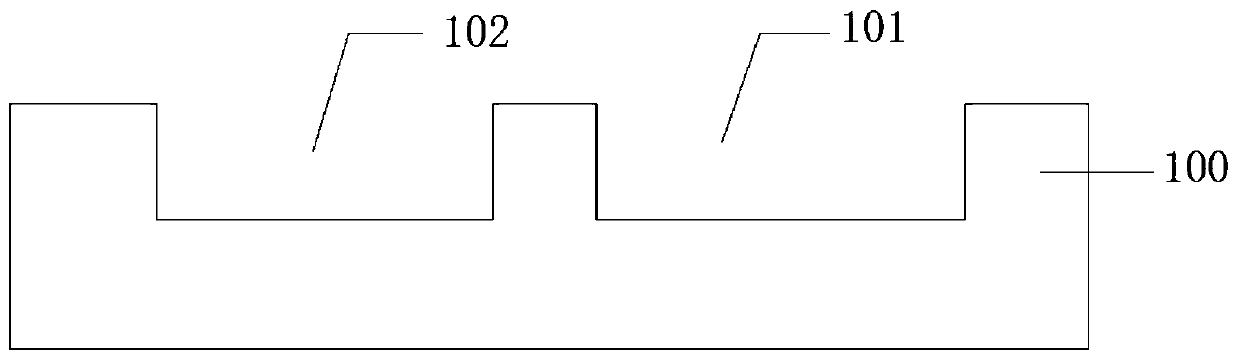

[0042] Such as figure 1 As shown, a chip fan-out packaging structure with an integrated antenna includes a carrier board 100 and at least one radio frequency chip 200 including a radio frequency signal receiving or / and transmitting function, and the carrier board has a first surface and a second surface opposite to it. On the surface, the carrier board has a first groove 101 for accommodating the radio frequency chip, and the bonding pad of the radio frequency chip is buried in the first groove ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More