Method and apparatus for processing hard memory error

A method for handling hard errors and a technology for hard errors, applied in the field of communications, can solve problems such as hard memory errors and inability to correct hard errors in memory, and achieve the effect of improving stability and avoiding program errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

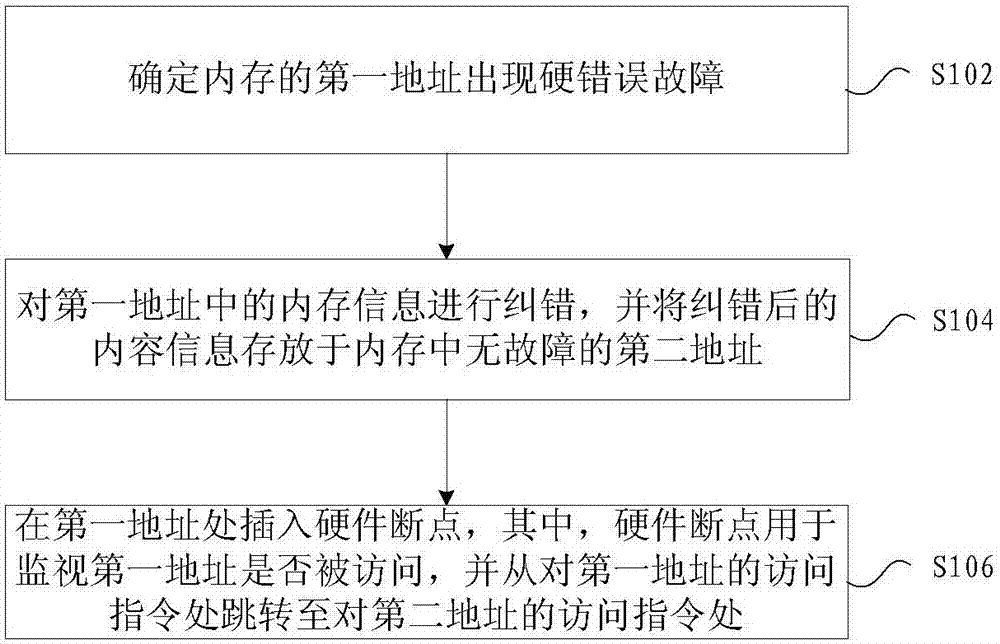

[0030] In this embodiment, a method for processing memory hard errors is provided, figure 1 is a flow chart of a method for processing memory hard errors according to an embodiment of the present invention, such as figure 1 As shown, the process includes the following steps:

[0031] Step S102, determining that a hard error occurs at the first address of the memory;

[0032] Step S104, performing error correction on the memory information in the first address, and storing the error-corrected memory information in a second address in the memory without fault;

[0033] Step S106, inserting a hardware breakpoint at the first address, wherein the hardware breakpoint is used to monitor whether the first address is accessed, and jump from an access instruction to the first address to an access instruction to the second address.

[0034]Through the above steps, firstly, it is determined that a hard error has occurred in the first address of the memory, and then the memory informati...

Embodiment 2

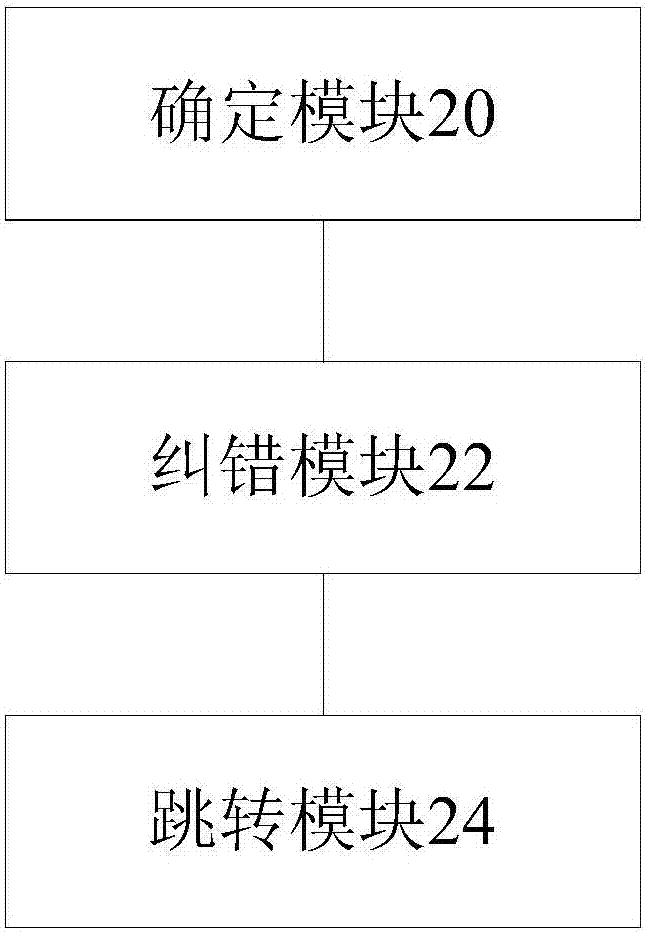

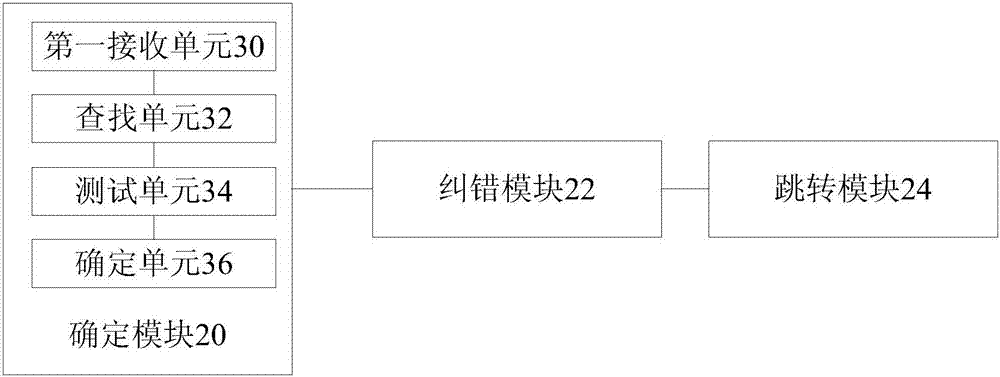

[0055] This embodiment also provides a memory hard error processing device, which is used to implement the above embodiments and preferred implementation modes, and what has already been described will not be repeated. As used below, the term "module" may be a combination of software and / or hardware that realizes a predetermined function. Although the devices described in the following embodiments are preferably implemented in software, implementations in hardware, or a combination of software and hardware are also possible and contemplated.

[0056] figure 2 is a structural block diagram of a memory hard error processing device according to an embodiment of the present invention, such as figure 2 As shown, the device includes:

[0057] A determining module 20, configured to determine that a hard error fault occurs at the first address of the memory;

[0058] The error correction module 22 is used to correct the memory information in the first address, and store the corre...

Embodiment 3

[0072] This embodiment relates to a method for ensuring the normal operation of the system under the premise of ensuring that the system does not restart when unrecoverable hardware damage occurs in the storage unit in the memory particle in the embedded system.

[0073] This embodiment provides a method and device: when an uncorrectable hard error occurs in the memory of the embedded system, the system can continue to operate normally without restarting the system, which can significantly improve the market application of data communication products. stability.

[0074]In the embedded CPU architecture of the related technology, the memory controller supports ECC verification and error correction capabilities. As long as the memory we use also supports the ECC verification function, an ECC interrupt can be reported to the CPU when an error occurs in the memory. After an ECC error occurs, the error address is given in the ECC error capture address register. At this time, the o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More