Test system for DSP (digital signal processing) unit in field programmable gate array chip

A test system and gate array technology, applied in the direction of test/monitoring control system, general control system, electrical test/monitoring, etc., can solve the problems of normal DSP unit function, abnormal function of test result display, poor accuracy, etc., and achieve accurate function The effect of the test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

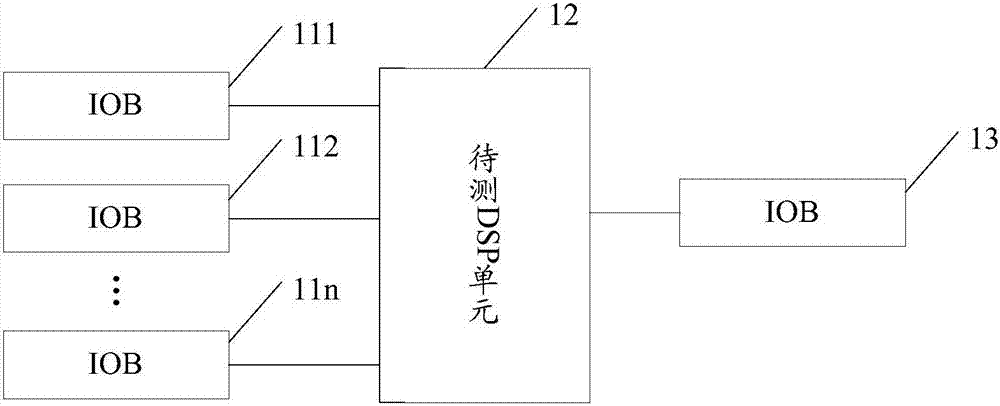

[0023] figure 1 It is a schematic diagram of a testing system of a DSP unit in an existing FPGA chip. Such as figure 1 As shown, the input and output units (IOBs) 111-11n in the FPGA chip are connected to the DSP unit 12 to be tested through interconnection resources in the FPGA chip. The excitation data are respectively input to the DSP unit 12 to be tested by the IOB111-11n, and the DSP unit 12 to be tested performs corresponding operations on the excitation data, and then outputs the operation result data through the IOB13. The user can judge whether the function of the DSP unit 12 under test is normal by comparing the output calculation result data with the expected data, that is, whether the DSP unit 12 under test is working normally.

[0024] In the above test system, multiple IOBs need to be used, and each IOB is connected to the DSP unit 12 to be tested through different interconnection resources. Due to the different delays of different interconnection resources, d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More