Virtext5 device-based bit stream file analysis method and timed refreshing method

A file analysis and device technology, applied in the direction of instruments, static memory, digital memory information, etc., can solve the problem that the size of BRAM resources cannot be known, achieve broad market application prospects, realize dynamic refresh, and improve system reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

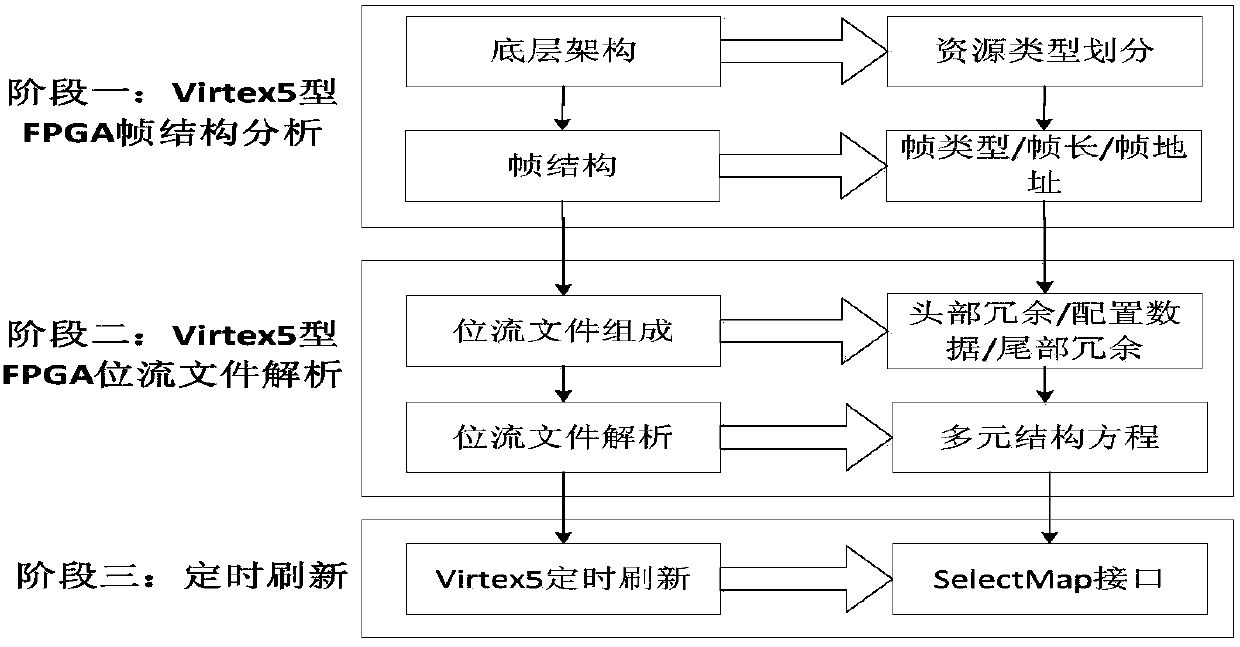

[0040] Attached below figure 1 And examples illustrate the present invention in detail. The present invention relates to a kind of bit stream file parsing method based on Virtex5 device, and the steps are as follows:

[0041] (1) Analyze the underlying architecture of at least 8 series of devices of the Virtex5 type, and determine the resource type of each series of devices;

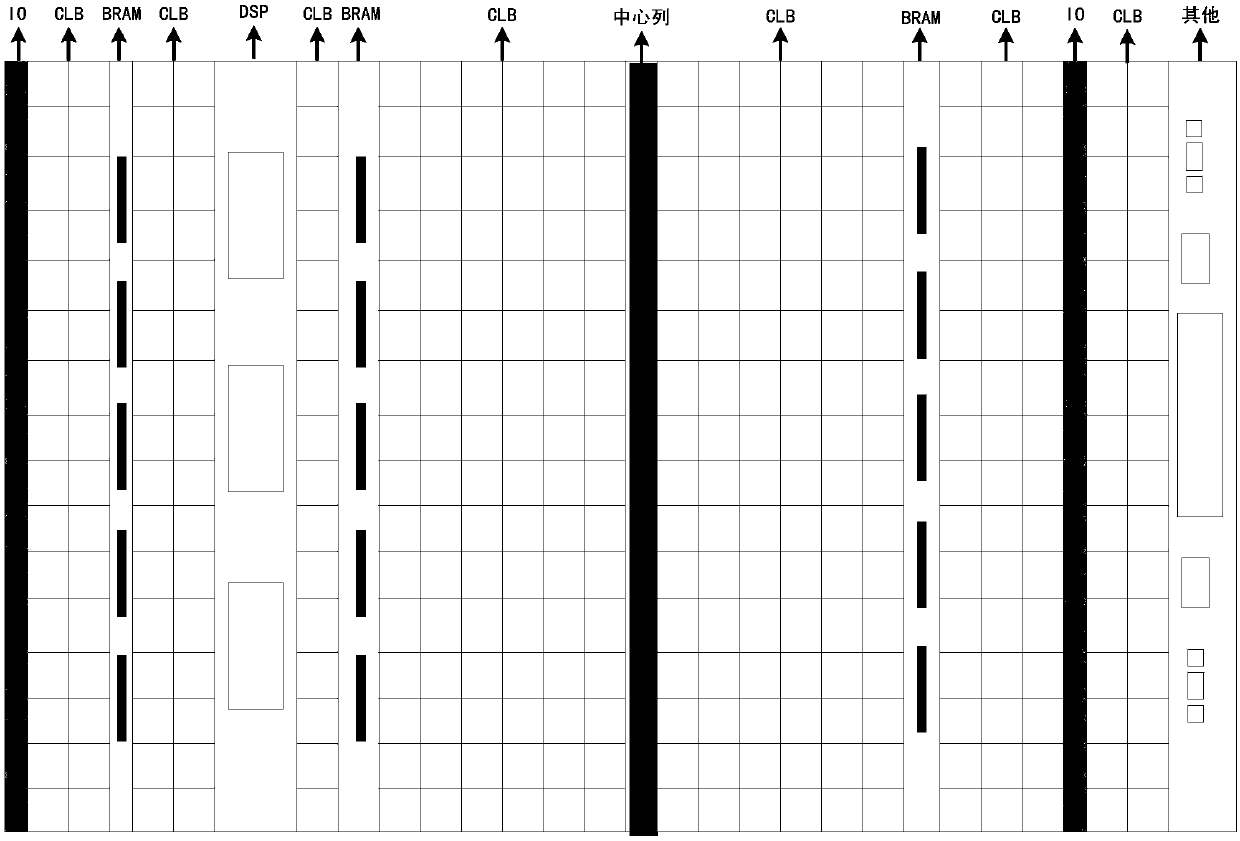

[0042] Analysis of the underlying architecture: Since the configuration memory is invisible to the user, it is necessary to study the configuration framework and configuration file structure of the SRAM FPGA to understand the configuration file of the FPGA. figure 2 According to FPGA EDIT, the resource type and organizational structure of Virtex5 are extracted. This figure describes the internal organizational structure of the Virtex5 FPGA, including the internal composition of various resource types (such as CLB, DSP, BRAM, etc.) in the FPGA. Different layout shapes in the underlying architecture rep...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More