Register generating method device for chip verification

A technology for generating devices and registers, used in instruments, special data processing applications, electrical digital data processing, etc., and can solve the problem of only being widely supported

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be described in detail below in conjunction with various embodiments shown in the drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

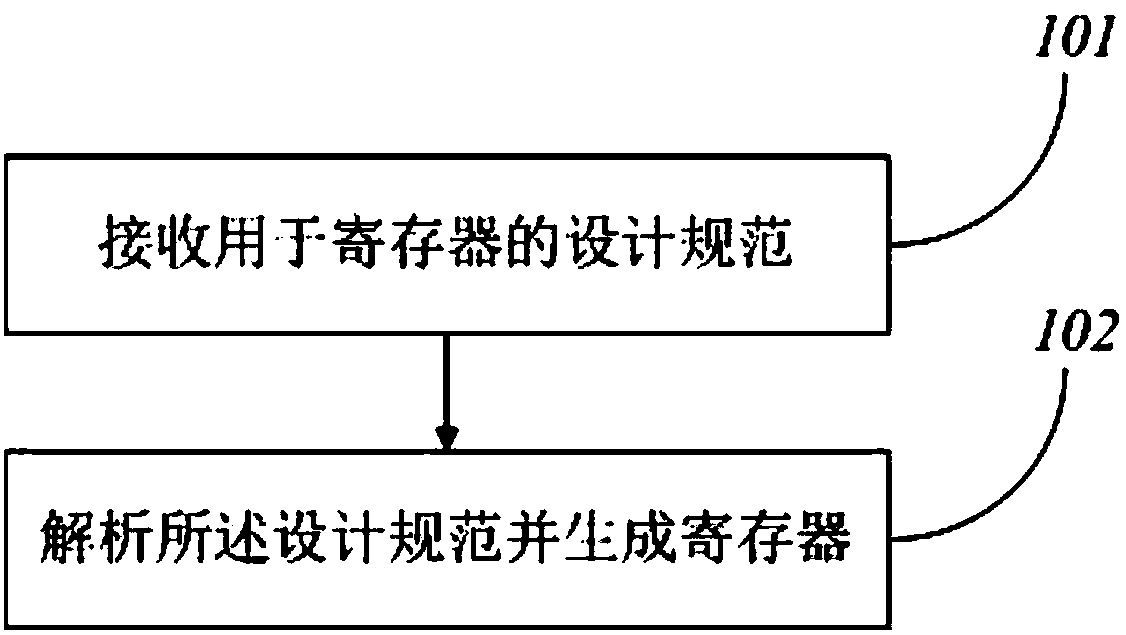

[0018] An embodiment of the present invention provides a register generation method for chip verification, such as figure 1 shown, including the following steps:

[0019] Step 101: receiving design specifications for registers;

[0020] Step 102: Parse the design specification and generate registers.

[0021] Preferably, said generating registers includes: generating registers conforming to SystemVerilog specifications.

[0022] Preferably, the following steps are also included: compiling the register;

[0023] Preferably, the following steps are also included: start the simulation, call the model initialization...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com