A Calibration Method of Hierarchical TDC Using Delay Chain Structure

A correction method and delay chain technology, applied in the field of time-to-digital conversion, can solve problems such as uncertain position relationship of rising edge of external input signal, DFF error output code, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

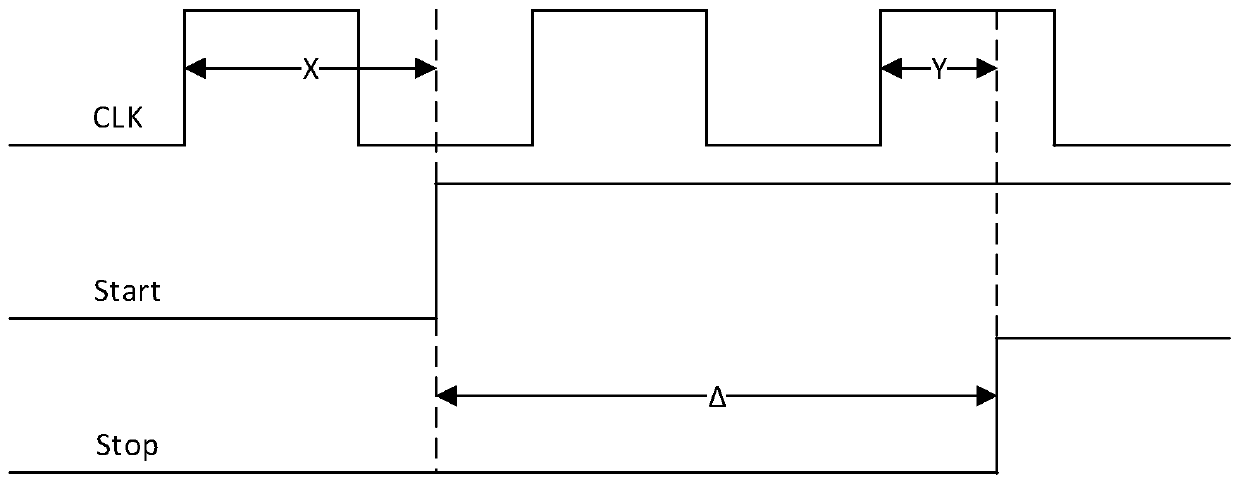

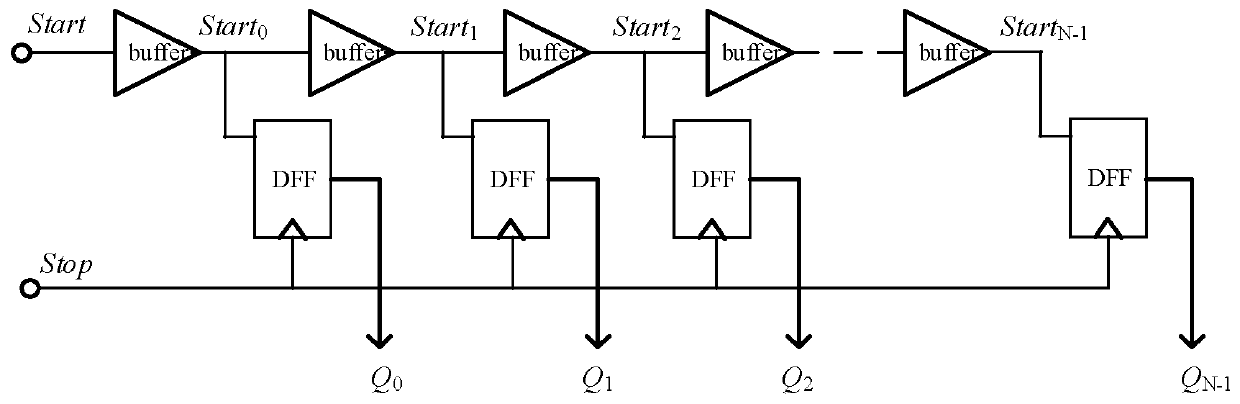

[0027] Specific implementation mode one: refer to figure 1 Specifically describe this embodiment, a correction method for a hierarchical TDC using a delay chain structure described in this embodiment,

[0028] When the start signal Start arrives, the reference clock counter counts the reference clock CLK, and at the same time, the start signal Start is sent to the delay chain, and the time interval X between the start signal Start and the reference clock CLK is obtained, 0≤X≤T, where T represents The time of one cycle of the reference clock CLK,

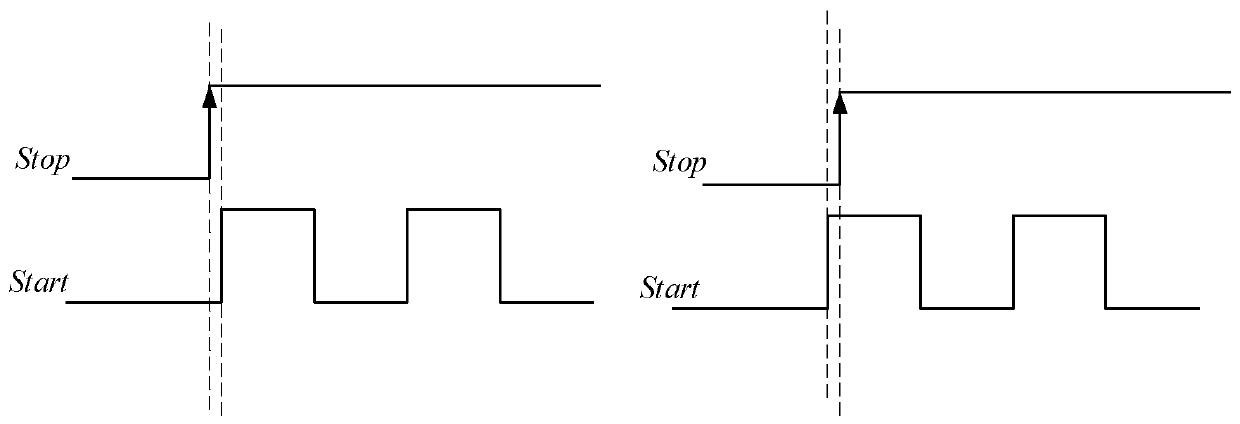

[0029] When the stop signal Stop arrives, the reference clock counter stops counting and obtains the number of reference clock cycles N between the start signal Start and the stop signal Stop. At the same time, the stop signal Stop is sent into the delay chain, and the stop signal Stop and the reference clock CLK are obtained. The time interval Y, 0≤Y≤T.

[0030] Correct the reference clock cycle number N,

[0031] Suppose the in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More