Channel simulator based on FPGA (Field Programmable Gate Array) and simulation method thereof

A channel simulation and analog signal technology, which is applied in transmission monitoring, electrical components, transmission systems, etc., can solve problems such as hardware resource consumption in analog channel scenarios and 4G communication system simulation requirements, and achieve a clear and reasonable overall design structure , high reliability effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

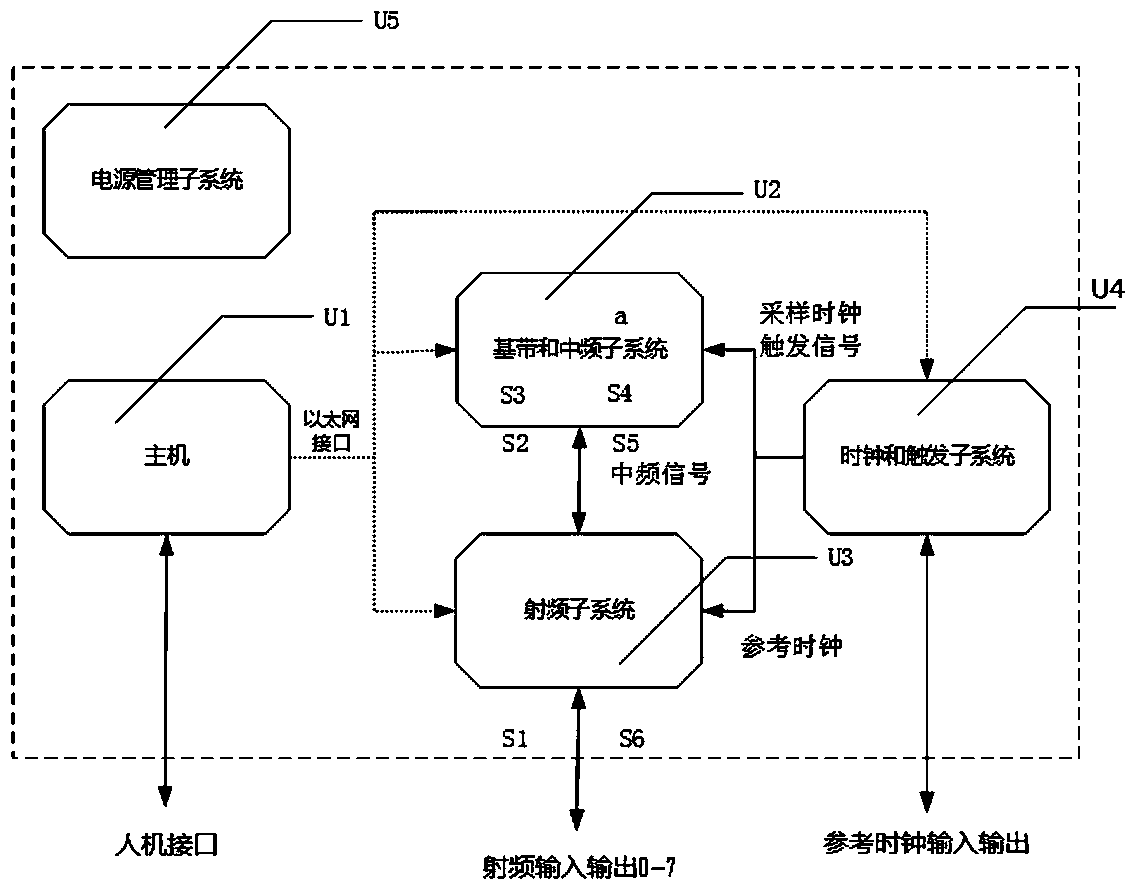

[0029] refer to figure 1 A channel emulator based on FPGA of the present invention includes host U1, baseband and intermediate frequency subsystem U2, radio frequency subsystem U3, clock and trigger subsystem U4, and power management subsystem U5; host U1 respectively through different Ethernet interfaces It is connected with baseband and intermediate frequency subsystem U2, radio frequency subsystem U3, clock and trigger subsystem U4; clock and trigger subsystem U4 is also connected with baseband and intermediate frequency subsystem U2, radio frequency subsystem U3; baseband and intermediate frequency subsystem U2 is connected with radio frequency The subsystem U3 is connected; the host U1, baseband and intermediate frequency subsystem U2, radio frequency subsystem U3, clock and trigger subsystem U4 are all connected to the power management s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More