Method and device for implementing cache data consistency based on distributed finite directory

A technology for caching data and implementing methods, which is applied in multi-programming devices, machine execution devices, electrical digital data processing, etc., and can solve problems such as starvation of request transactions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

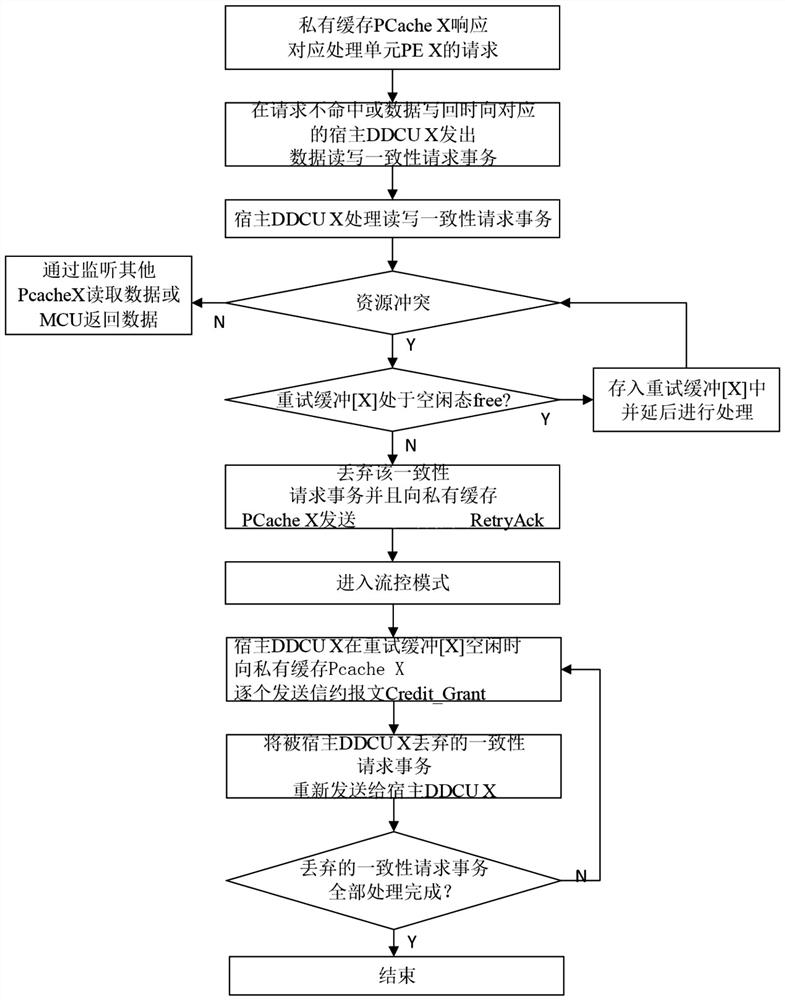

[0029] Such as image 3 As shown, the implementation steps of the cache data consistency implementation method based on the distributed limited directory in this embodiment include:

[0030]1) The private cache PCache X responds to the request of the corresponding processing unit PE X, and sends a data read and write consistency request transaction to the corresponding host DDCU X when the request misses or the data is written back;

[0031] 2) The host DDCU X responds to the data read and write consistency request transaction, and when the data read and write consistency request transaction encounters a resource conflict, if the retry buffer [X] is in the free state, it will be preferentially stored in the retry buffer [X] And delay processing, otherwise discard the data read and write consistency request transaction and send a retry response message RetryAck to the private cache PCache X;

[0032] 3) The flow control mode is entered between the private cache PCache X and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More