Processor with instruction lookahead issue logic

A processor and instruction decoder technology, applied in concurrent instruction execution, instruction analysis, electrical digital data processing, etc., to solve problems such as inaccurate predictions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

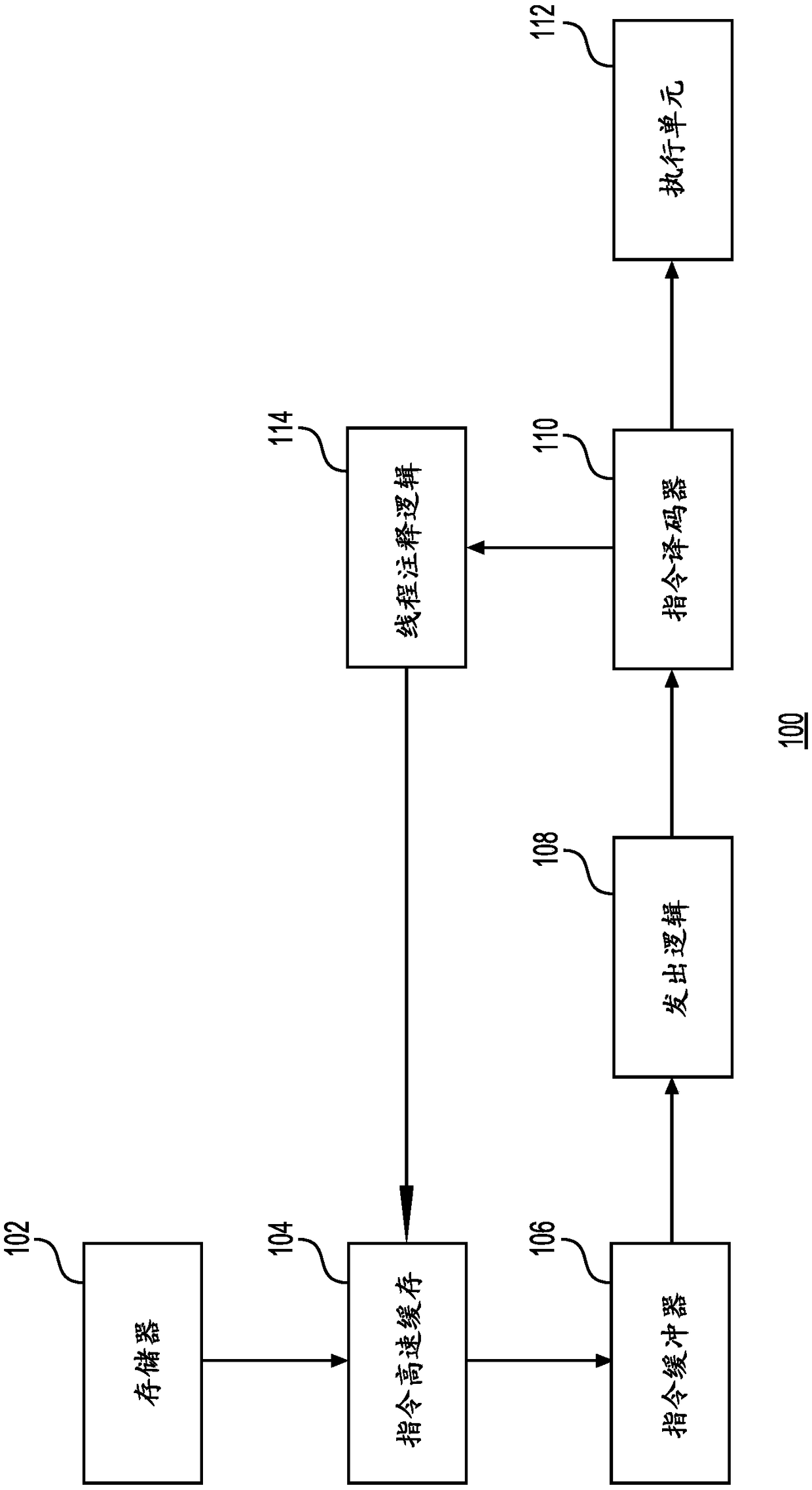

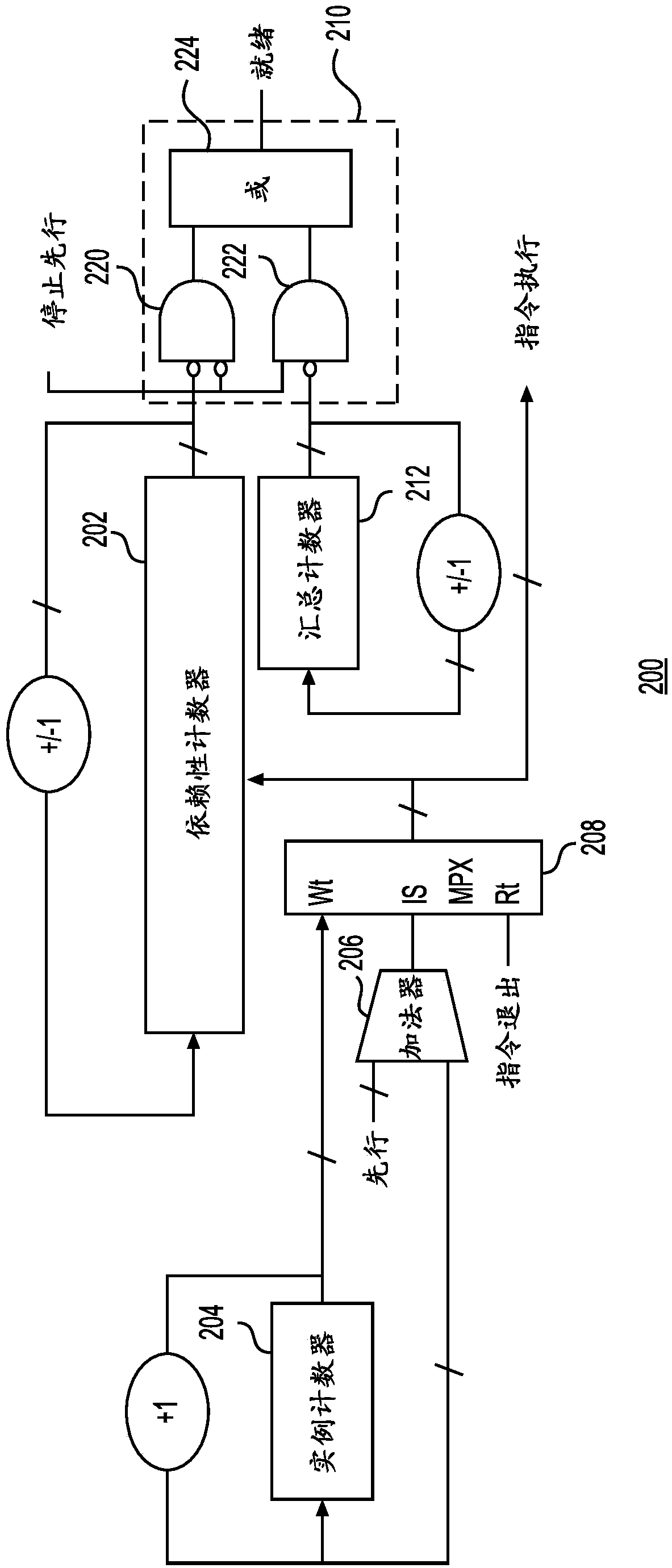

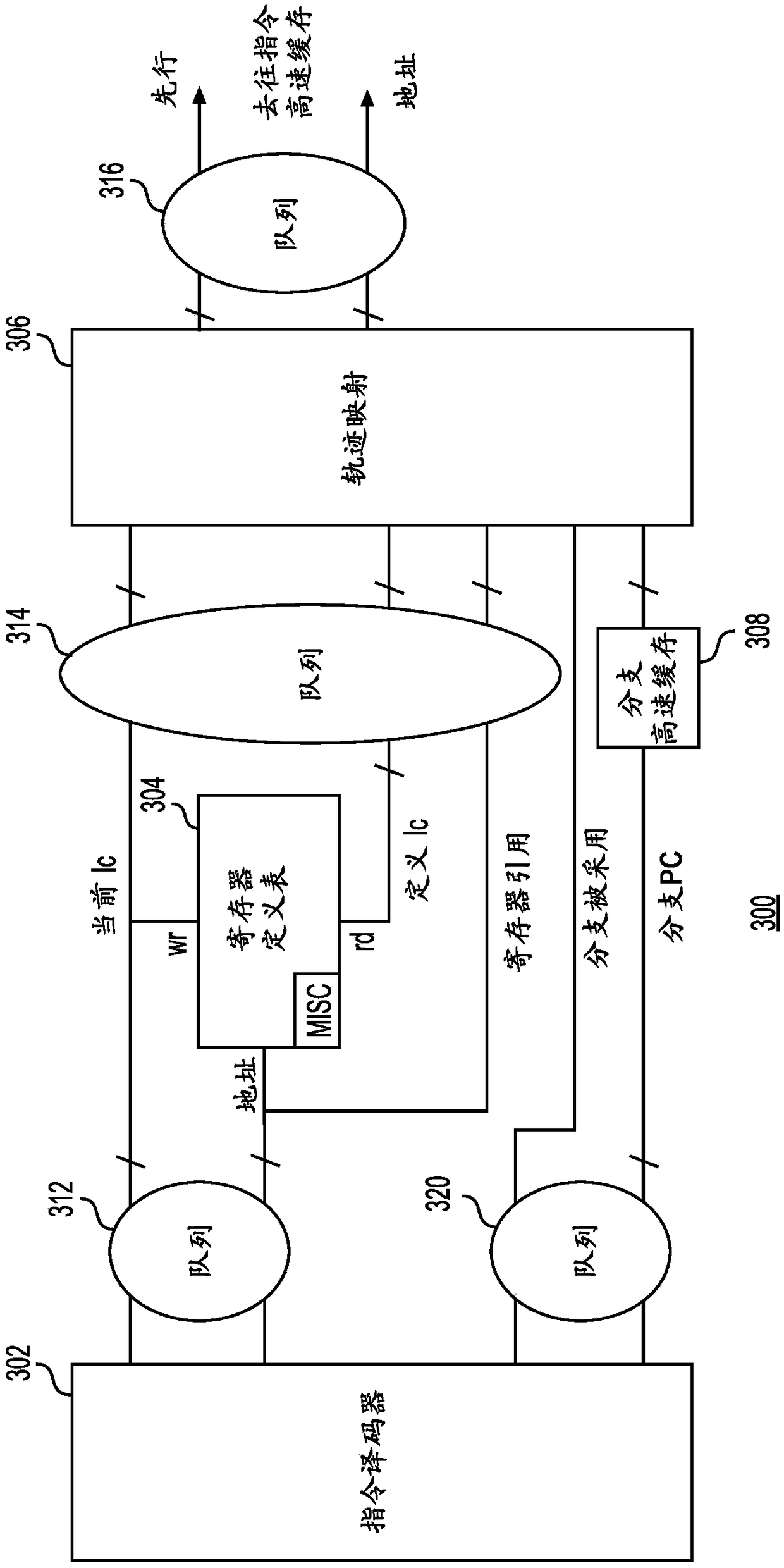

[0013] The examples described in this disclosure relate to processors that can superimpose the execution of instructions that may be part of different threads. Thus, the processor can sequentially fetch instructions belonging to the threads and execute them. Concurrently with executing the instructions of the thread, the processor may execute instructions that generate references to memory locations. This may indicate that the processor may have to wait until the referenced memory location is accessed. Similarly, if an instruction takes multiple cycles to execute, subsequent instructions that depend on that instruction will have to wait. To maintain efficiency, the processor can fetch instructions from a different thread and start executing those instructions. This way, the processor can execute instructions more efficiently. This type of parallelism may be referred to as thread-level parallelism. Another way to improve performance is to gain instruction-level parallelism....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More