Boundary spacer structure and integration

A spacer and boundary technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as limiting device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

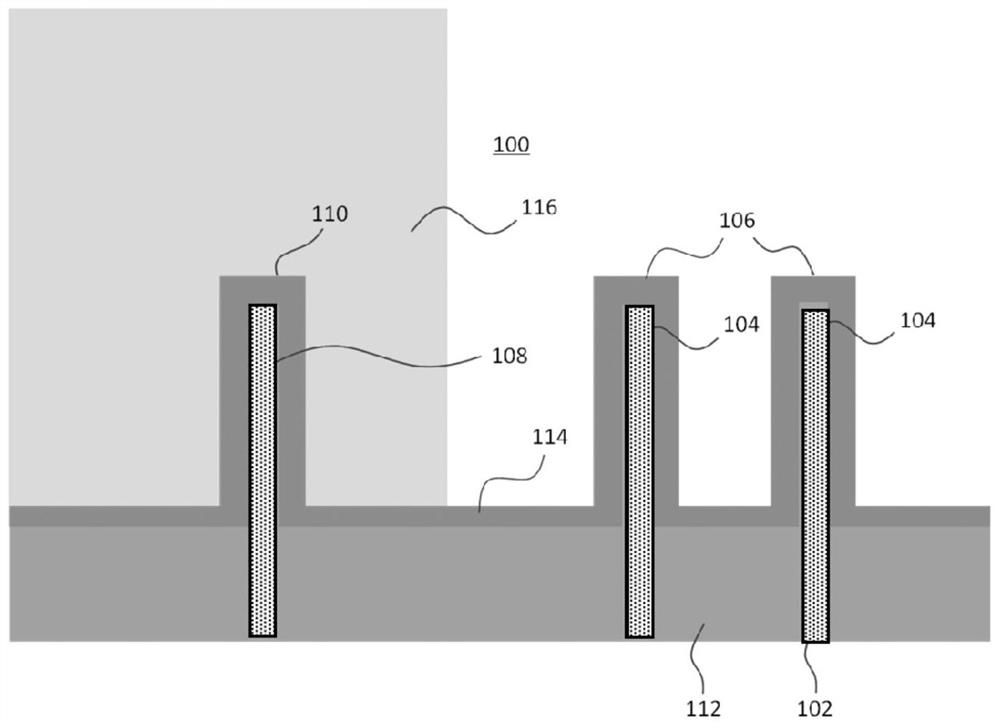

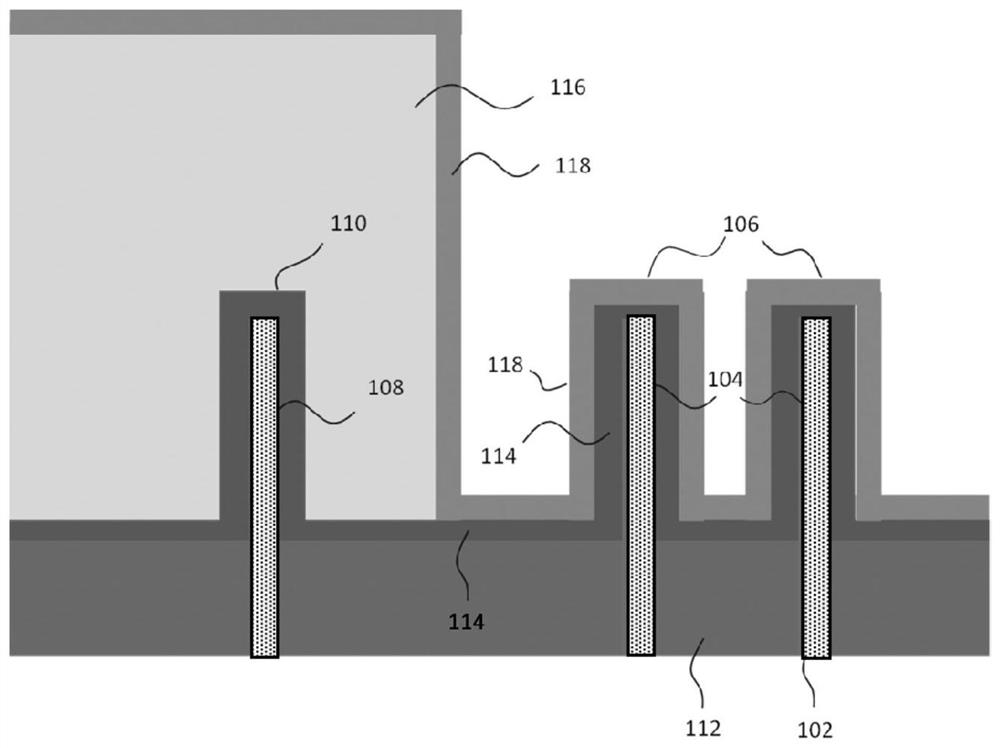

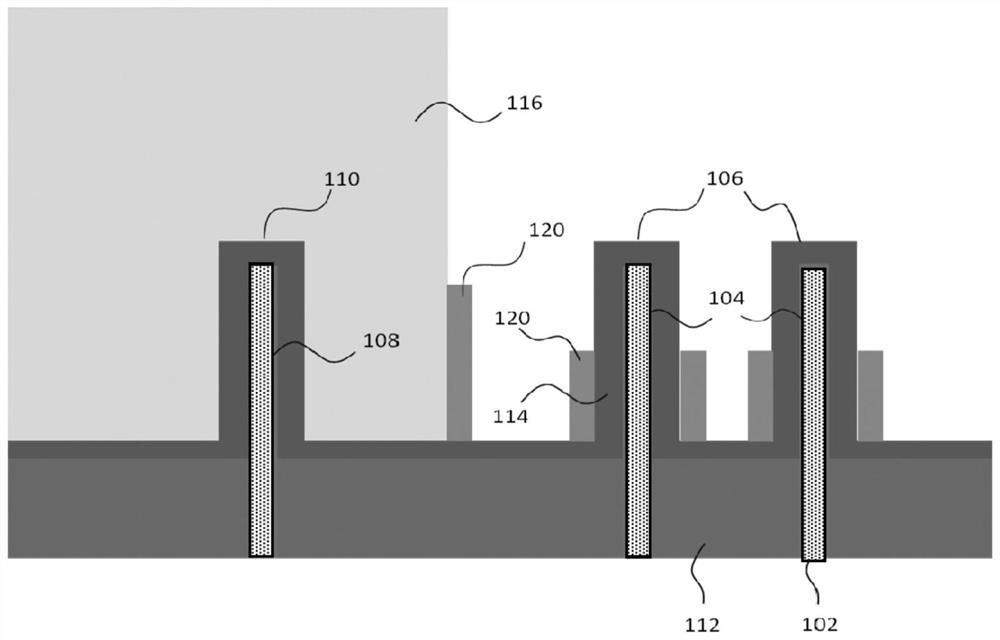

[0015] The present disclosure relates to semiconductor structures, and more particularly, to boundary spacer structures and methods of fabrication for use with FinFET devices. More specifically, the present disclosure provides physical boundaries in the form of barrier layers between fin structures of adjacent devices (eg, PFETs and NFETs) to prevent merging of epitaxial layers in spaces between adjacent fin structures. Advantageously, in an embodiment, a barrier layer between adjacent fin structures will prevent the epitaxial layers from merging together causing short circuits in the device. In addition, the boundary prevents the epitaxial layer of one fin structure from shorting to the Vdd supply line of an adjacent fin structure.

[0016] In a more specific embodiment, in the present disclosure, a mask is formed over the first fin structure on the first device, and a barrier material is formed over the mask and the exposed second fin structure of the second device. Portion...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More