A method and system for extending high-performance encryption and decryption computing capability

A computing capability and extension method technology, applied in the field of high-performance encryption and decryption computing capability extension methods and systems, can solve the problems of insufficient security protection capability, inability to effectively expand encryption and decryption computing performance, and low encryption and decryption computing capability of security chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the object, technical solution and advantages of the present invention more clear and definite, the present invention will be further described in detail below with reference to the accompanying drawings and examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

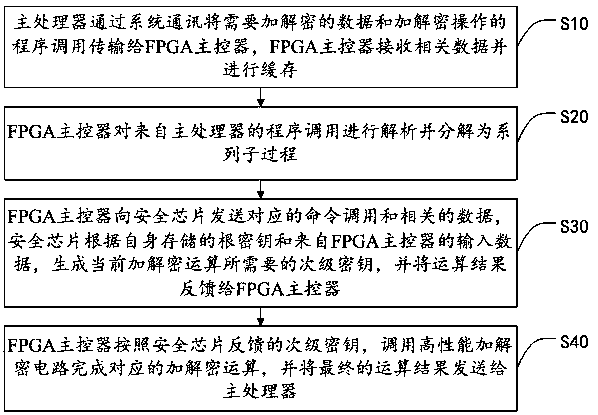

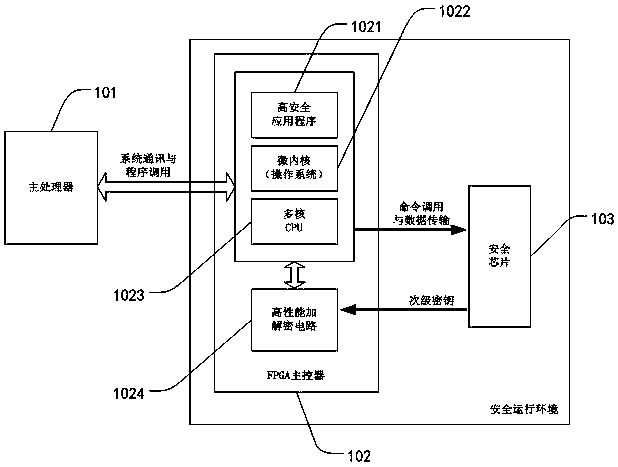

[0041] The high-performance encryption and decryption computing ability expansion method described in the preferred embodiment of the present invention, such as figure 2 As shown, the method for extending the high-performance encryption and decryption computing capability includes the following steps:

[0042] Step S10, the main processor transmits the data to be encrypted and decrypted and the program call of the encryption and decryption operation to the FPGA main controller through the system communication, and the FPGA main controller receives and caches the relevant data.

[0043]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More