Dual-bus dual-power-tube current-limiting circuit, chip and electronic device

A technology of current-limiting circuits and electronic equipment, applied in the field of circuits, can solve the problems of low reliability and high cost of current-limiting protection, and achieve the effects of cost reduction, reliability improvement, and phase deviation avoidance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In the following description, specific details such as specific system structures and technologies are presented for the purpose of illustration rather than limitation, so as to thoroughly understand the embodiments of the present invention. It will be apparent, however, to one skilled in the art that the invention may be practiced in other embodiments without these specific details. In other instances, detailed descriptions of well-known systems, devices, circuits, and methods are omitted so as not to obscure the description of the present invention with unnecessary detail.

[0029] In order to illustrate the technical solutions of the present invention, specific examples are used below to illustrate.

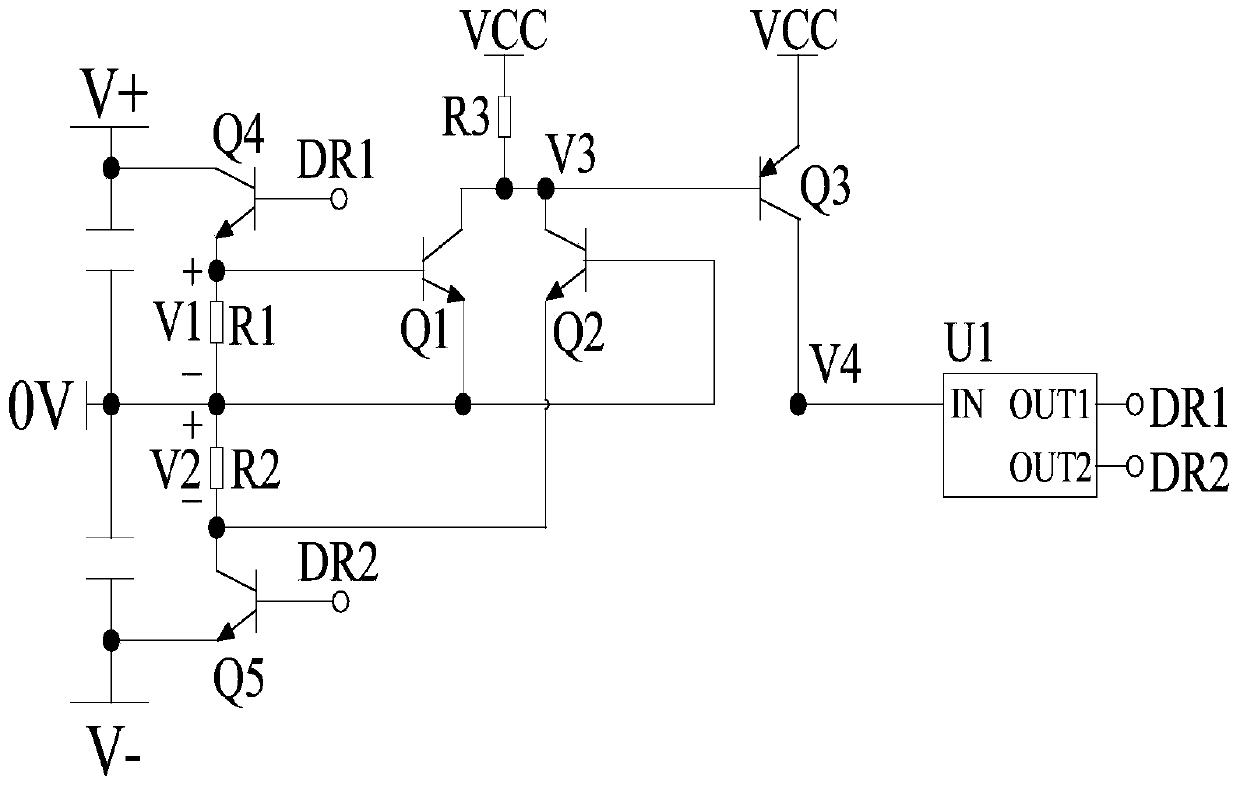

[0030] The embodiment of the present invention provides a dual-bus dual-power tube current limiting circuit, such as figure 1 As shown, the current-limiting circuit with dual busbars and dual power transistors may include a first power resistor R1, a second power resis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More