Multi-chip series automatic address coding system and method

An address coding and multi-chip technology, which is applied in the field of multi-chip serial automatic address coding system, can solve the problems of large number of IOs, unfixable coding address and physical location, inconvenience, etc., achieve high communication efficiency, solve communication delay, and facilitate The effect of repair and replacement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

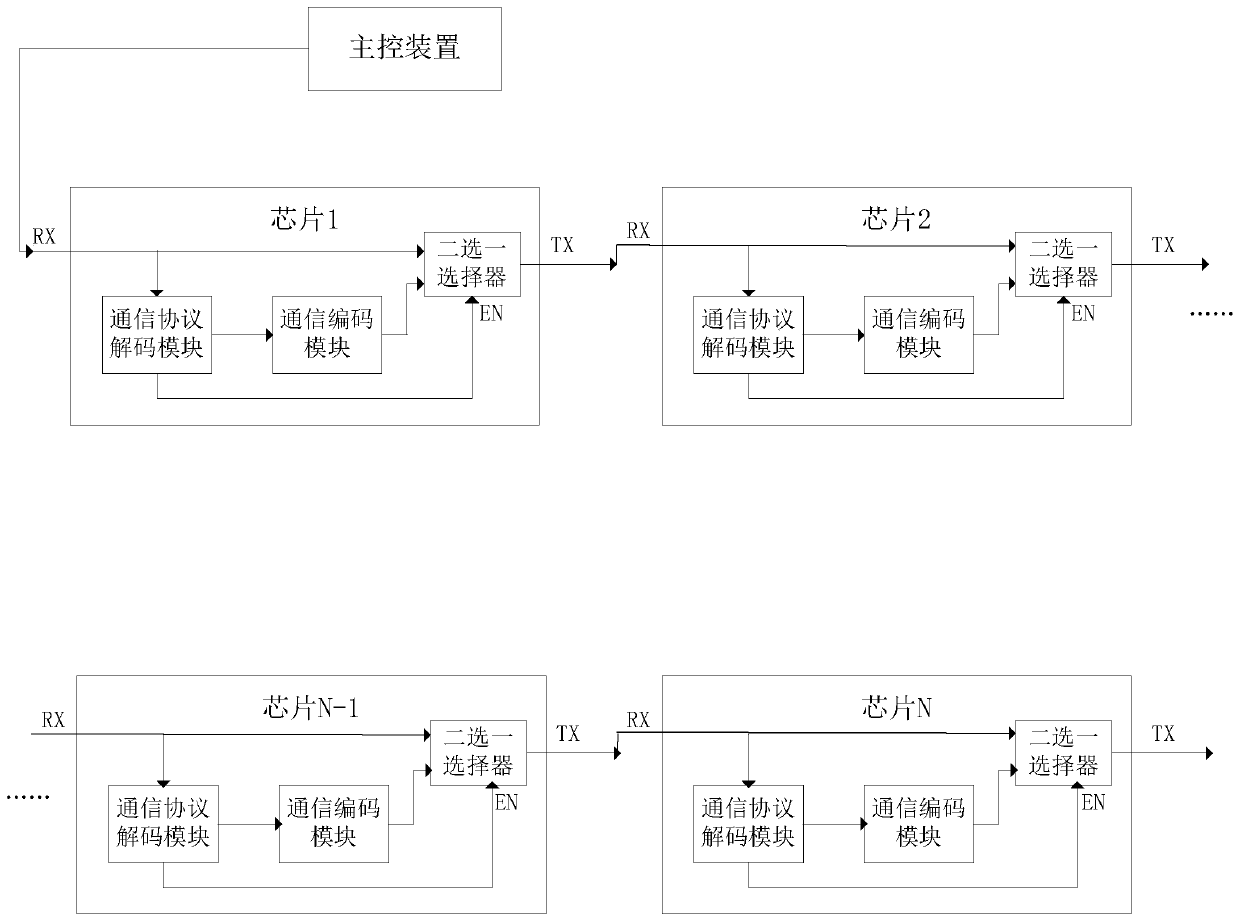

[0033] figure 1 It is a block diagram of a multi-chip serial automatic address coding system module in Embodiment 1 of the present invention, referring to figure 1 , a multi-chip series automatic address coding system, including a main control device and N chips, the main control device is connected to the first chip, from the first chip to the Nth chip, the sending end TX of the chip is connected to the next chip The receiver RX connection of the chip.

[0034] Wherein, the master control device is used to send an automatic address allocation command to the first chip; the automatic address allocation command includes an ID.

[0035] The chip is used to receive the automatic address allocation instruction, decode the automatic address allocation instruction, obtain the ID, set the ID as the chip ID, and perform the operation on the ID according to the operation rules, obtain the automatic allocation address instruction for the operation, and automatically assign the address ...

Embodiment 2

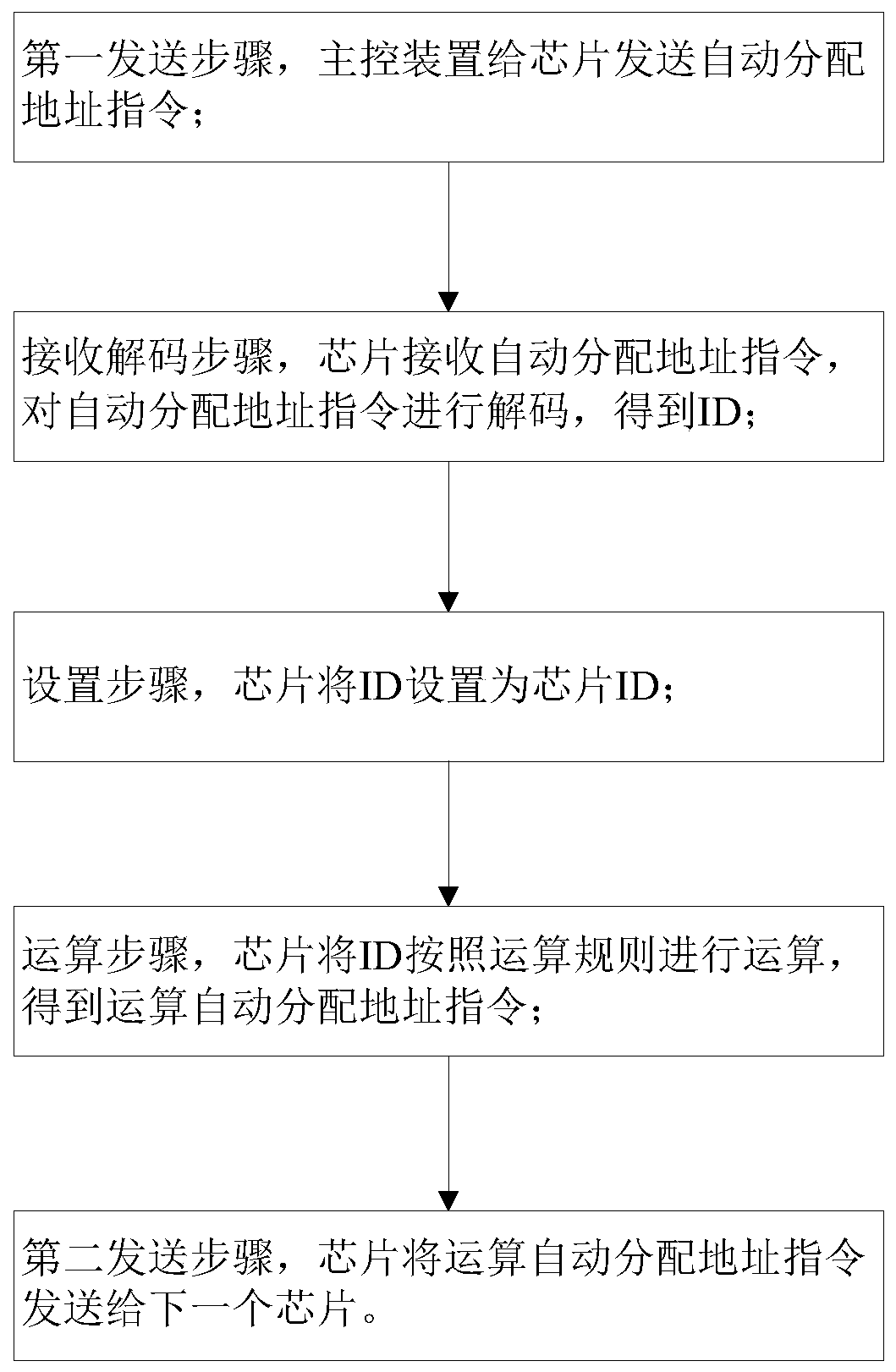

[0043] figure 2 It is a schematic flow chart of the multi-chip serial automatic address coding method in Embodiment 2 of the present invention, referring to figure 2 , a multi-chip series automatic address coding method, comprising:

[0044] In the first sending step, the master control device sends an automatic address allocation instruction to the chip;

[0045] Among them, the automatic address assignment instruction includes ID;

[0046] Receive the decoding step, the chip receives the automatic address allocation command, decodes the automatic address allocation command, and obtains the ID;

[0047] In the setting step, the chip sets the ID as the chip ID;

[0048] In the operation step, the chip performs the operation on the ID according to the operation rules, and obtains the operation automatic allocation address instruction;

[0049] Among them, the operation rule is increment operation;

[0050] In the second sending step, the chip sends the operation automatic ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More