AES hardware encryption system implementation method based on quantum reversible circuit

An implementation method and hardware encryption technology, applied in the field of information security, can solve the problems of lack of quantum reversible circuit key expansion module interface module, inability to put into use, lack of practicality, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0116] In order to clearly illustrate the technical features of the solution, the solution will be described below through specific implementation modes.

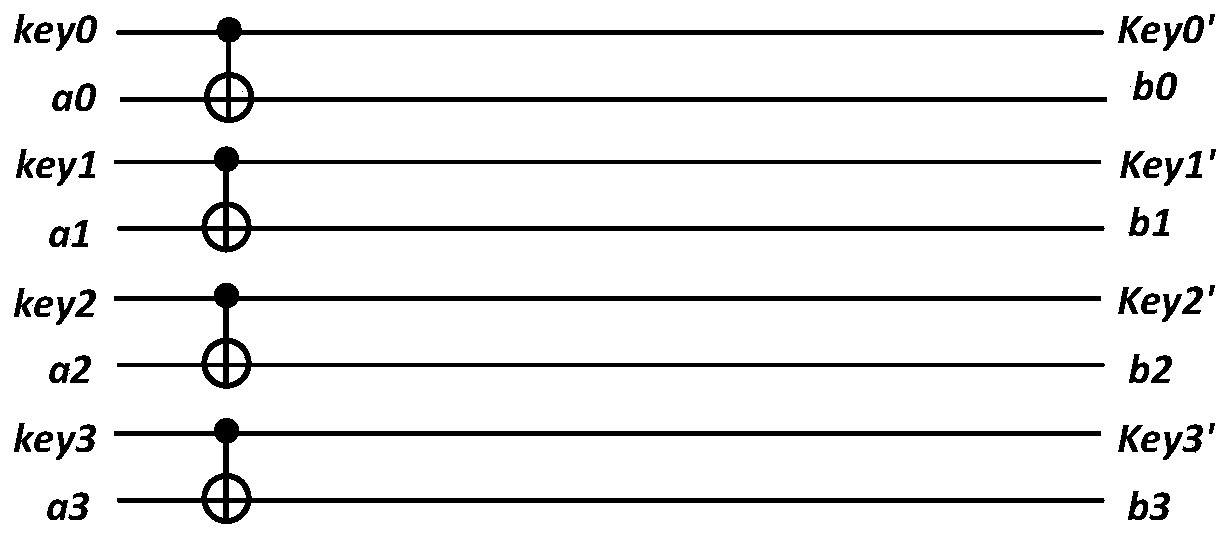

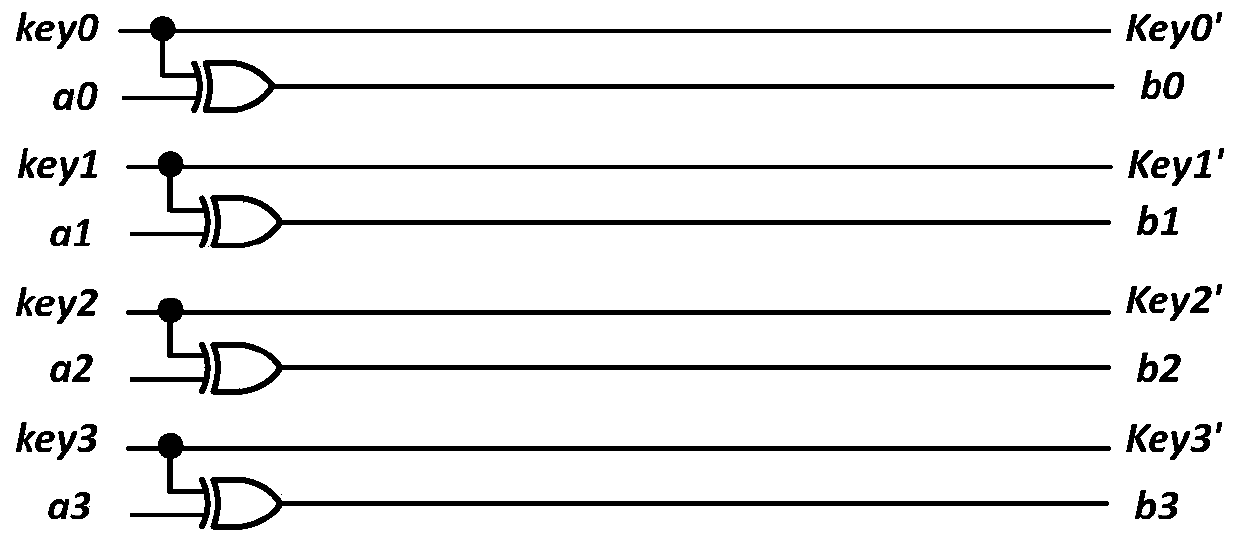

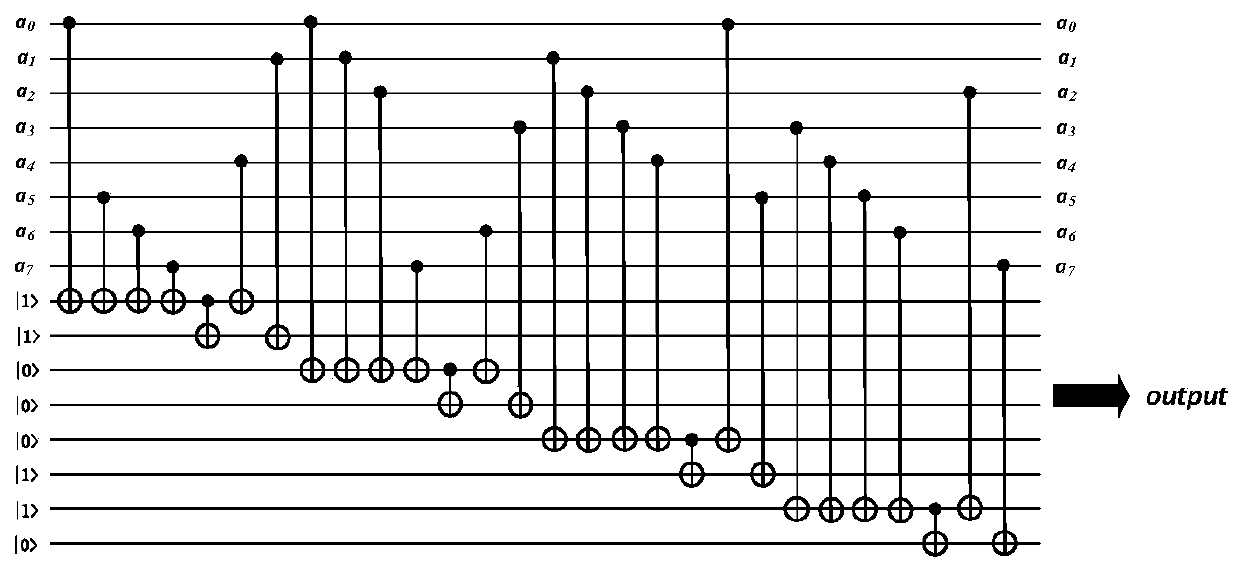

[0117] see Figure 1 to Figure 13 , the present invention is: a kind of realization method based on the AES hardware encryption system of quantum reversible circuit comprises the following steps:

[0118] The method comprises the steps of:

[0119] Step A: Realize the hardware setting of the quantum reversible circuit encryption and decryption module;

[0120] Step B: Realize the hardware setting of the quantum key expansion module;

[0121] Step C: Setting up the multi-interface selection module by using the electronic circuit.

[0122] As a further optimization scheme of the implementation method of an AES hardware encryption system based on quantum reversible circuits in the present invention, the step A is specifically that the quantum reversible circuit encryption and decryption module is divided into an encryption ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More