Low-power time-to-digital converter

A time-to-digital converter technology, which is used in time-to-digital converters, electrical unknown time interval measurement, devices for measuring time intervals, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

[0033] Hereinafter, the present invention will be more fully described in reference embodiments in conjunction with the drawings. The present invention provides preferred embodiments, but should not be considered as limited to the embodiments set forth herein.

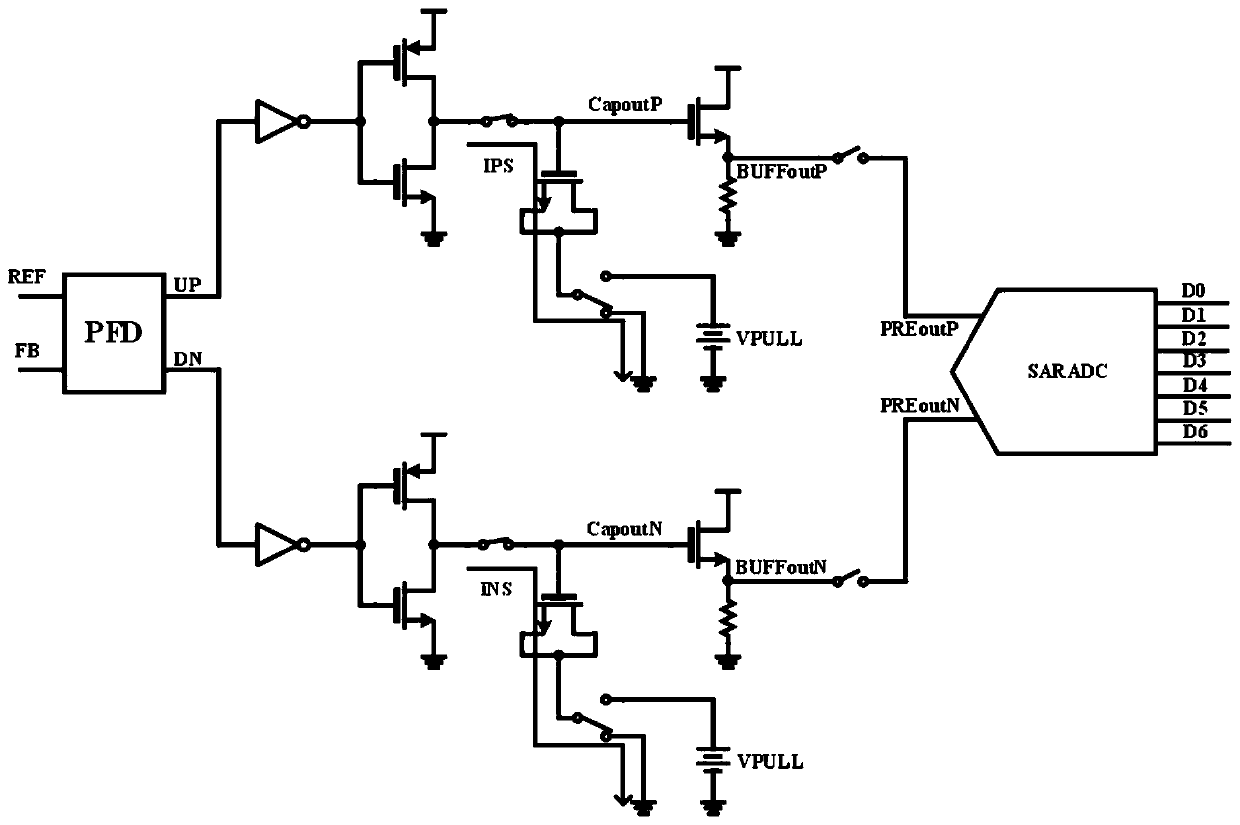

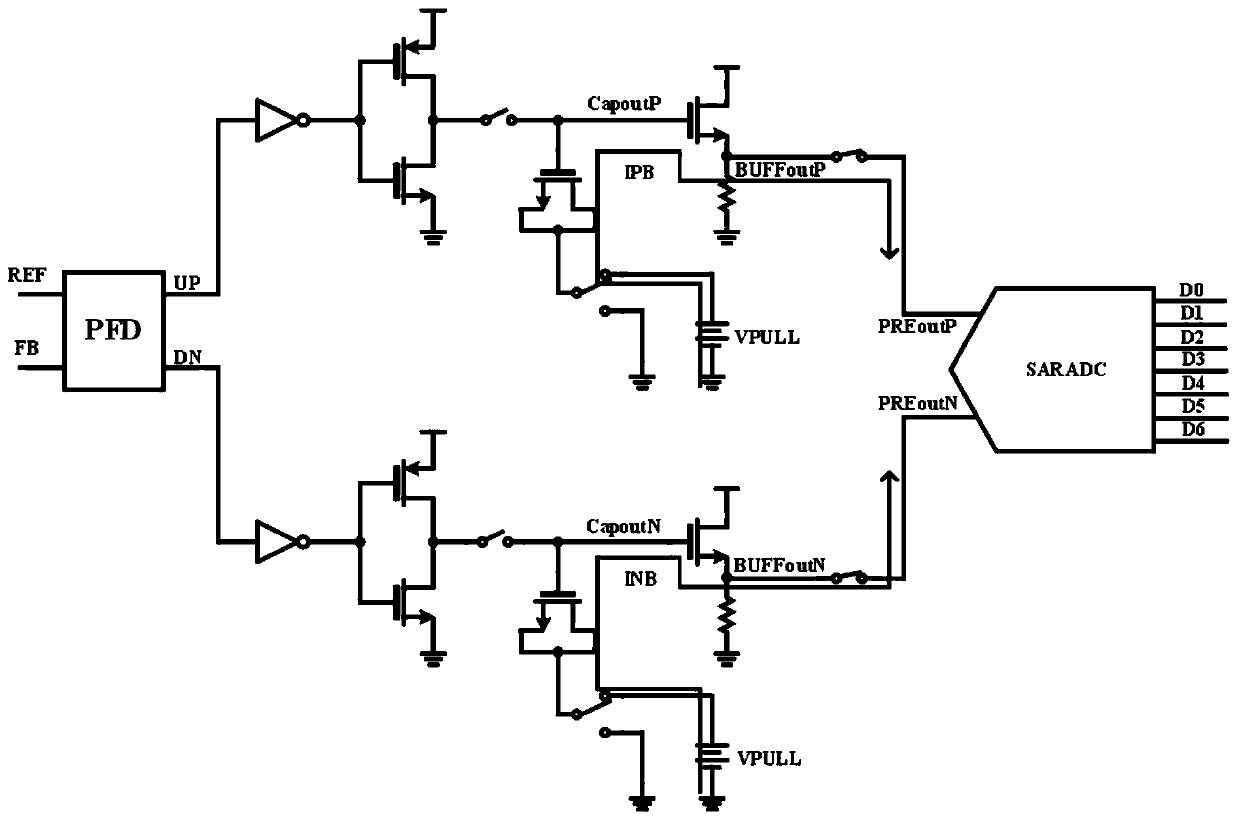

[0034] The present invention provides a low-power time-to-digital converter, which is figure 1 The circuit architecture shown includes a pre-amp (Pre-amp) and a successive approximation register analog-to-digital converter (SARADC); the input signal is input into the pre-amplifier in the form of pseudo-differential for amplification, and then by successive approximation The register type analog-to-digital converter converts into a digital signal. Among them, the design principle of the pre-amplifier is to obtain the phase difference between the two input clock signals, and the phase difference is input into the inverter in the form of a pulse and converted into a voltage before amplifying. The analog-to-digital converter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More