LDO-based FPGA loading configuration problem checking method

A problem detection and problem technology, which is applied in the field of LDO-based FPGA loading and configuration problem checking, can solve problems such as FPGA configuration loading failure, and achieve the effects of stable and reliable loading configuration, rapid problem location, and cost reduction.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

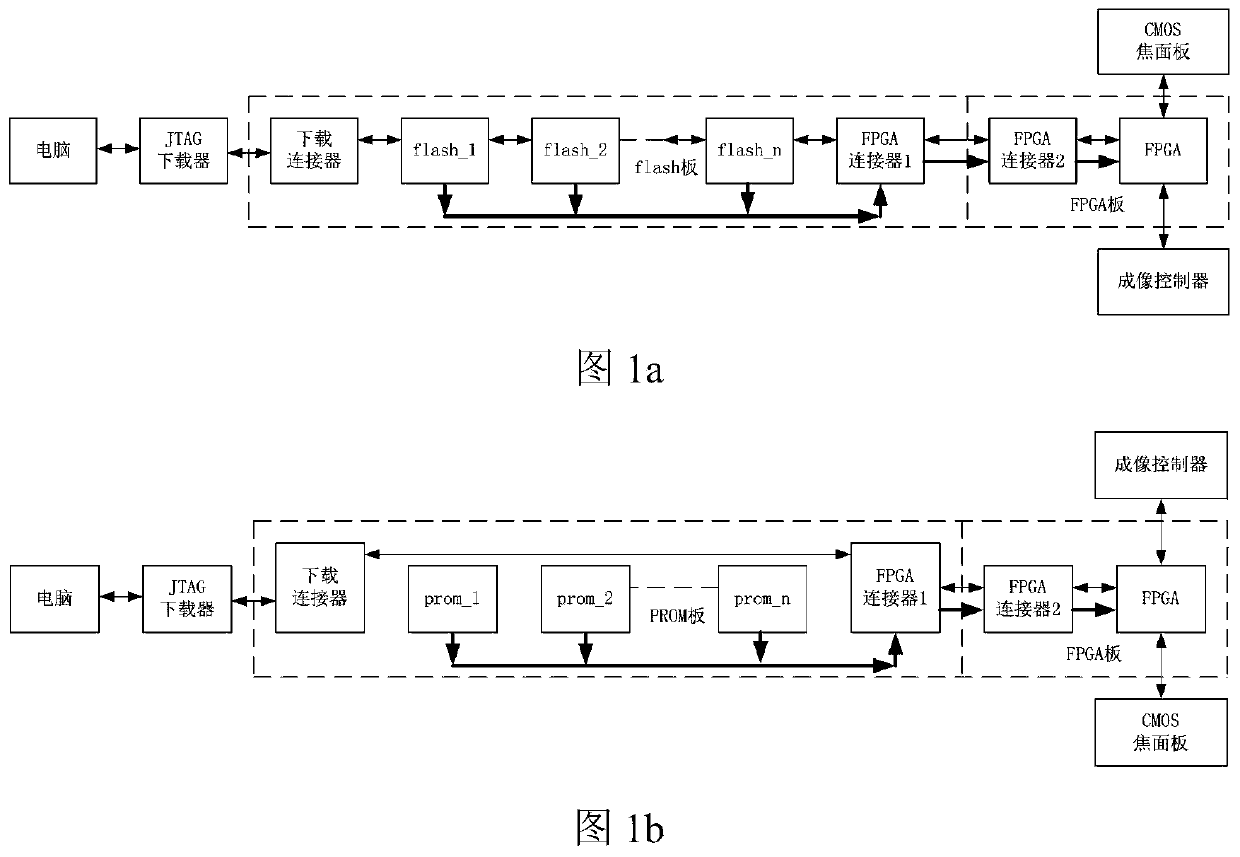

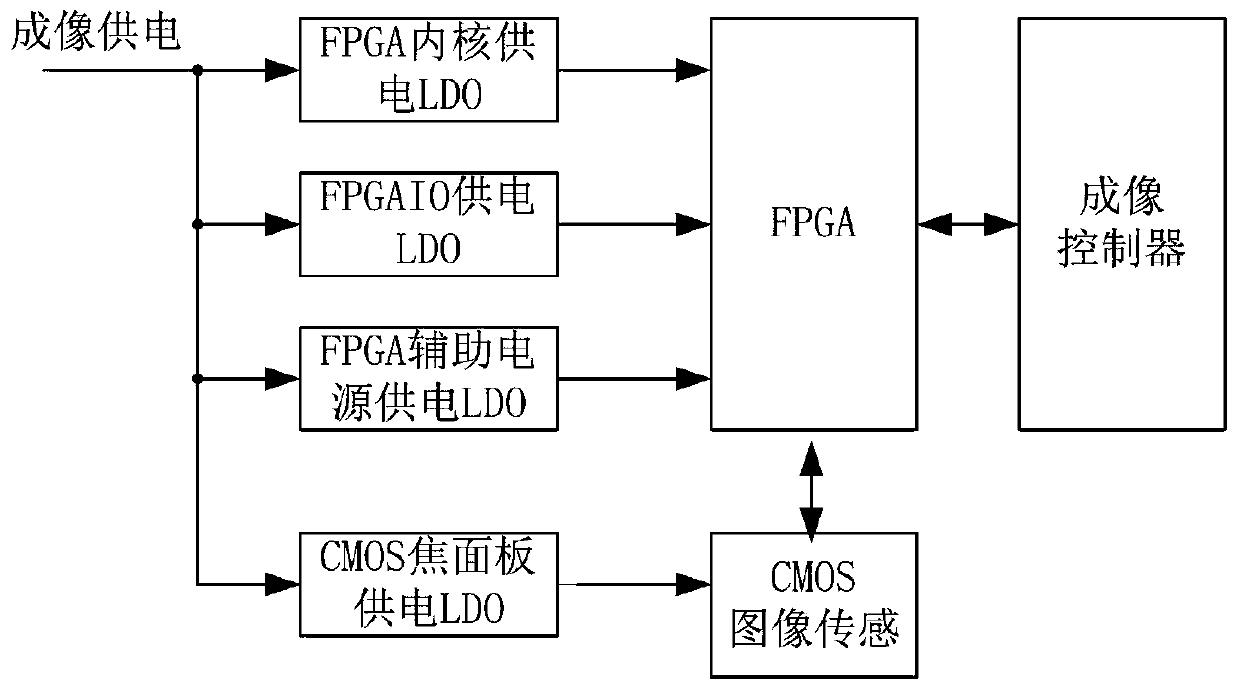

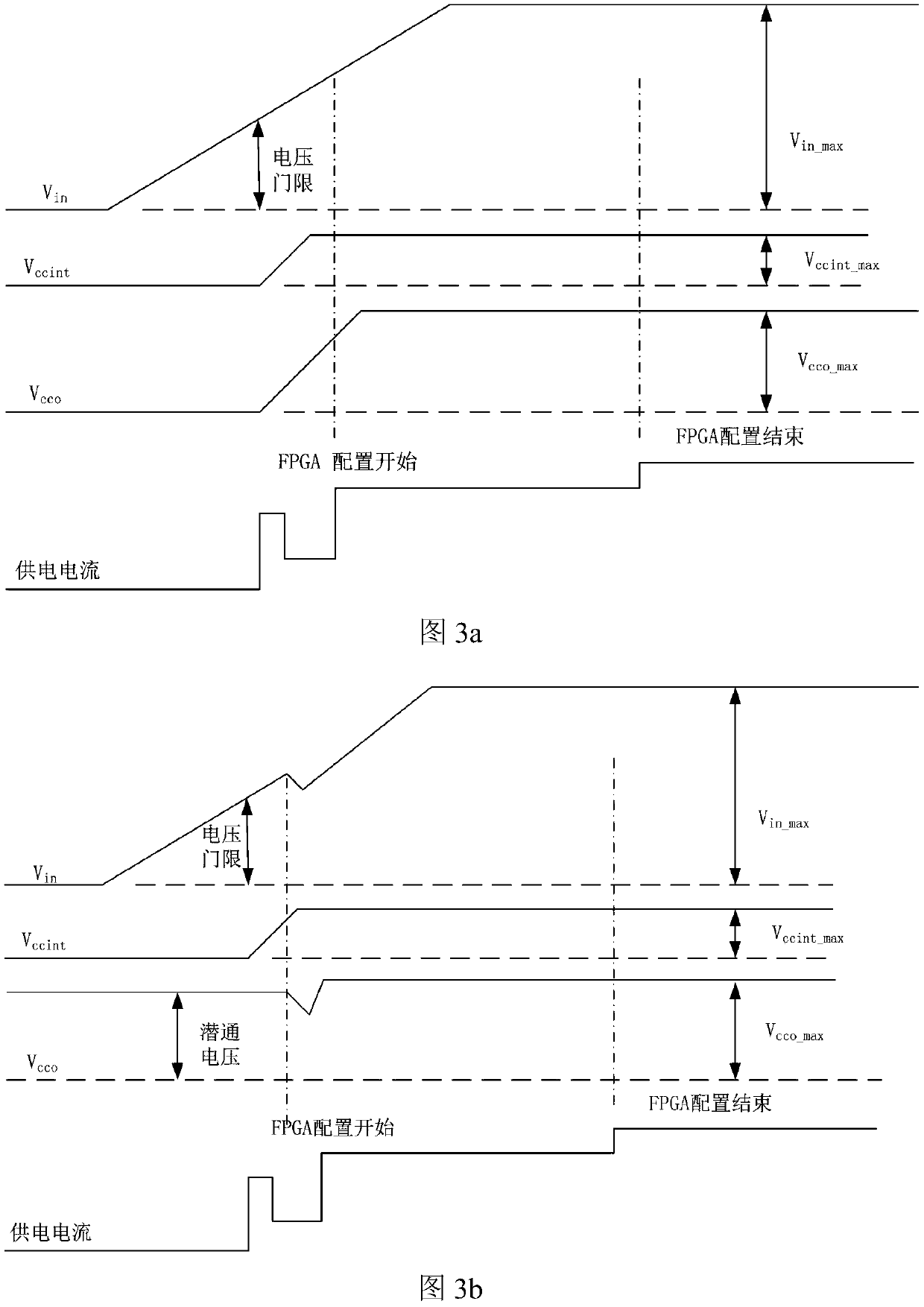

[0037] Specific implementation mode 1. Combination Figure 1 to Figure 9 Description of this embodiment, the LDO-based FPGA loading configuration problem checking method, including the FPGA imaging configuration loading system, combined with figure 1 , including computer, JTAG downloader, FPGA board, CMOS focus panel and imaging controller, and also includes prom board or flash board. The FPGA board includes an FPGA and an FPGA connector 2 connected to the prom or flash board. The prom board contains the FPGA connector 1 connected to the FPGA board, and contains n proms at the same time; the flash board contains the FPGA connector 1 connected to the FPGA board, and contains n flashes at the same time; the signal on the FPGA connector 1 of the two compatible. combine figure 1 a, The flash-based FPGA imaging configuration loading system can directly download the configuration data of the FPGA to the FPGA through the daisy chain structure from the computer to the JTAG download...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More