TSV-based multi-chip package structure and method for fabricating same

A multi-chip packaging and chip technology, which is used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problem of limited chip size selection, unfavorable development of diversified chip packaging, etc., and achieve the effect of compact packaging structure.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

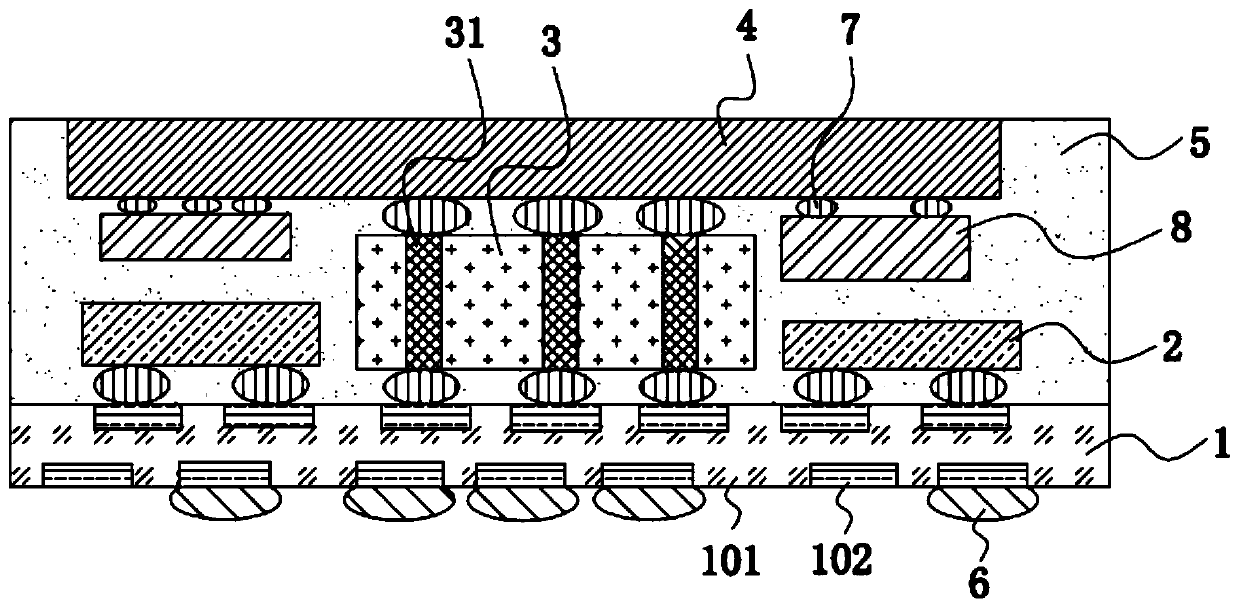

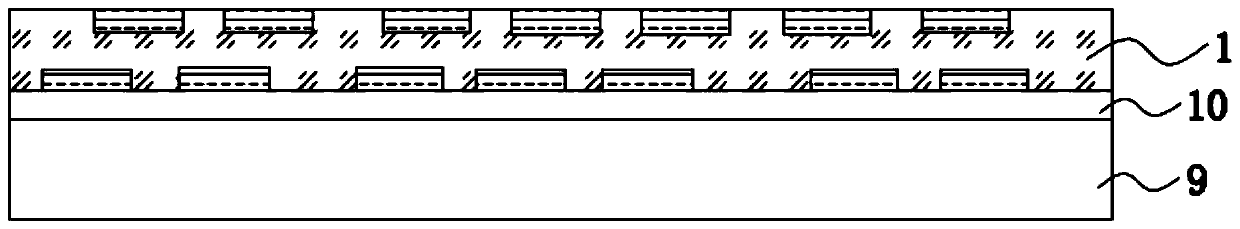

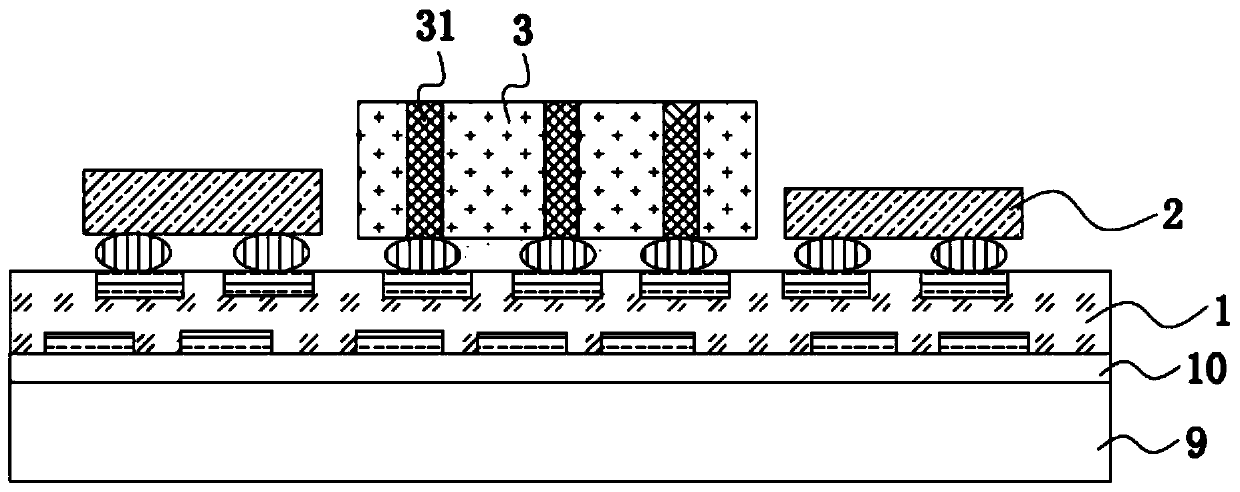

[0038] Such as figure 1 As shown, this embodiment relates to a TSV-based multi-chip packaging structure, including an interconnection structure 1 , a first chip 2 , an interposer 3 , a second chip 4 , a packaging layer 5 and a bump structure 6 .

[0039] Wherein, the first chip 2 and the adapter plate 3 are installed on the interconnection structure 1, and the first chip 2 and the adapter plate 3 are located on the same side of the interconnection structure 1; the second chip 4 is installed on the adapter plate 3 On the top, the second chip 4 is arranged opposite to the interconnection structure 1; the encapsulation layer 5 is arranged on the interconnection structure 1, and the encapsulation layer 5 is used for plastic sealing the first chip 2, the interposer 3 and the second chip 4; bumps The structure 6 is arranged on the interconnection structure 1 and is located on the side opposite to the first chip 2 , and the bump structure 6 is used to realize the electrical connectio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More