Multi-bit Signal Transmission Method for Integrated Circuit Memory

An integrated circuit and signal transmission technology, applied in the direction of digital memory information, static memory, instruments, etc., can solve problems such as abnormal performance of storage units and failure to successfully read stored data, so as to eliminate influence and interference and improve the success rate of reading , the effect of accurate verification and debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] In this embodiment, the multi-bit signal transmission method of the integrated circuit memory includes: providing an integrated circuit memory.

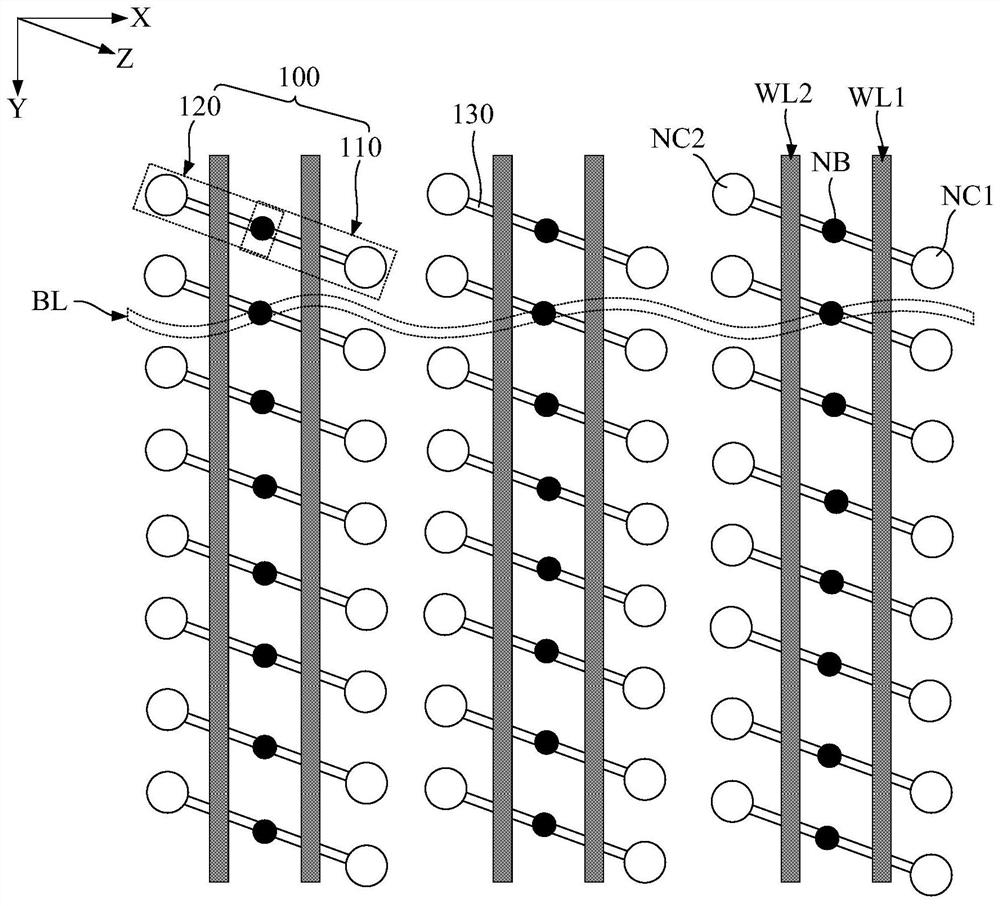

[0055] figure 2 It is a schematic structural diagram of the integrated circuit memory in Embodiment 1 of the present invention, such as figure 2 As shown, the integrated circuit memory includes at least one combination memory unit 100, and the combination memory unit 100 includes a plurality of storage subunits, and the plurality of storage subunits are connected to the same bit line. In this embodiment, the combined storage unit 100 includes a first storage subunit 110 and a second storage subunit 120, and the first storage subunit 110 and the second storage subunit 120 share a bit line node NB, And connected to the same bit line BL through the bit line node NB.

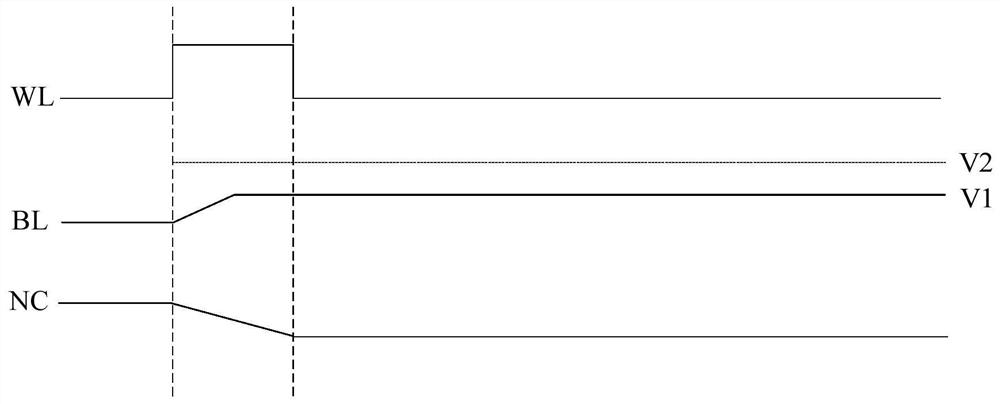

[0056] Wherein, the multi-bit signal transmission method of the integrated circuit memory further includes: performing a write operation on the combination memo...

Embodiment 2

[0097] The difference from Embodiment 1 is that in this embodiment, multiple memory sub-units of the composite memory unit are respectively formed in different active regions.

[0098] Figure 5 It is a schematic structural diagram of the integrated circuit memory in Embodiment 2 of the present invention. Such as Figure 5 As shown, the integrated circuit memory includes a plurality of active regions 130 , and the plurality of memory subunits of the combination memory unit 100 are respectively formed on different active regions 130 . In this embodiment, the first storage subunit 110 and the second storage subunit 120 of the combined memory unit 100 are respectively formed in two adjacent active regions 130 . And, both the active region 130 corresponding to the first storage subunit and the active region 130 corresponding to the second storage subunit intersect with the same bit line BL, so that both the first storage subunit 110 and the second storage subunit 120 are connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More