Method and system for quickly verifying IP prototype of FPGA platform

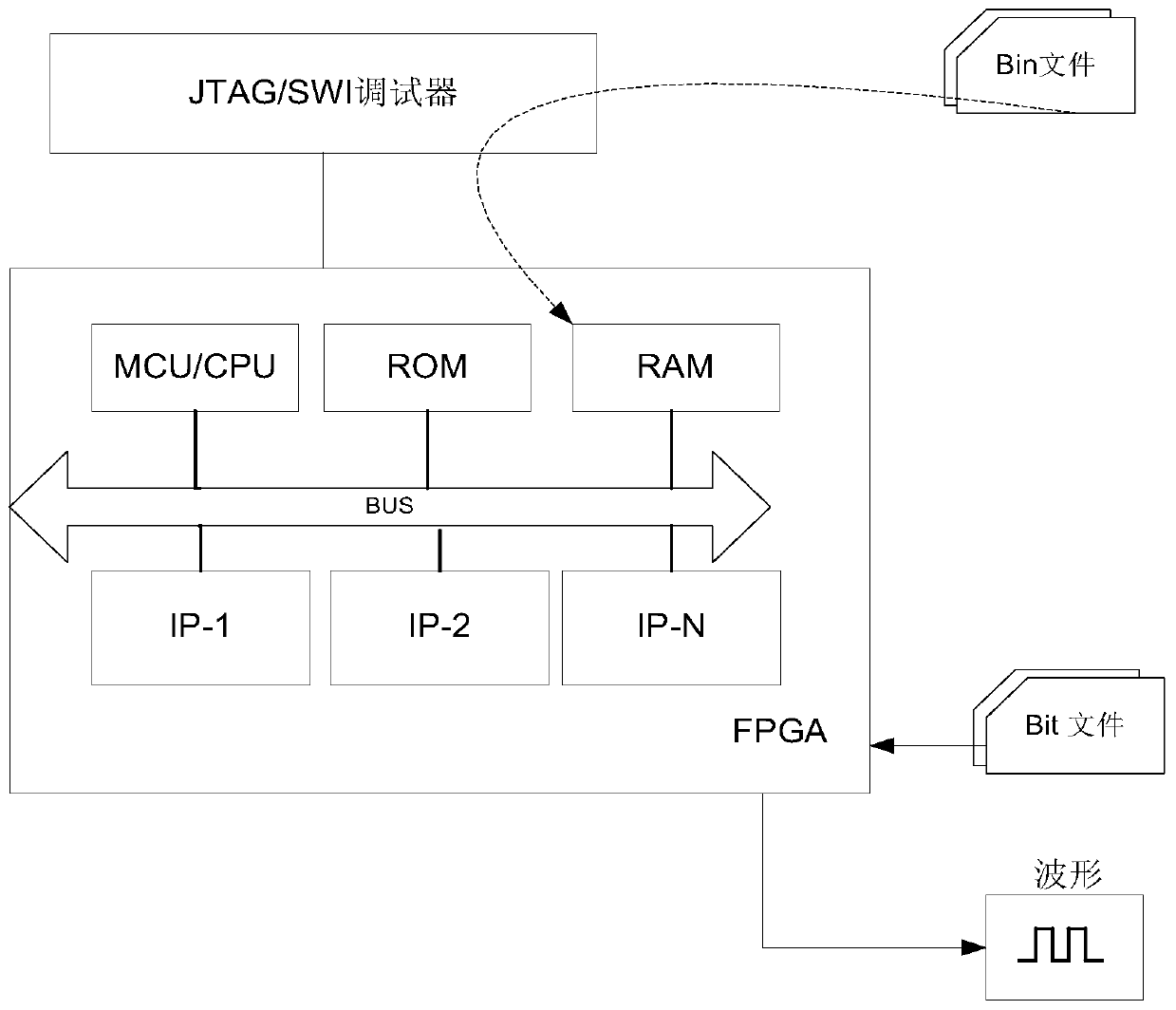

A verification method and verification system technology, applied in FPGA platform IP prototype rapid verification method and system field, can solve problems such as low efficiency, difficult debugging, high error rate, etc., achieve less logic, save early work, and reusability strong effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

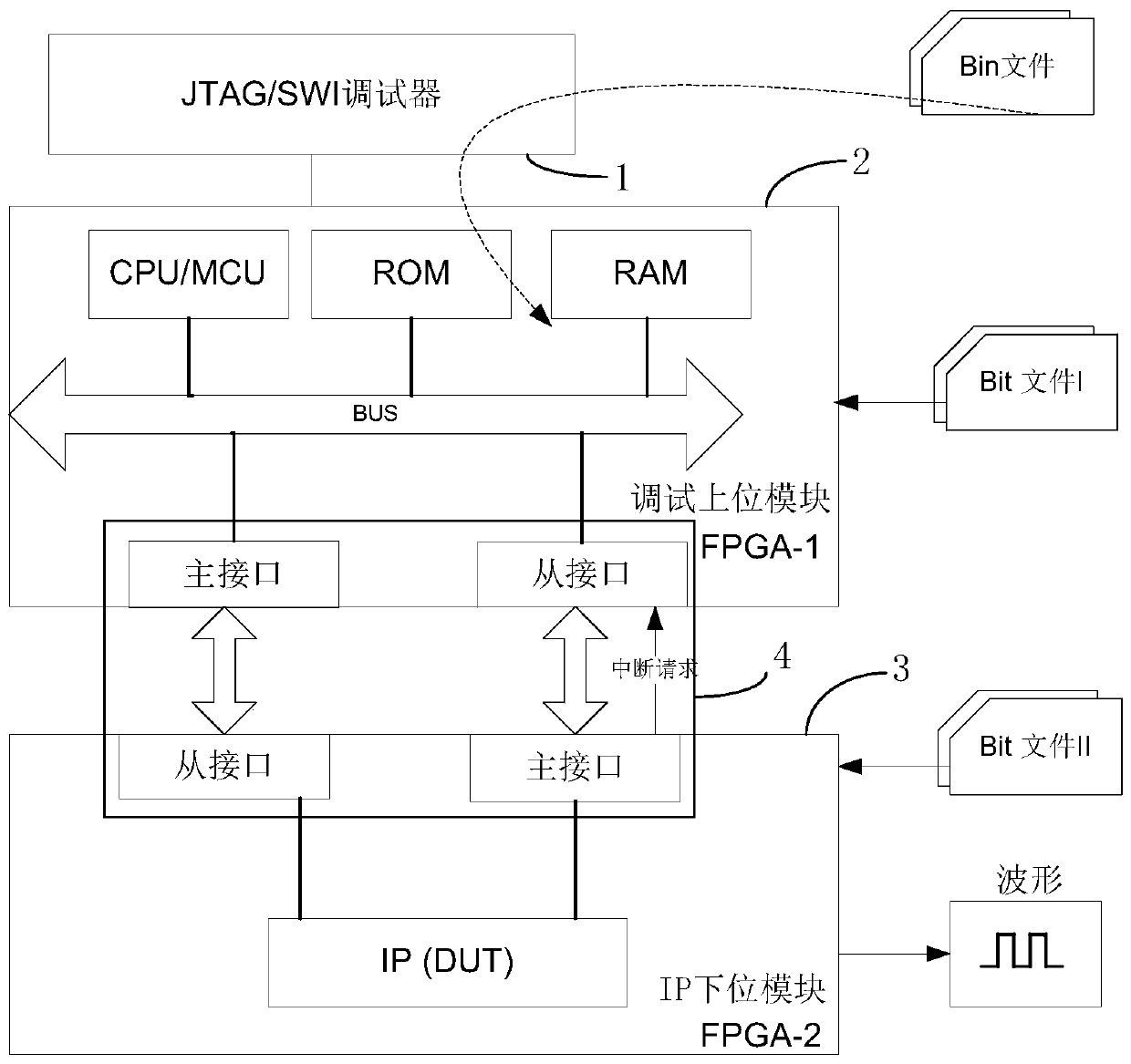

[0040] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

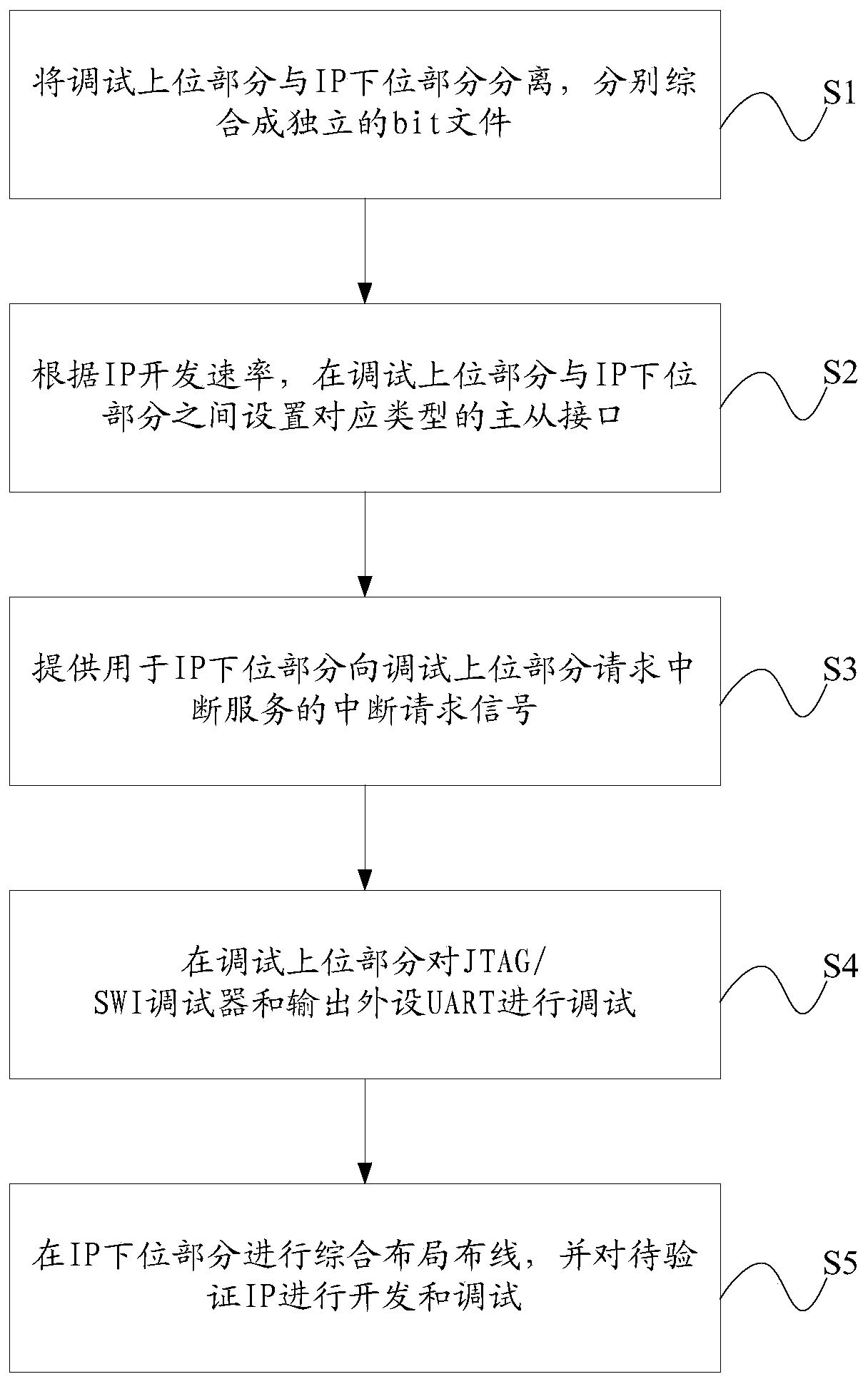

[0041] On the one hand, see attached figure 2 , the embodiment of the present invention discloses a method for quickly verifying an FPGA platform IP prototype, the method comprising the following steps:

[0042] S1: Separate the debugging upper part and the IP lower part, and synthesize them into independent bit files respectively;

[0043] S2: according to the IP development rate, a corresponding type of master-slave interface is set between the debugging u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More