Processor compatible with multi-instruction system and operation method thereof

A technology of instruction system and operation method, applied in concurrent instruction execution, machine execution device, electrical digital data processing, etc., can solve the problem of low efficiency, X86 processor cannot hardware execute MIPS instruction system, processor cannot hardware compatible instruction system, etc. problem, to achieve the effect of maintaining execution efficiency and small hardware cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

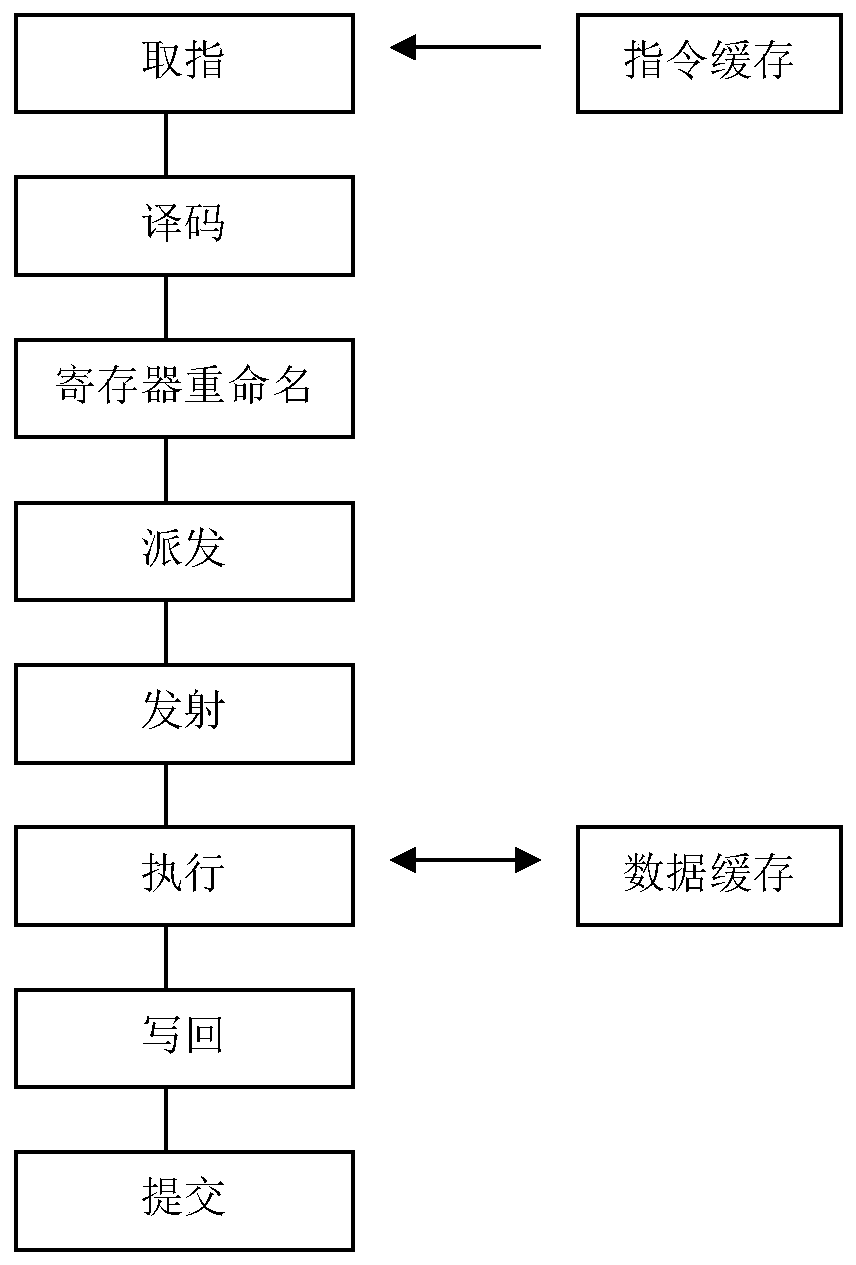

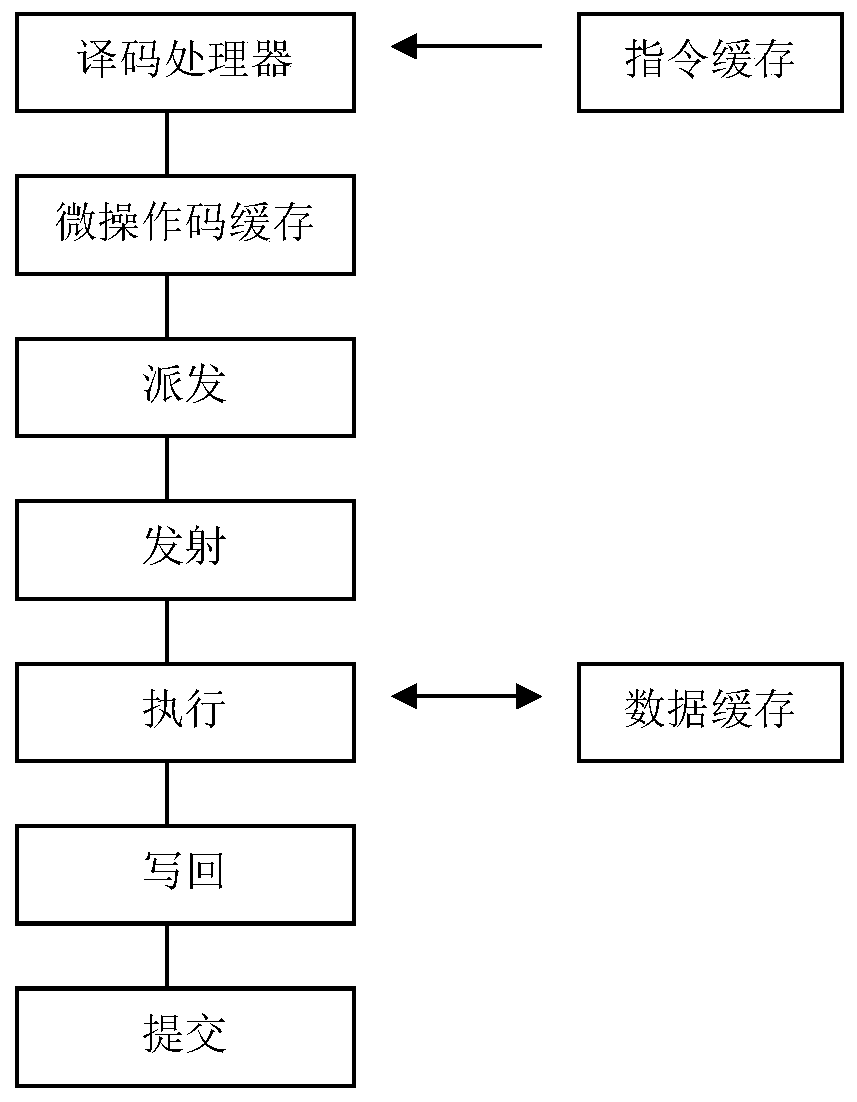

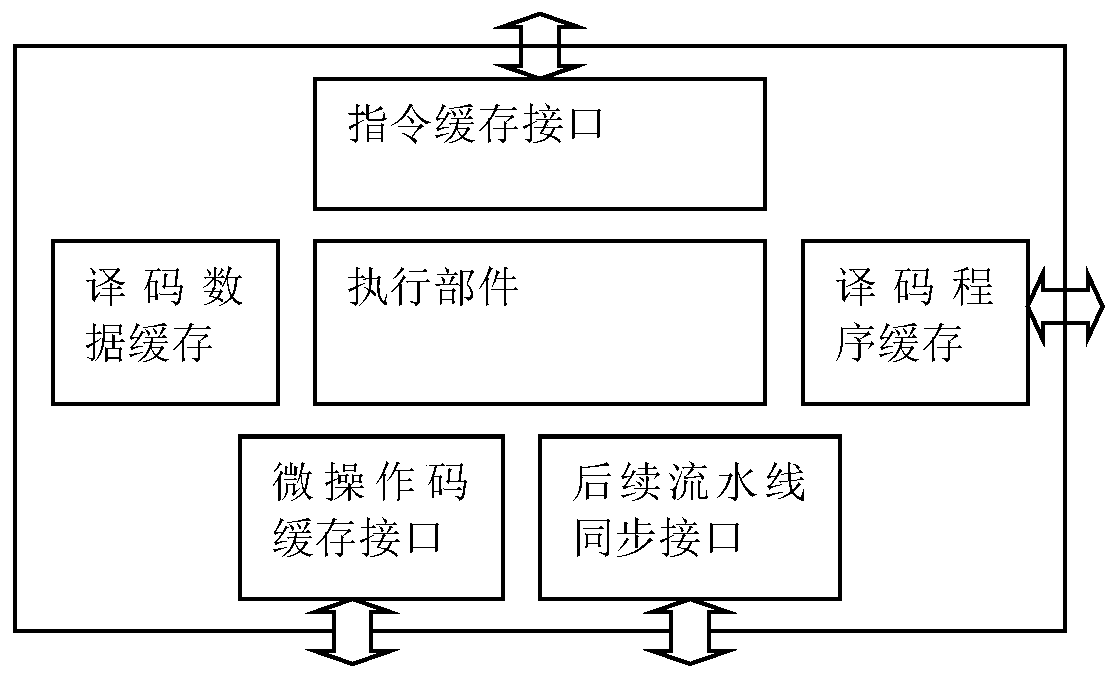

[0039] The microstructures and functions of existing processors with different instruction systems are very similar. Such as figure 1 As shown, all adopt the pipeline structure, and the functions of each part of the pipeline are similar, and the biggest difference is the decoding part. The decoding components of different processors implement instruction decoding of different instruction systems, which are different from each other. Since the decoding component is implemented by hardware and cannot be changed dynamically, this results in a processor that implements a specified instruction system not being compatible with other instruction systems in hardware. However, if the decoding component is implemented in a software programmable manner, then only the decoding software of the software decoding component is updated to switch to another instruction system processor without affecting the execution efficiency of the processor at all.

[0040] The present invention includes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More