Interference analysis method among DAG real-time tasks based on division scheduling on multi-core processor

A multi-core processor, real-time task technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as affecting the accuracy of scheduling analysis, not considering the impact, etc., to achieve the effect of improving accuracy and reducing repeated calculations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

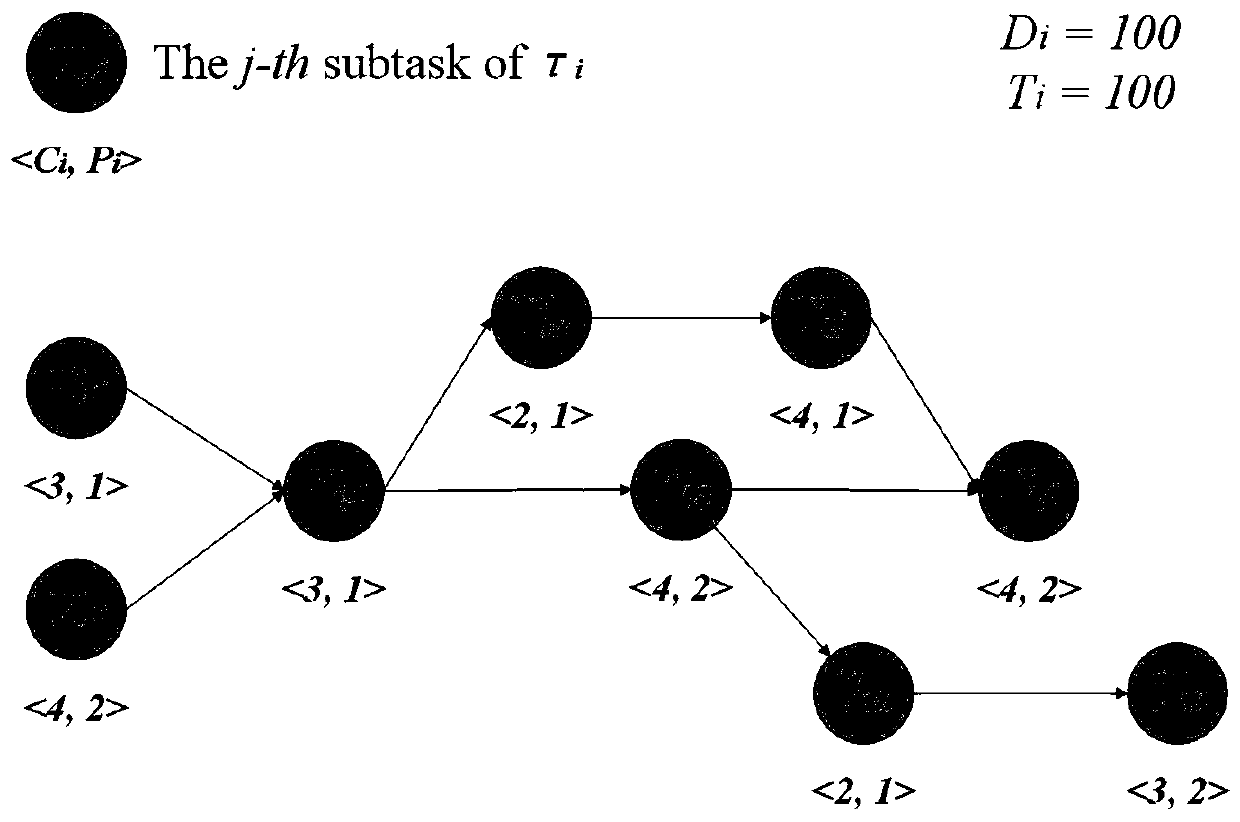

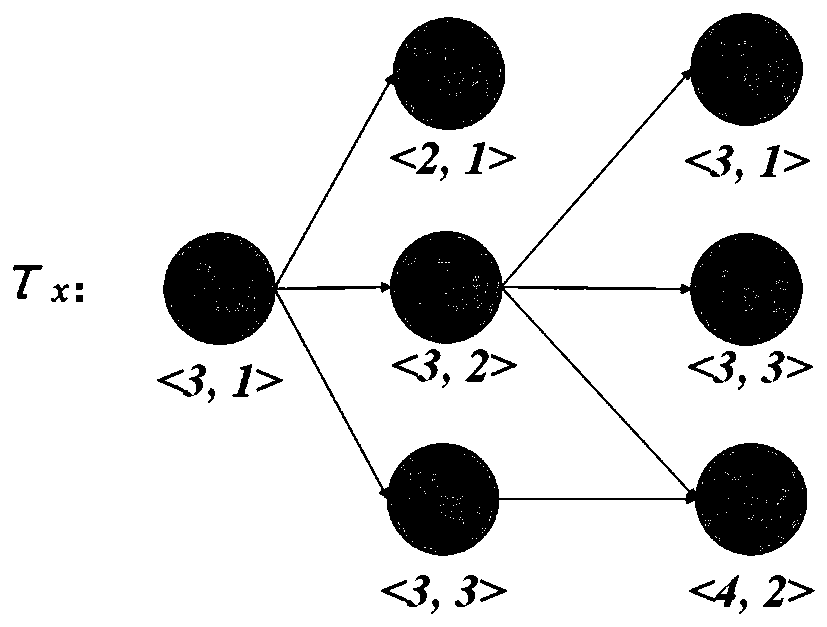

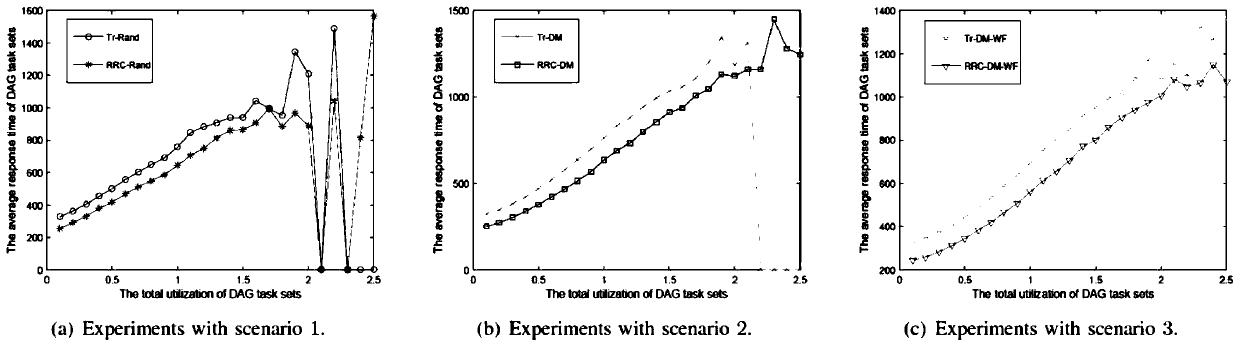

[0051] combined with Figures 1 to 4 , the implementation of the interference analysis method between DAG real-time tasks based on partition scheduling on the multi-core processor of the present invention is described as follows:

[0052] The invention discusses the response time analysis of preemptive DAG tasks on multi-processors under fixed priority division scheduling. Tasks are assigned to different processors for execution in advance, and the tasks can only be executed on the assigned processors. First, we analyze and demonstrate the factors affecting path execution in the target DAG task. On this basis, a parallel structure for recalculating interference is proposed and proved. This structure provides good guidance for priority assignment and partitioning of nodes to processors. Finally, we propose a new analysis strategy to improve the performance of WCRT analysis by considering the parallel structure.

[0053] 1. DAG task model

[0054] Assume that a task set t={t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More