Hardware system reliability verification method

A hardware system, reliability technology, applied in hardware monitoring, instrumentation, error detection/correction, etc., can solve problems such as reliability and safety cannot be guaranteed, weapon system failure, economic loss, etc., to alleviate system complexity, The effect of improving software quality and optimizing hardware structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0046] An embodiment of the present disclosure provides a hardware system reliability verification method.

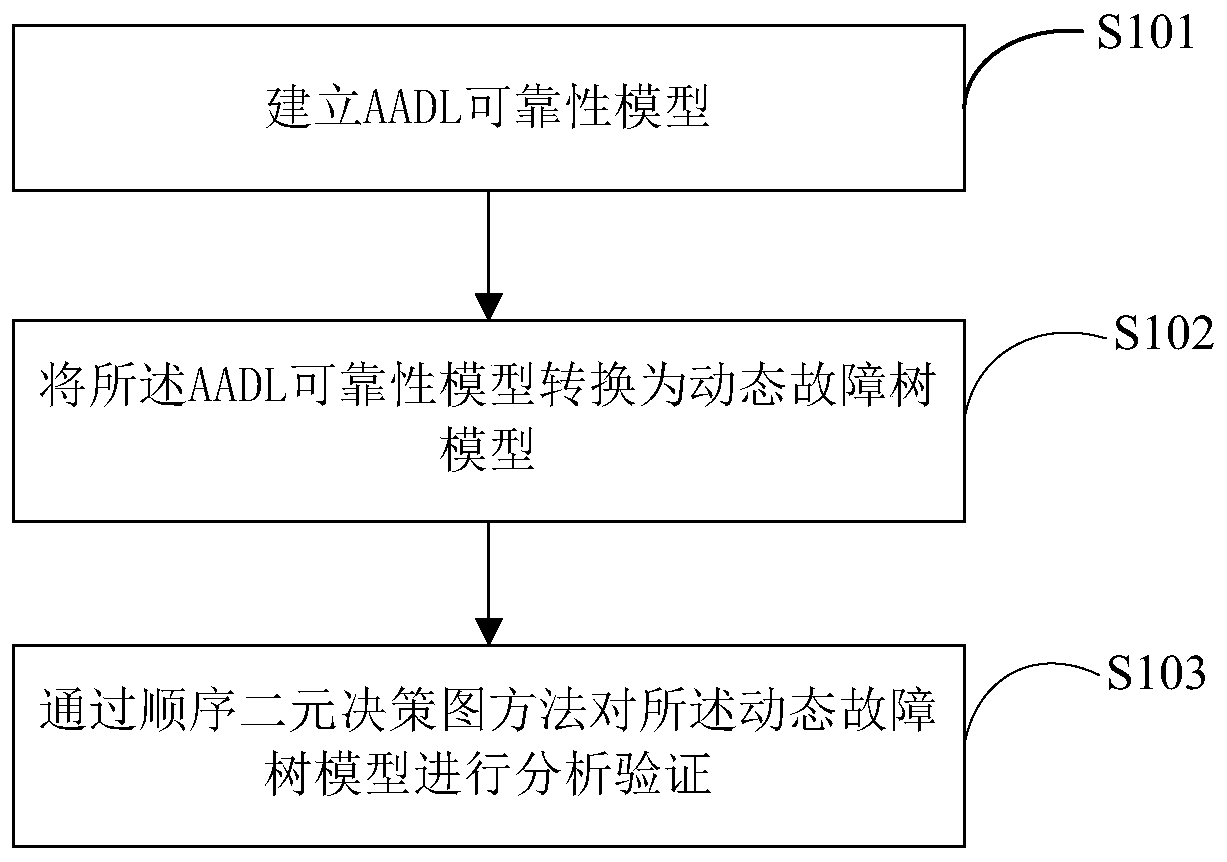

[0047] figure 1 It is a schematic flowchart of a hardware system reliability verification method according to an exemplary embodiment.

[0048] In some embodiments, a hardware system reliability verification method includes:

[0049] Step S101, establishing an AADL reliability model;

[0050] Among them, AADL (Architecture Analysis and Design Language, Architecture Analysis and Design Language) is an architectural design and analysis language that describes the hardware and software structure of a real-time system, and has been maturely used in the verification of hardware system-related issues. This technology is based on AADL conducts reliability verification on hardware systems.

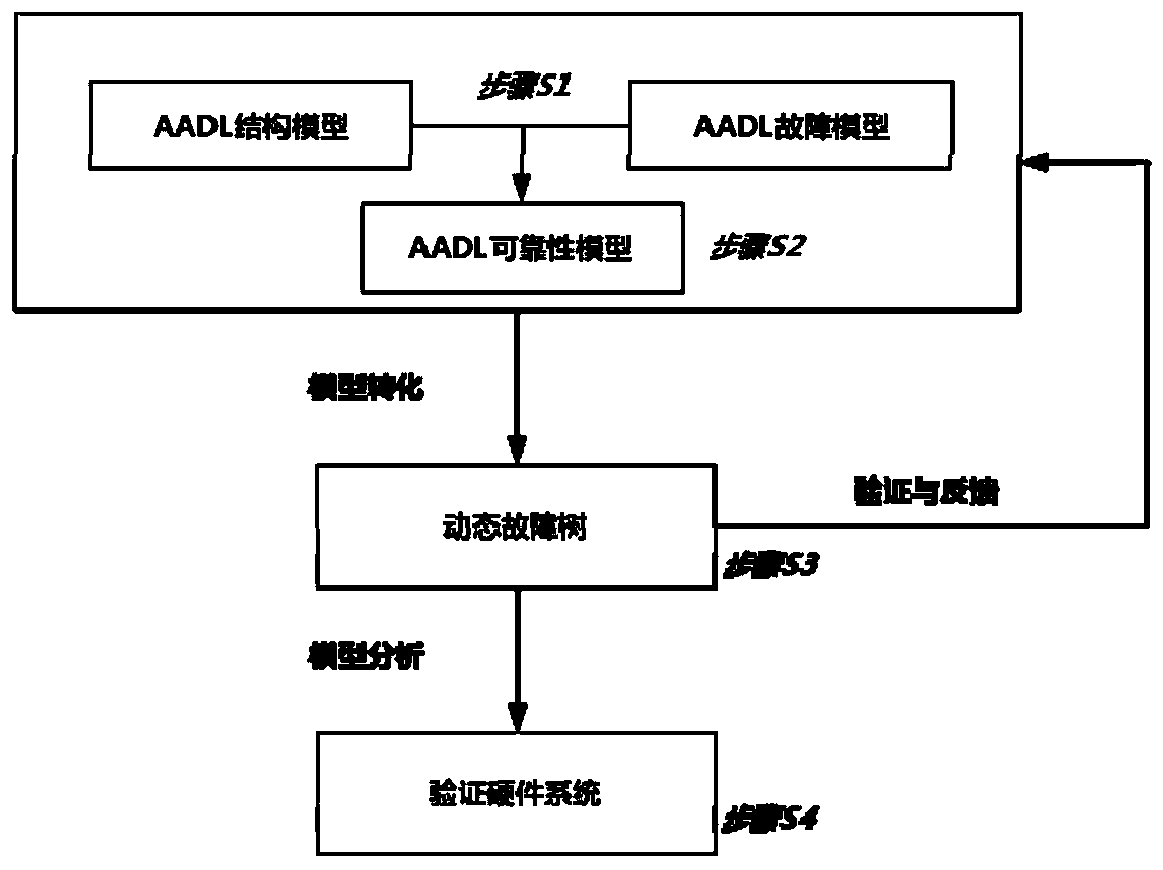

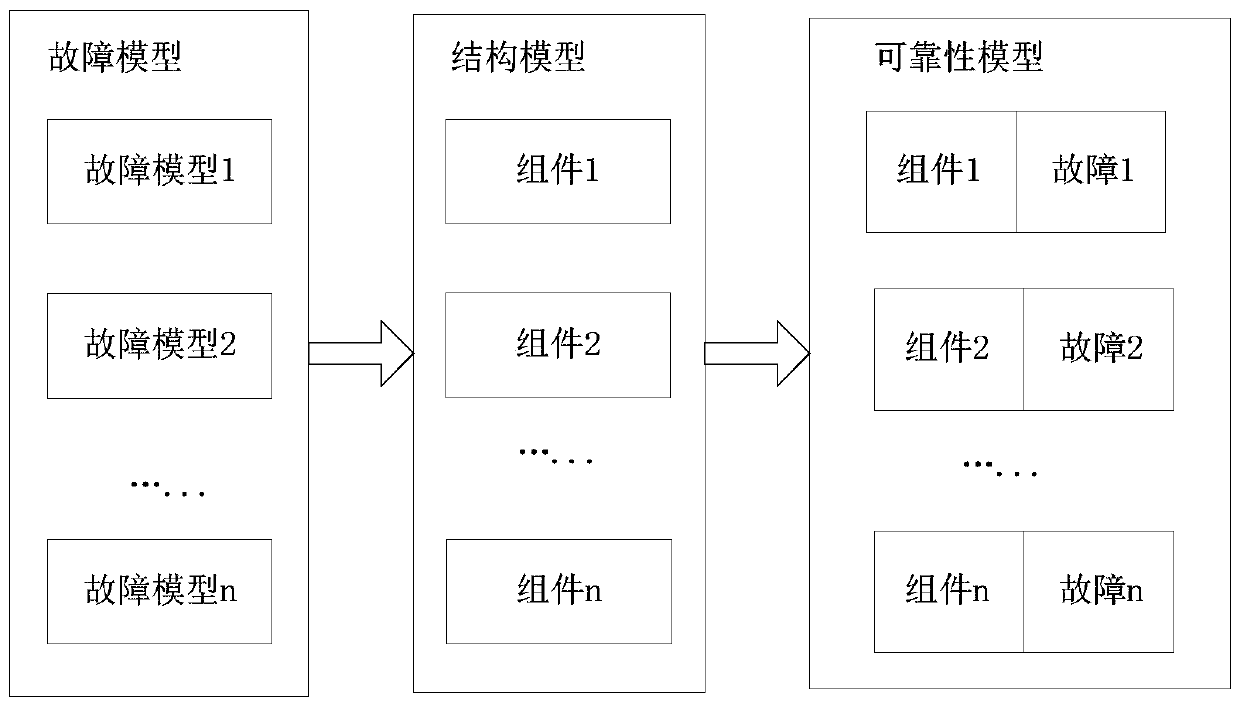

[0051] image 3 It is a schematic diagram showing the construction of a reliability model according to an exemplary embodiment.

[0052] Such as image 3 As shown, the construction me...

Embodiment 2

[0135] An embodiment of the present disclosure provides a hardware system reliability verification system.

[0136] Figure 5 It is a schematic structural diagram of a hardware system reliability verification system shown according to an exemplary embodiment;

[0137] In some optional embodiments, a hardware system reliability verification system includes:

[0138] S501 building blocks for establishing AADL reliability models;

[0139] S502 conversion module, for converting the AADL reliability model into a dynamic fault tree model;

[0140] The S503 verification module is used to analyze and verify the dynamic fault tree model through the sequential binary decision diagram system.

[0141] Figure 6 It is a structural schematic diagram of a building block shown according to an exemplary embodiment;

[0142] Such as Figure 6 As shown, the building blocks include:

[0143] S501-1 The first building unit is used to establish the AADL structure model and fault model;

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More