Wafer detection method

A detection method and wafer technology, applied in measurement devices, semiconductor/solid-state device testing/measurement, instruments, etc., can solve problems such as the inability to scan effective chips, the inability to calculate the wafer map by the SEM machine, and the large exposure unit. , to avoid a large number of chips not being scanned and inaccurate defect scanning, narrowing the range of scanning units, and improving scanning accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

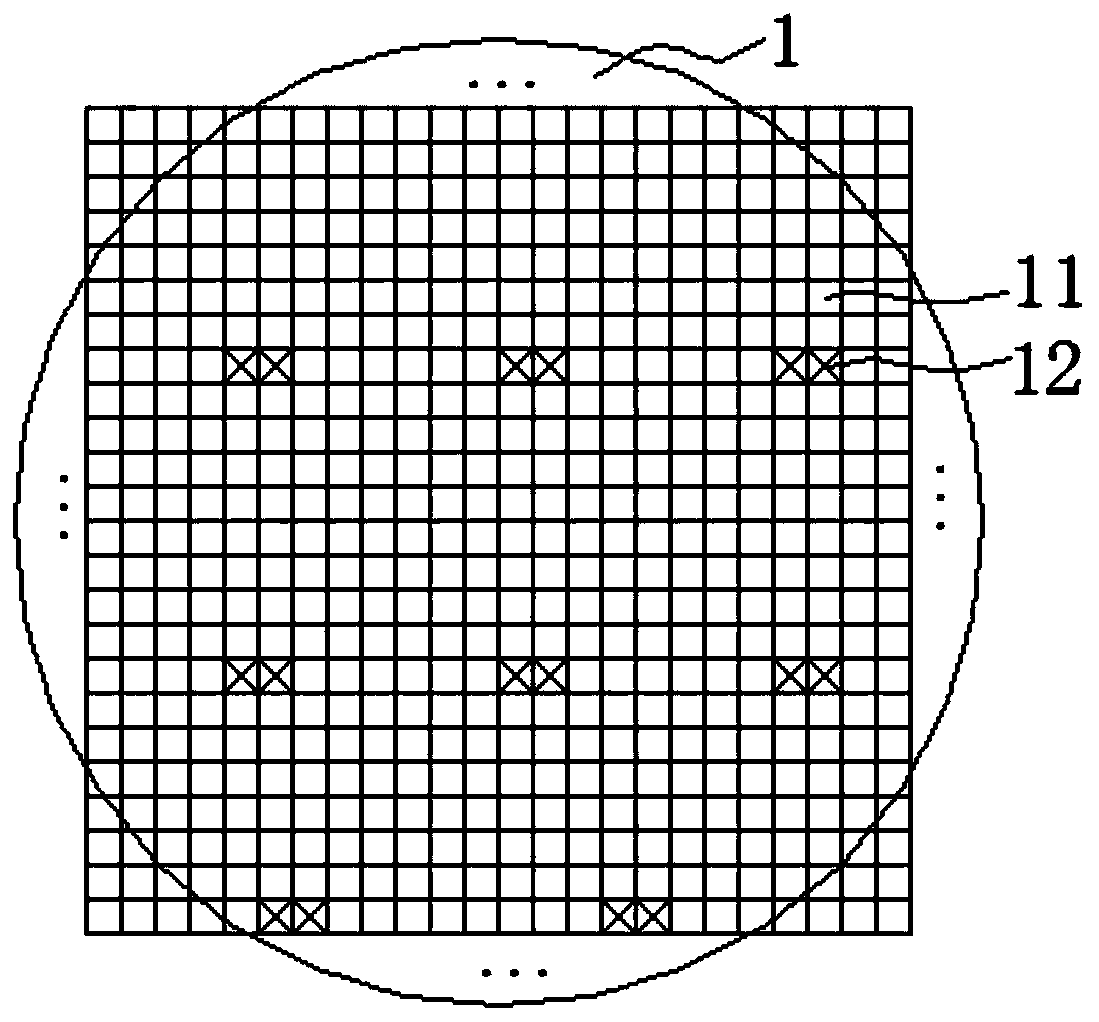

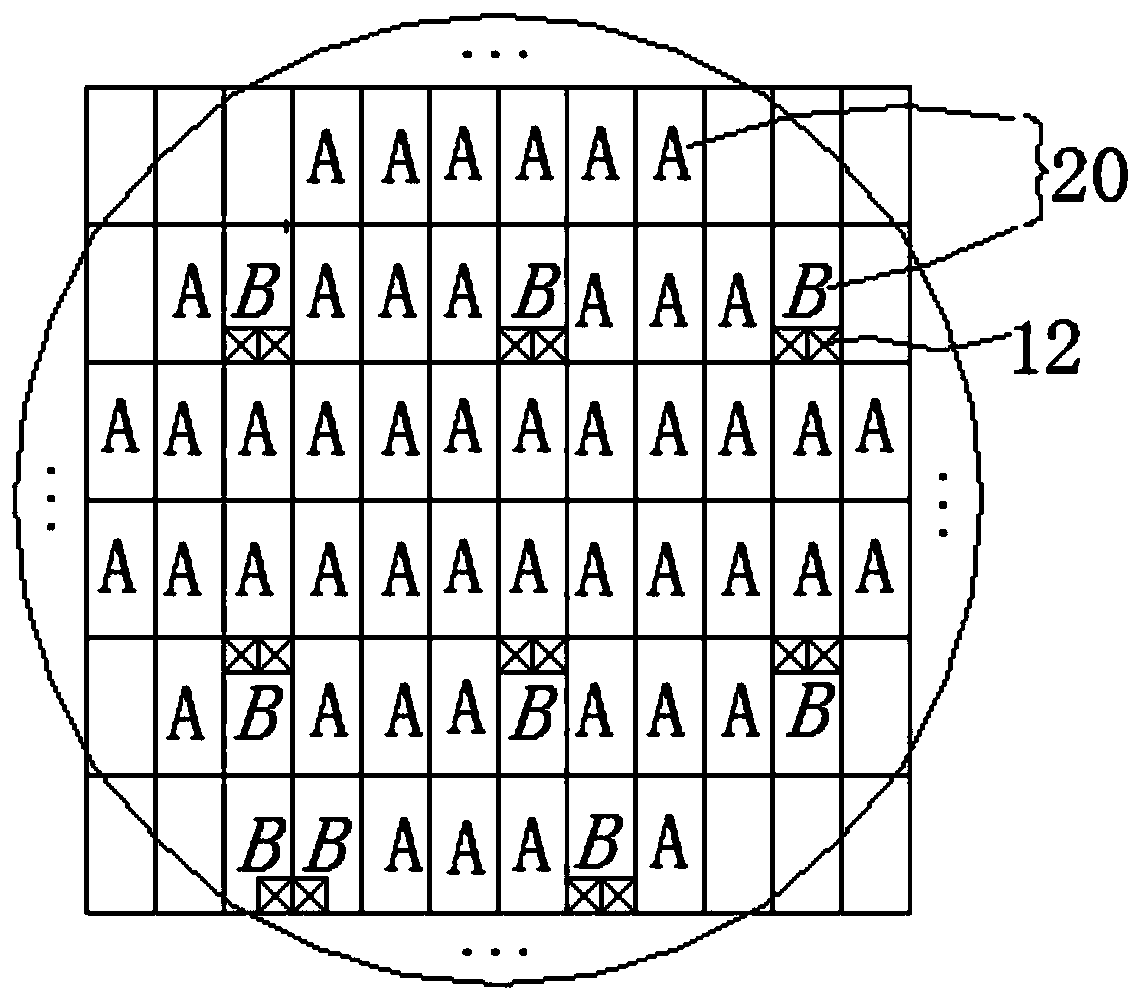

[0032] An embodiment of the present invention provides a wafer inspection method. The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that the drawings are all in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

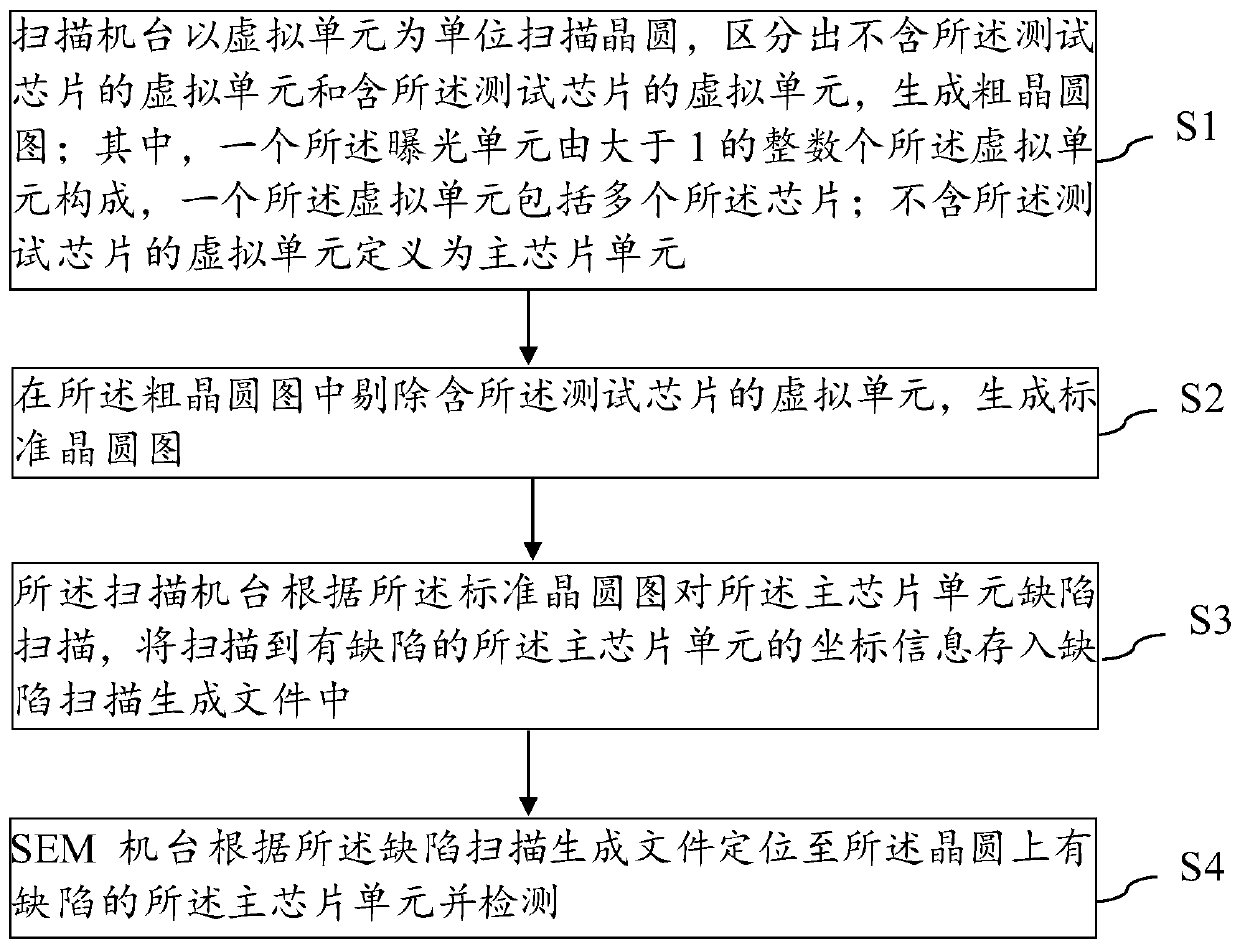

[0033] An embodiment of the present invention provides a wafer inspection method. The chips on the wafer include a main chip and a test chip, and the wafer is formed by repeated exposure by an exposure unit, such as figure 1 shown, including:

[0034] The scanning machine scans the wafer with a virtual unit as a unit, distinguishes a virtual unit not containing the test chip and a virtual unit containing the test chip, and generates a rough w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More