Single event effect suppression structure of solid-state power controller control loop

A single event effect and control loop technology, applied in the direction of output power conversion devices, electrical components, etc., can solve the problems of inability to receive communication instructions, loss of SSPC basic functions, and single event effect protection functions, etc., to achieve suppression of single event effects , to avoid the effect of uncertain output status

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings. It should be noted here that the descriptions of these embodiments are used to help understand the present invention, but are not intended to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

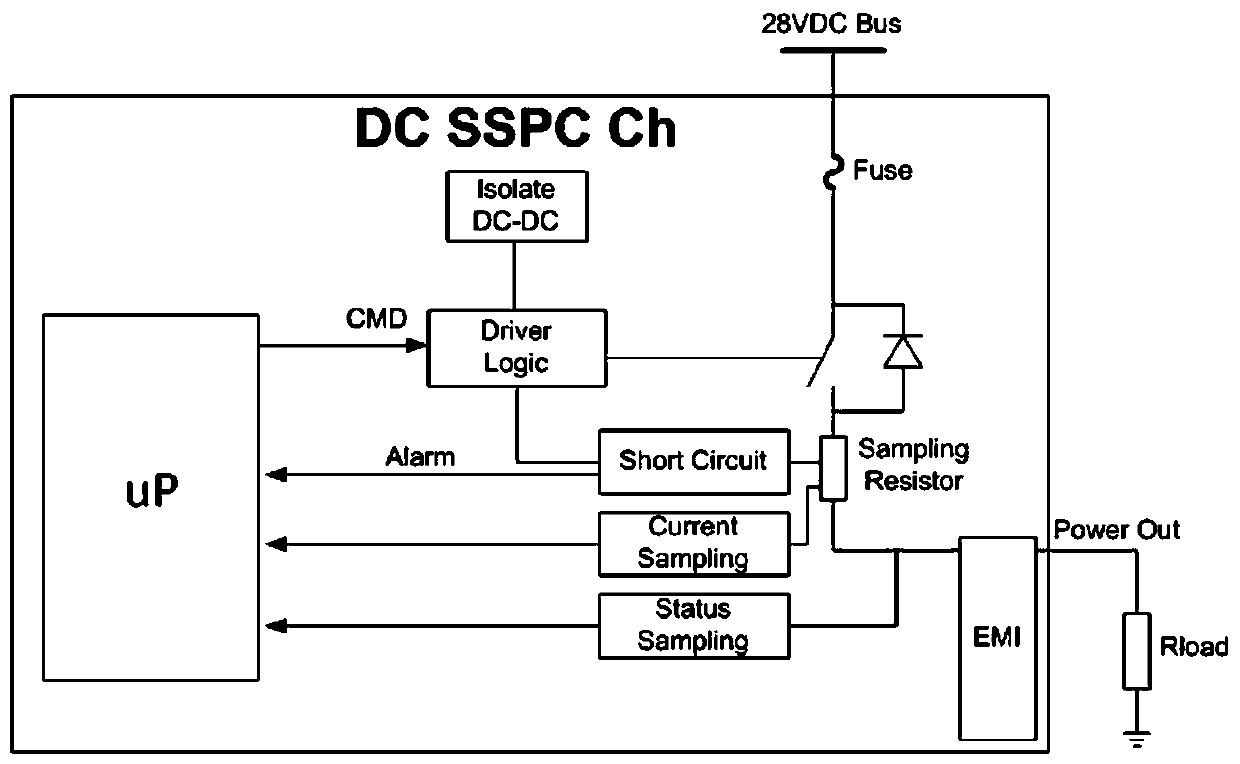

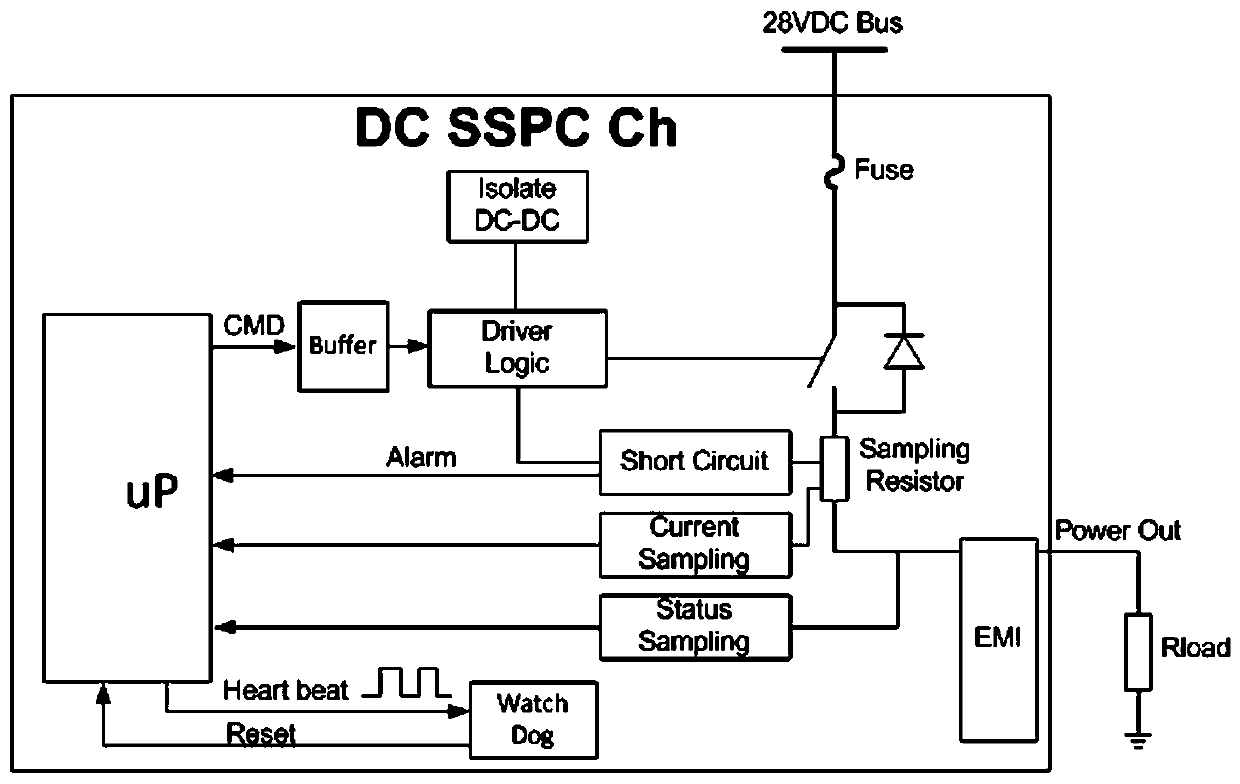

[0028] See Figures 3 to 4 , on the basis of the basic overload, short circuit protection and status reporting of the original SSPC, this patent adds a single event effect protection function. That is to add a buffer circuit between the processor and the power device driver. When the processor is disturbed by the single event effect and works abnormally, the buffer circuit can maintain the state of the last command, so that the load driver will not jump, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More