Chip automatic verification system and method therefor

An automatic verification and chip technology, applied in the field of verification platform, can solve the problems of increasing verification error rate, labor-intensive, time-consuming, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Embodiments of the present invention will be described below in conjunction with related figures. In the drawings, the same symbols represent the same or similar elements or method flows.

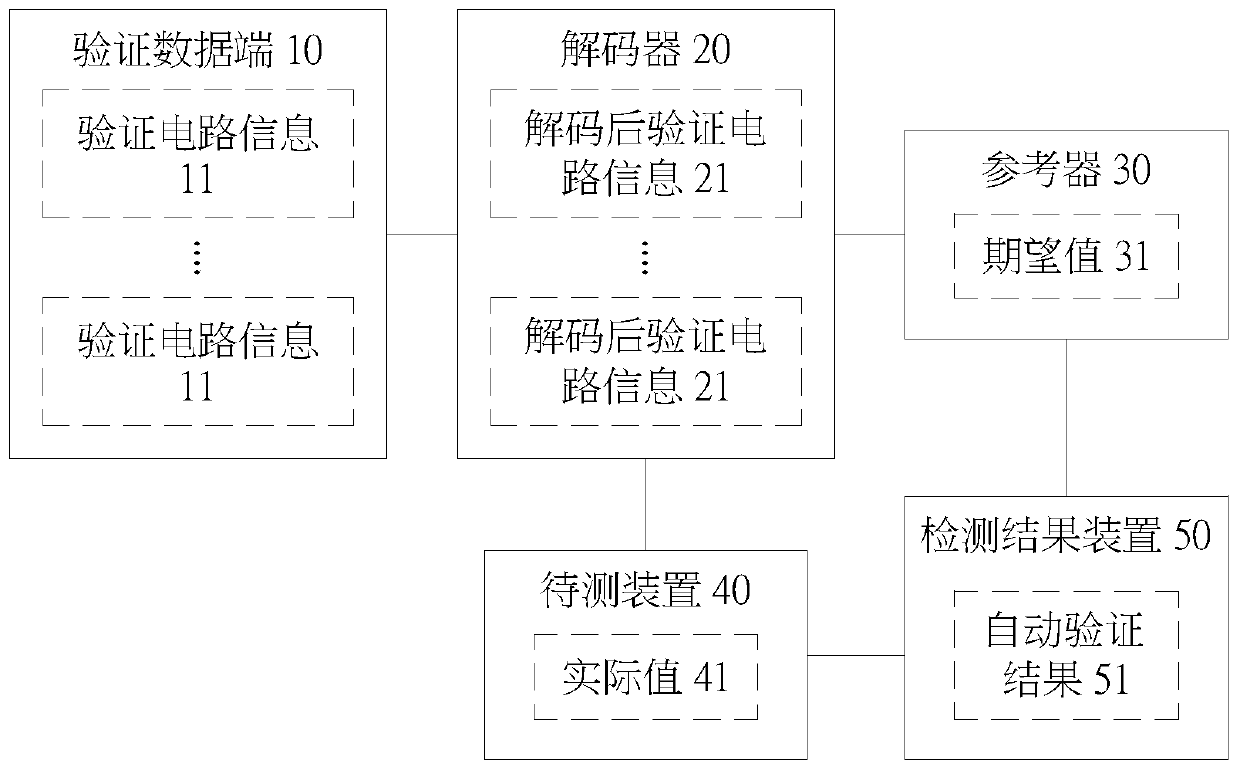

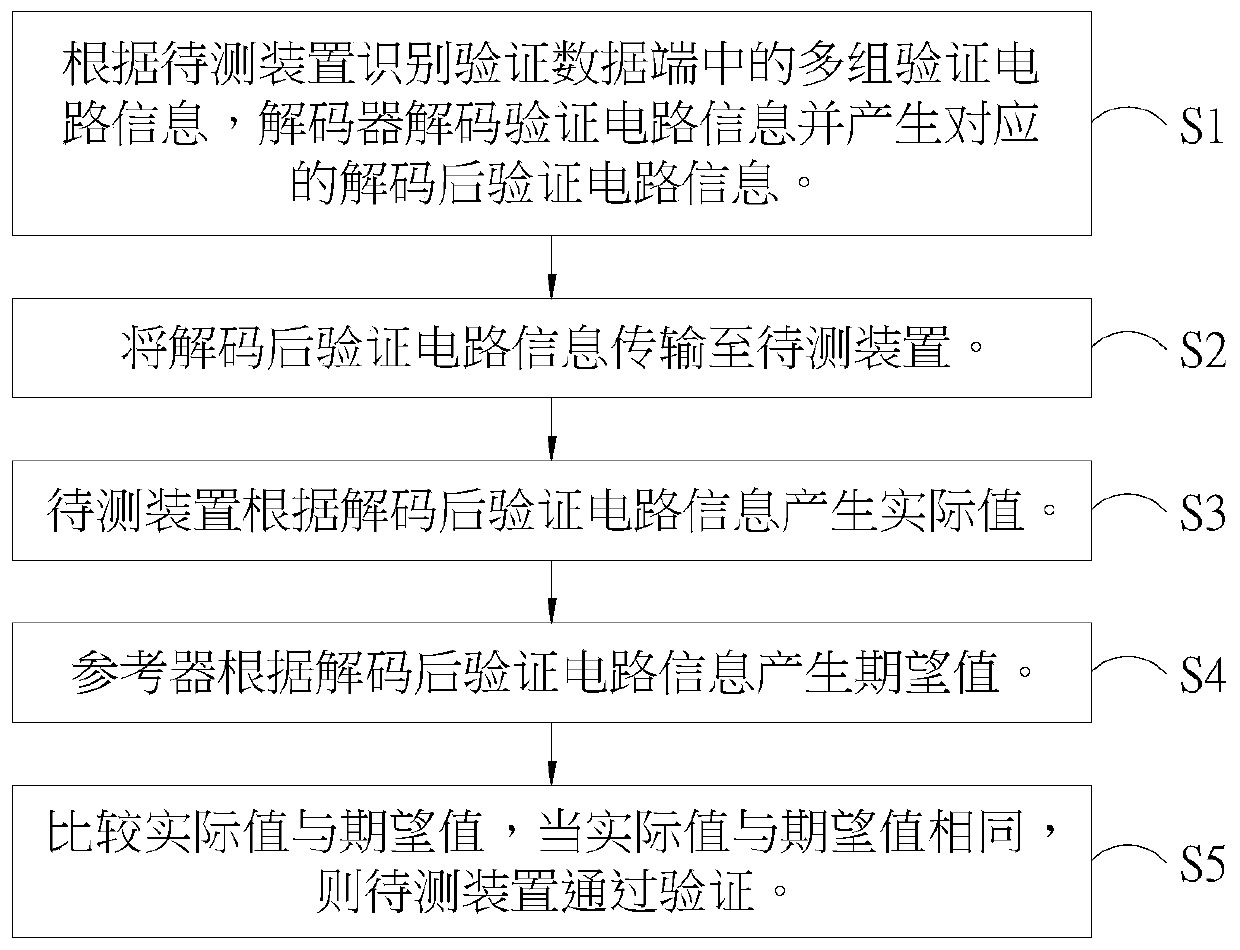

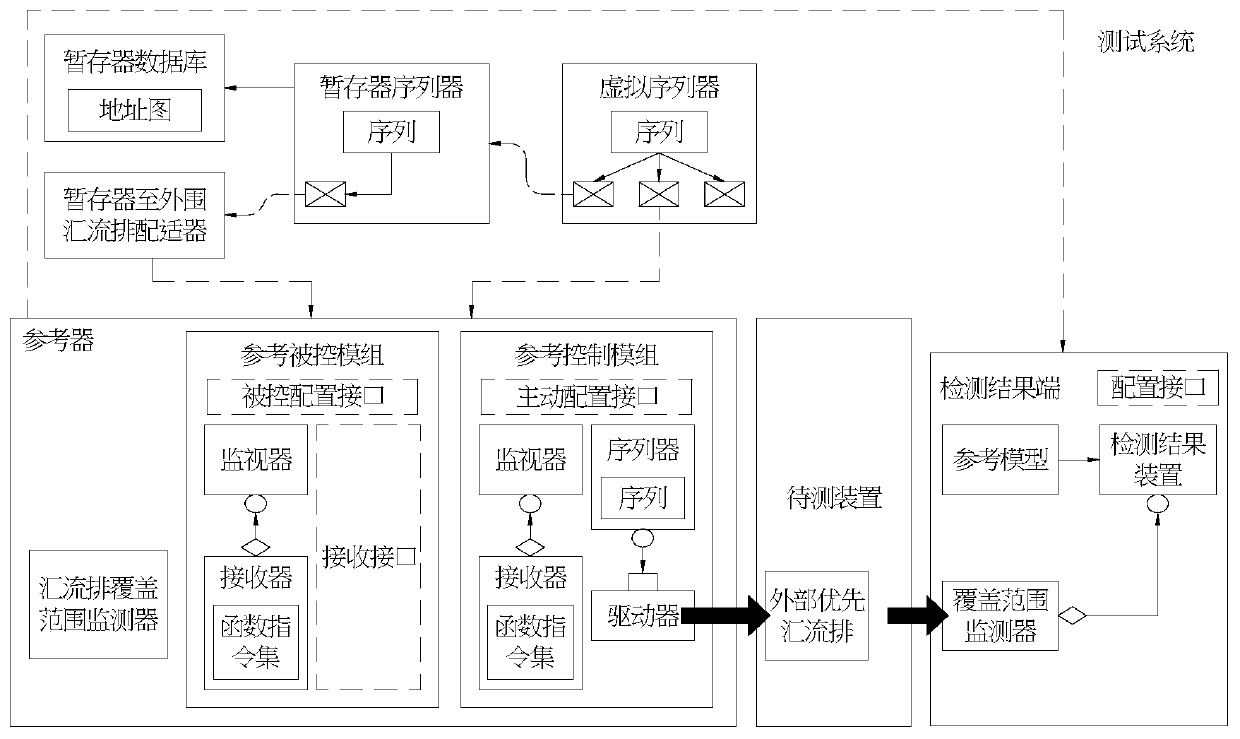

[0038] Please refer to figure 1 , which is an automatic chip verification system for verifying the signal of the device under test, which includes a verification data terminal 10 , a decoder 20 , a reference device 30 and a test result device 50 . The verification data terminal 10 stores multiple sets of verification circuit information 11 . The decoder 20 is connected to the verification data terminal 10, and decoded according to at least one verification circuit information 11 to generate at least one corresponding decoded verification circuit information 21. The decoder 20 is connected to the device under test 40, and the device under test 40 is verified according to the decoded verification circuit information. The information 21 produces an actual value 41 . The reference dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More