Three-dimensional semiconductor memory device

A storage device and semiconductor technology, applied in the direction of semiconductor devices, static memory, electric solid-state devices, etc., can solve problems such as integration setting restrictions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

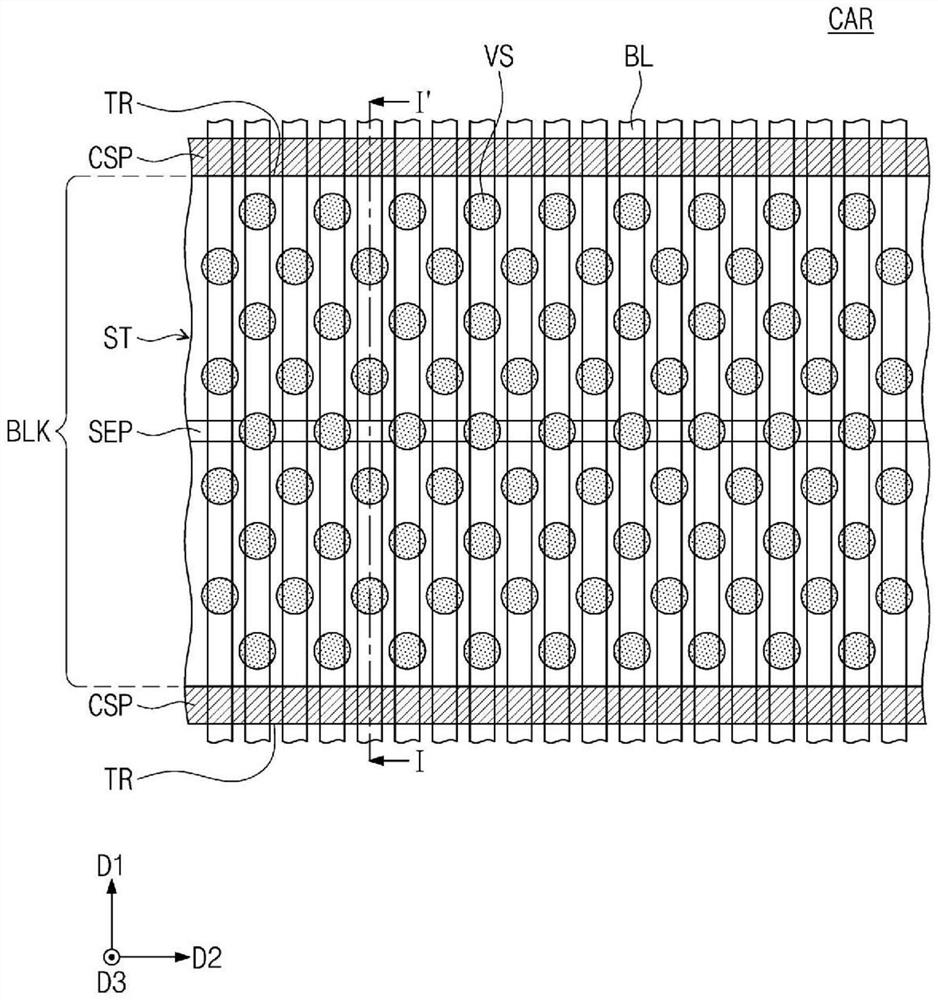

[0044] The upper semiconductor pattern USP may have a tube shape with its bottom closed. The upper semiconductor pattern USP may have a bottom surface in direct physical contact with the lower semiconductor pattern LSP. The upper semiconductor pattern USP may have an interior at least partially filled with the buried insulation pattern VI. Each of the upper semiconductor pattern USP and the buried insulation pattern VI may have a diameter that gradually decreases as the distance from the substrate 100 decreases. In some embodiments, the diameter may decrease monotonically with decreasing distance from the substrate 100 . According to some example embodiments of the inventive concepts, the lower semiconductor pattern LSP and the upper semiconductor pattern USP may serve as channels of a three-dimensional semiconductor memory device.

[0045] For example, the lower semiconductor pattern LSP and the upper semiconductor pattern USP may include silicon (Si), germanium (Ge), or a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More