Multi-channel high-speed data alignment method and multi-channel high-speed data alignment device

A high-speed data, multi-channel technology, applied in the field of communication, can solve problems such as data transmission delay and jitter, complex circuit design, and impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

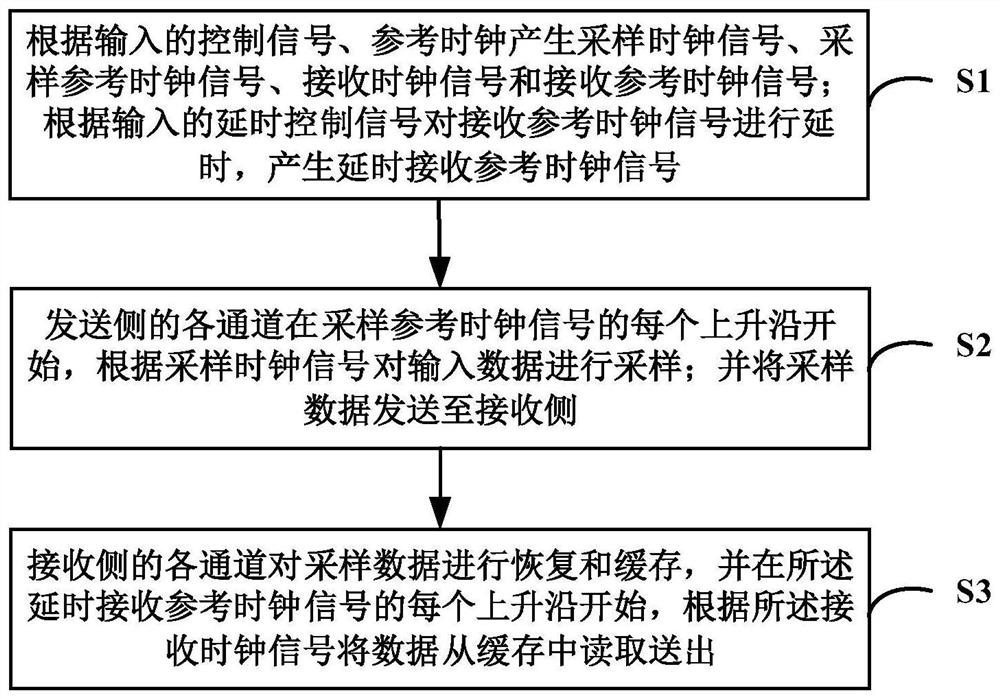

[0048] see figure 1 As shown, this embodiment provides a method for multi-channel high-speed data alignment, the method includes the following steps:

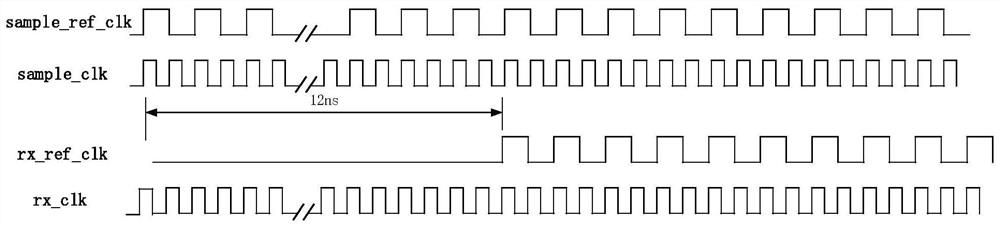

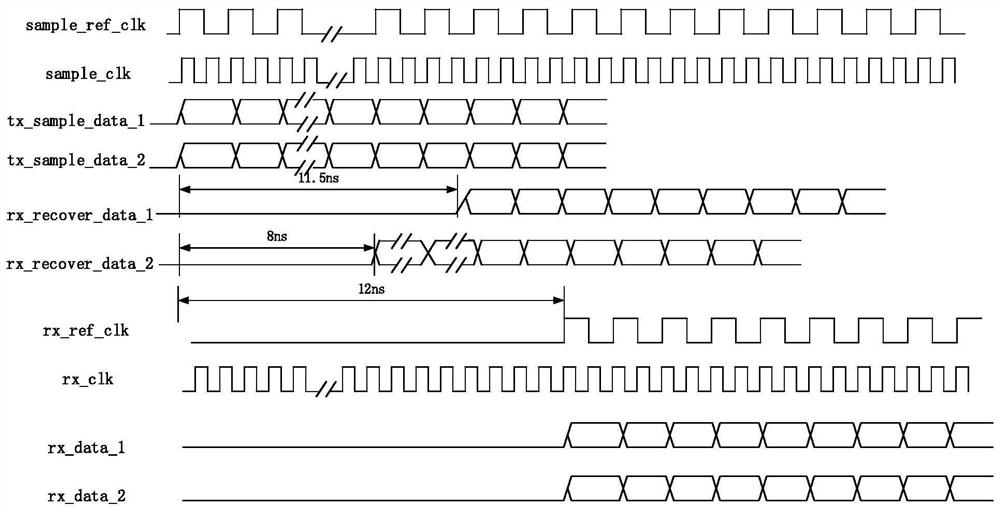

[0049] S1. Generate sampling clock signal (sample_clk), sampling reference clock signal (sample_ref_clk), receiving clock signal (rx_clk) and receiving reference clock signal (rx_ref_clk') according to the input control signal and reference clock (ref_clk); according to the input delay The control signal delays rx_ref_clk' to generate a delayed reception reference clock signal (rx_ref_clk). In practical applications, after the device is started, it will continue to generate the above signals.

[0050] S2. Each channel on the sending side starts at each rising edge of sample_ref_clk, samples input data (such as tx_data_1, tx_data_2, ..., tx_data_n) according to sample_clk; and samples the data (such as tx_sample_data_1, tx_sample_data_2, ..., tx_sample_data_n) ) to the receiving side. In practical applications, each channel h...

Embodiment 2

[0069] see Figure 4 As shown, based on the same inventive concept, an embodiment of the present invention also provides a multi-channel high-speed data alignment device, which includes a control side, a sending side, and a receiving side.

[0070] The control side includes a signal generation module and a signal delay module. Among them, the signal generation module is used to: generate a sampling clock signal (sample_clk), a sampling reference clock signal (sample_ref_clk), a receiving clock signal (rx_clk) and a receiving reference clock signal (rx_ref_clk') according to the input control signal and the reference clock (ref_clk) ). The signal delay module is configured to: delay rx_ref_clk' according to the input delay control signal to generate a delayed reception reference clock signal (rx_ref_clk). In practical applications, after the device is started, it will continue to generate the above signals.

[0071] The sending side includes multiple groups of data sampling ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com