Equal-probability DOE limit simulation method for PCIE link design, program and medium

A simulation method and equal-probability technology, applied in the direction of probabilistic CAD, stochastic CAD, computer-aided design, etc., can solve the problems such as the inability to guarantee the reliability of the results and the inability to guarantee the probability, and achieve the effect of guaranteeing the results and ensuring the correctness.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

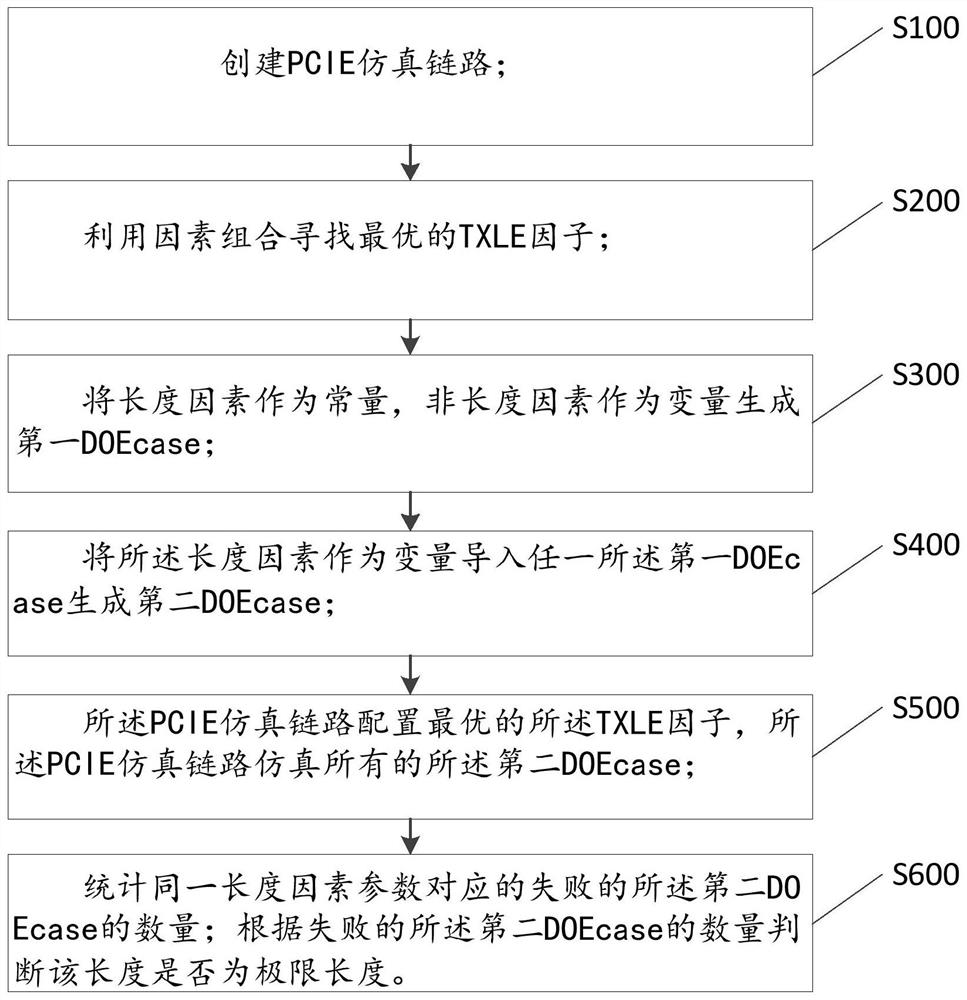

[0038] refer to figure 1 As shown, the present invention provides the present invention provides a kind of PCIE link design with equal probability DOE limit emulation method, comprises following steps:

[0039] S100, create a PCIE simulation link; in the specific implementation process, the configuration of the PCIE simulation link includes SSD simulation components, SSD channel simulation components, PCB channel simulation components and CPU simulation components; the SSD simulation components configure SSD packaging factors Parameters, the parameters of the SSD channel simulation component configuration SSD channel factors, the parameters of the PCB channel simulation component configuration PCB channel factors, the parameters of the CPU simulation component configuration CPU packaging routing factors, the parameter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com