Block floating point computations using reduced bit-width vectors

A block floating-point and vector technology, which is applied in calculations using number system representations, calculations using non-contact manufacturing equipment, calculations, etc., can solve problems such as reduction and adverse effects on accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

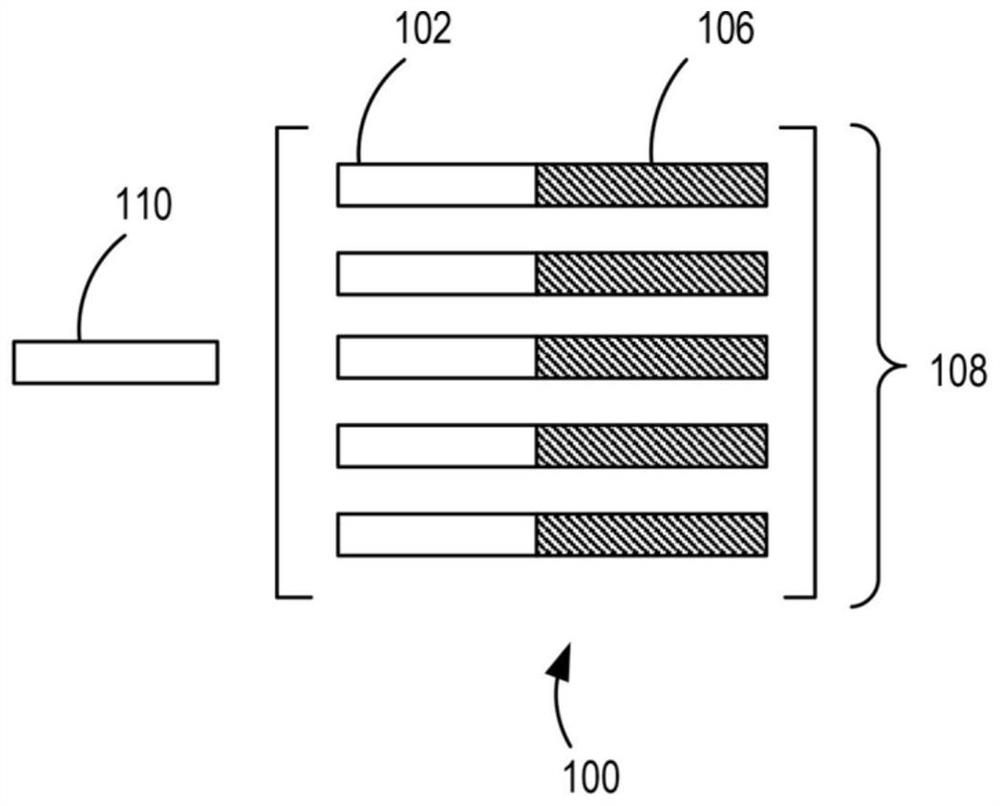

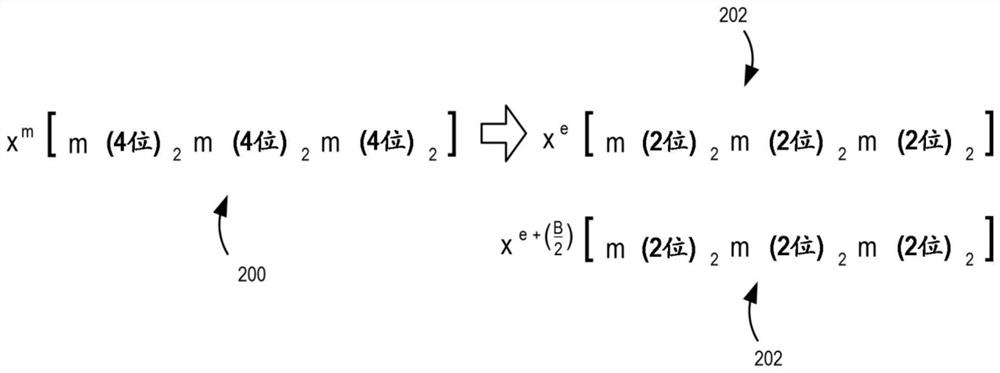

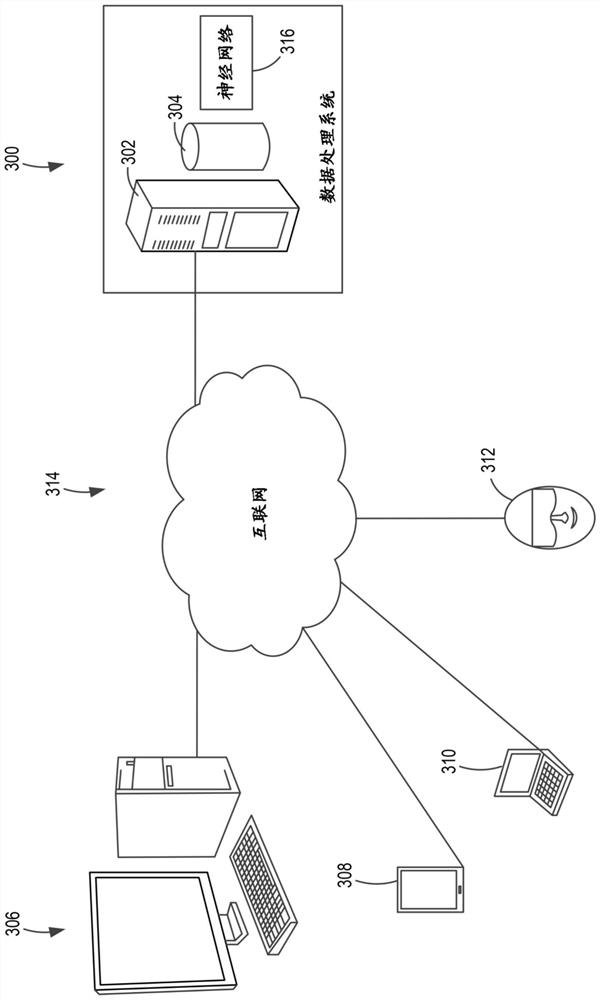

[0015] Computing devices and methods described herein are configured to perform block floating point calculations using reduced bit width vectors. For example, a block floating-point vector is broken into multiple smaller bit-width block floating-point vectors to perform operations on. Thereafter, the higher bit-width block floating-point vector is constructed by combining the results of operations performed on the smaller bit-width block floating-point vector. This precise fusion of block floating point numbers reduces the computational burden while increasing accuracy by allowing high precision mathematical operations to be performed using low precision hardware (eg, low precision hardware accelerators).

[0016] According to various examples of the present disclosure, neural networks, such as deep neural networks (DNNs), can be trained and operated more efficiently using smaller bit-width block floating-point vectors that allow High precision arithmetic on the precision bl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More