Programming method capable of reducing programming interference of memory cell difficult to program

A technology of storage unit and programming method, which is applied in the field of memory, to achieve the effect of reducing the number of programming interference and transmission interference, novel design and strong practicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

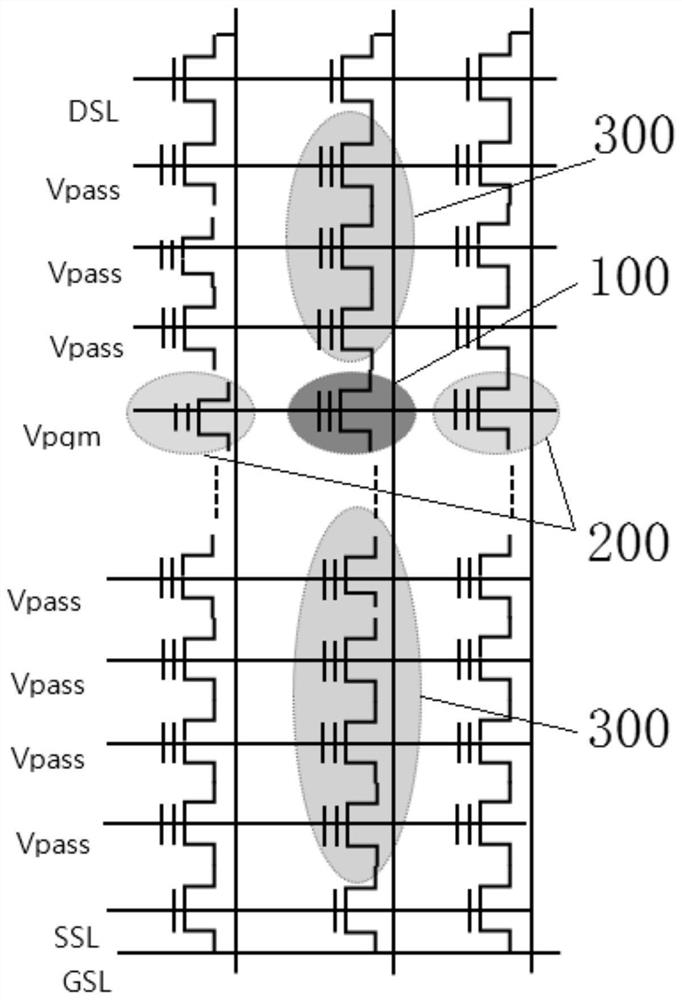

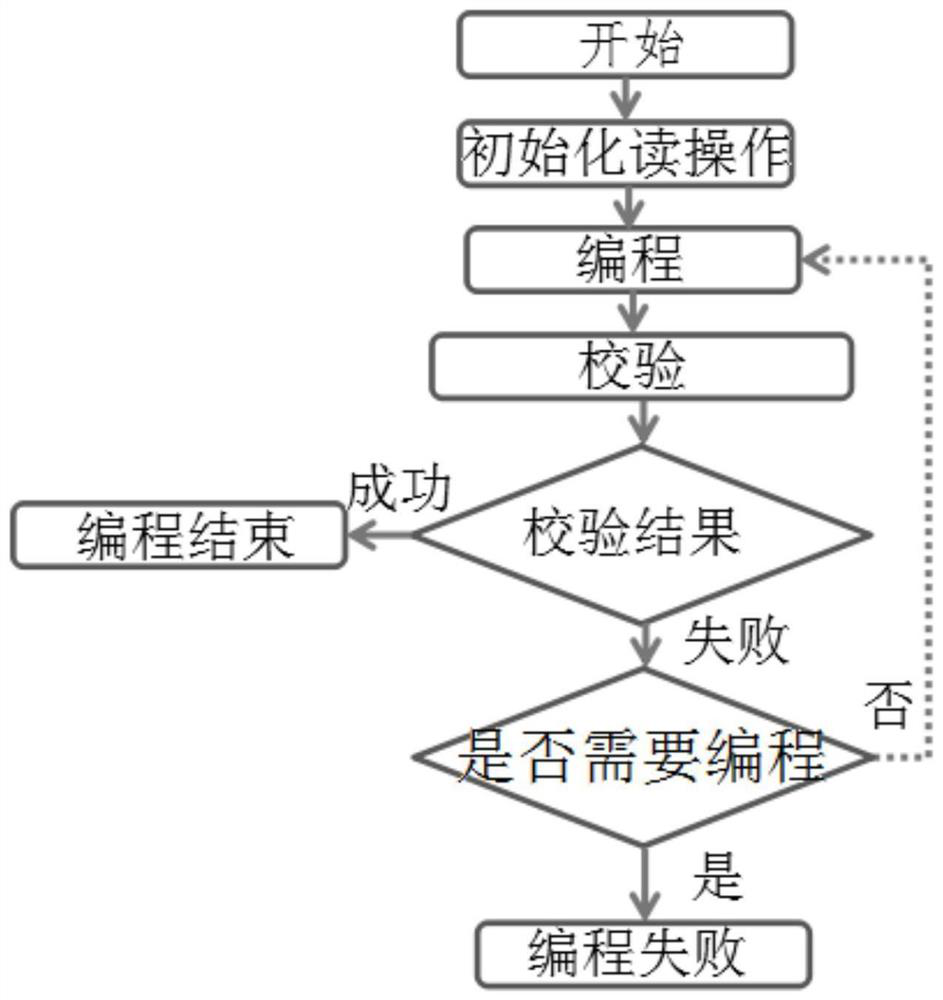

[0049] Step S0: perform an initial read operation on the storage area of the NAND FLASH, set the transmission voltage to 6V; set the preset number of times threshold to 3;

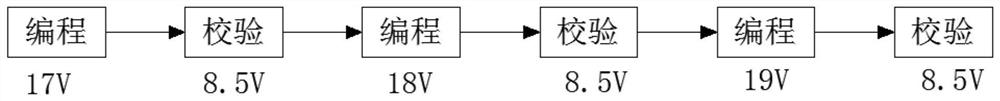

[0050] Step S1, using a programming voltage V of 17V pgm , program the memory cells of the storage area with a transmission voltage V of 8.5V pass applied to memory cells in a different row than the programmed memory cells in the memory region;

[0051] Step S2, using the first verification voltage of 0.8V to perform the first verification operation on the programmed memory cells, if the verification is successful, then go to step S3; if the verification fails, go back to step S1;

[0052] Step S3, use the second verification voltage of 1V to perform the second verification operation on the programmed memory cells, if the verification is successful, then end; if the verification fails, then enter step S4;

[0053] Step S4, increase the programming voltage and return to step S1.

[0054] In step S5, wh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More