Patents

Literature

36results about How to "Program disturb" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

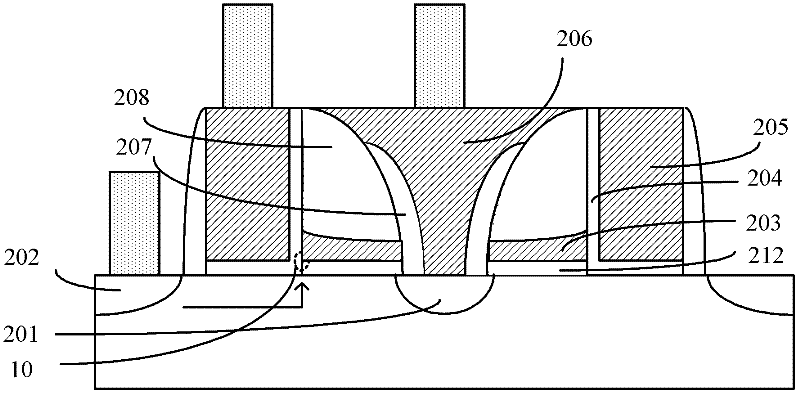

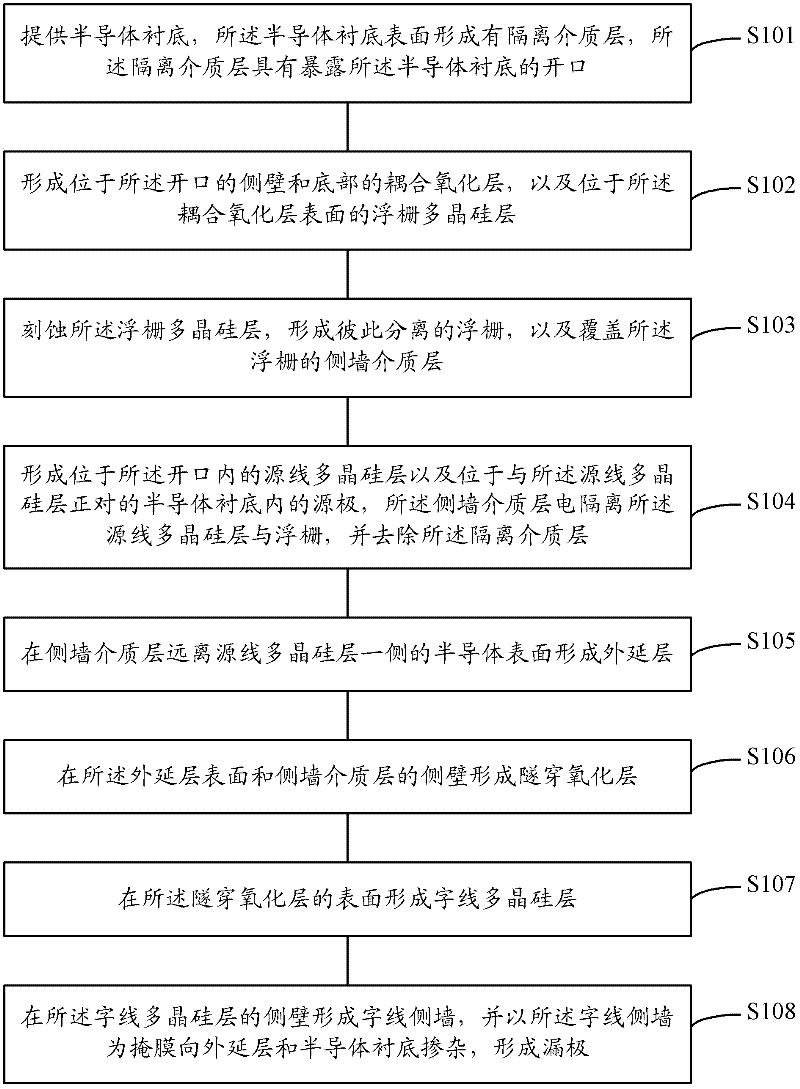

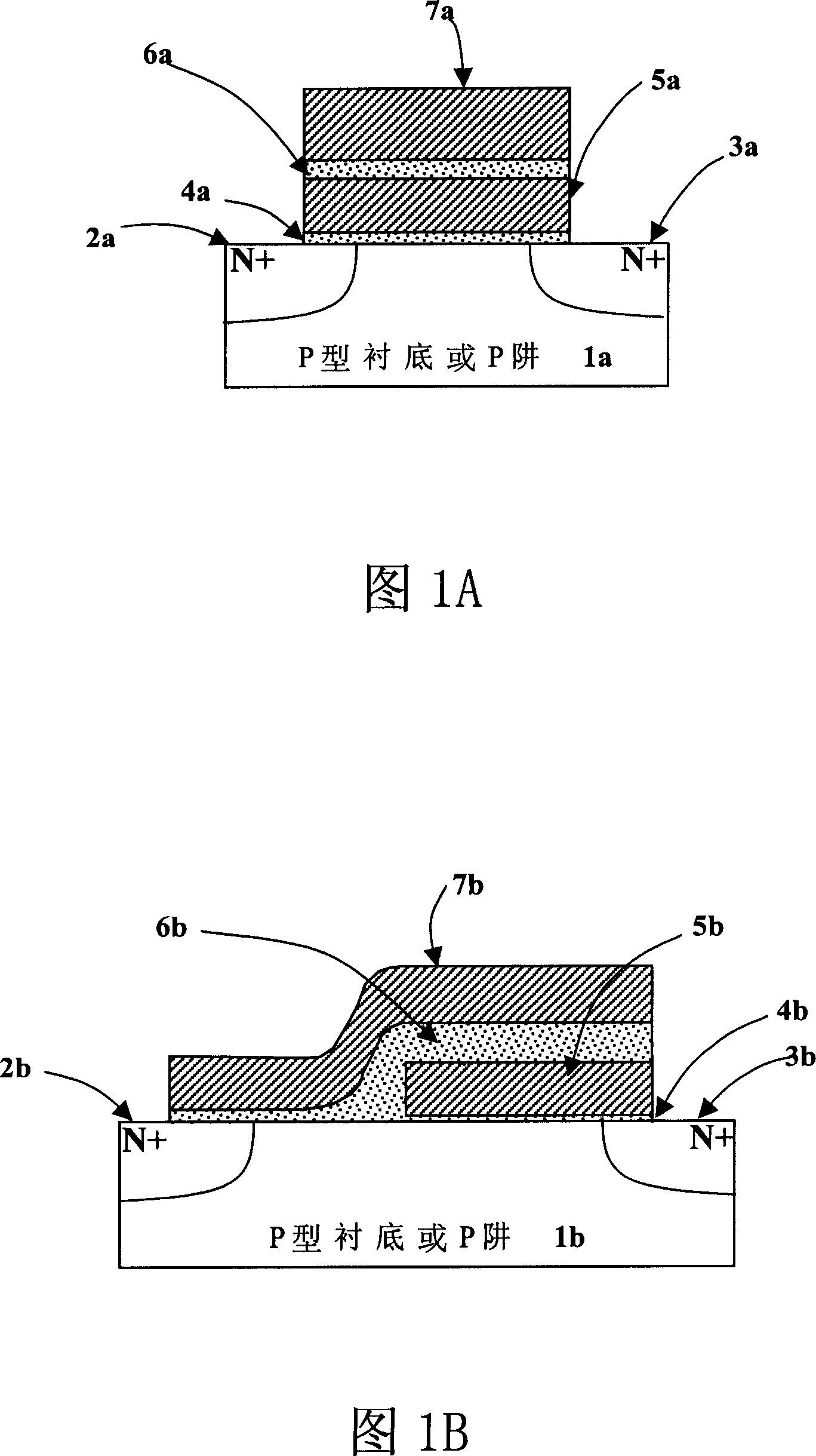

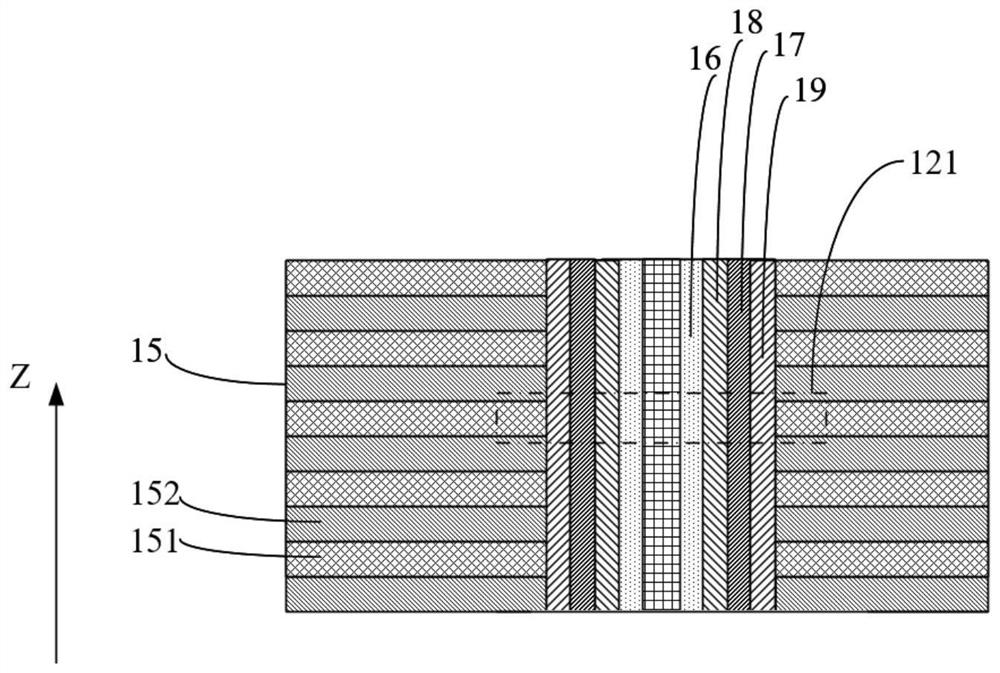

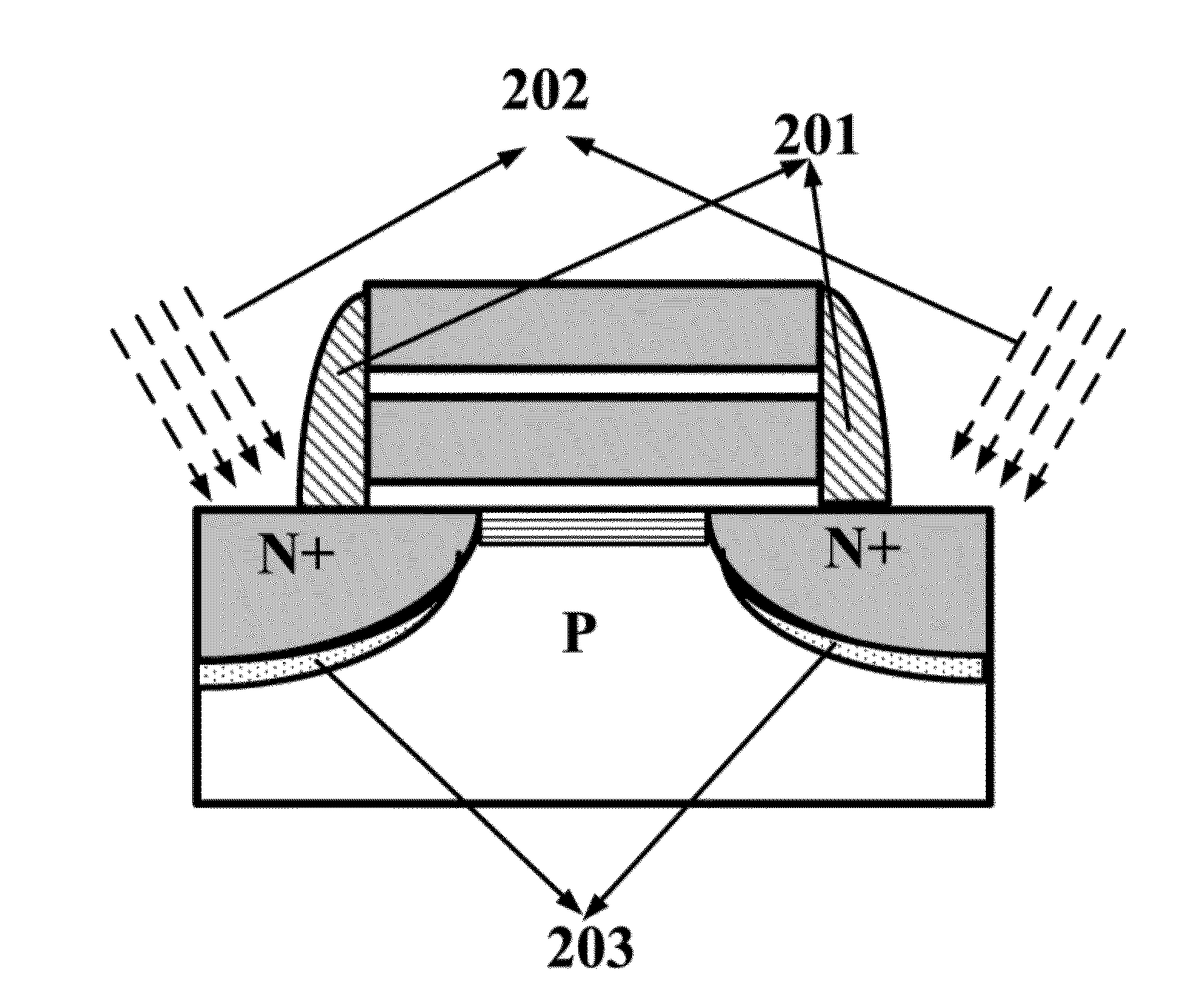

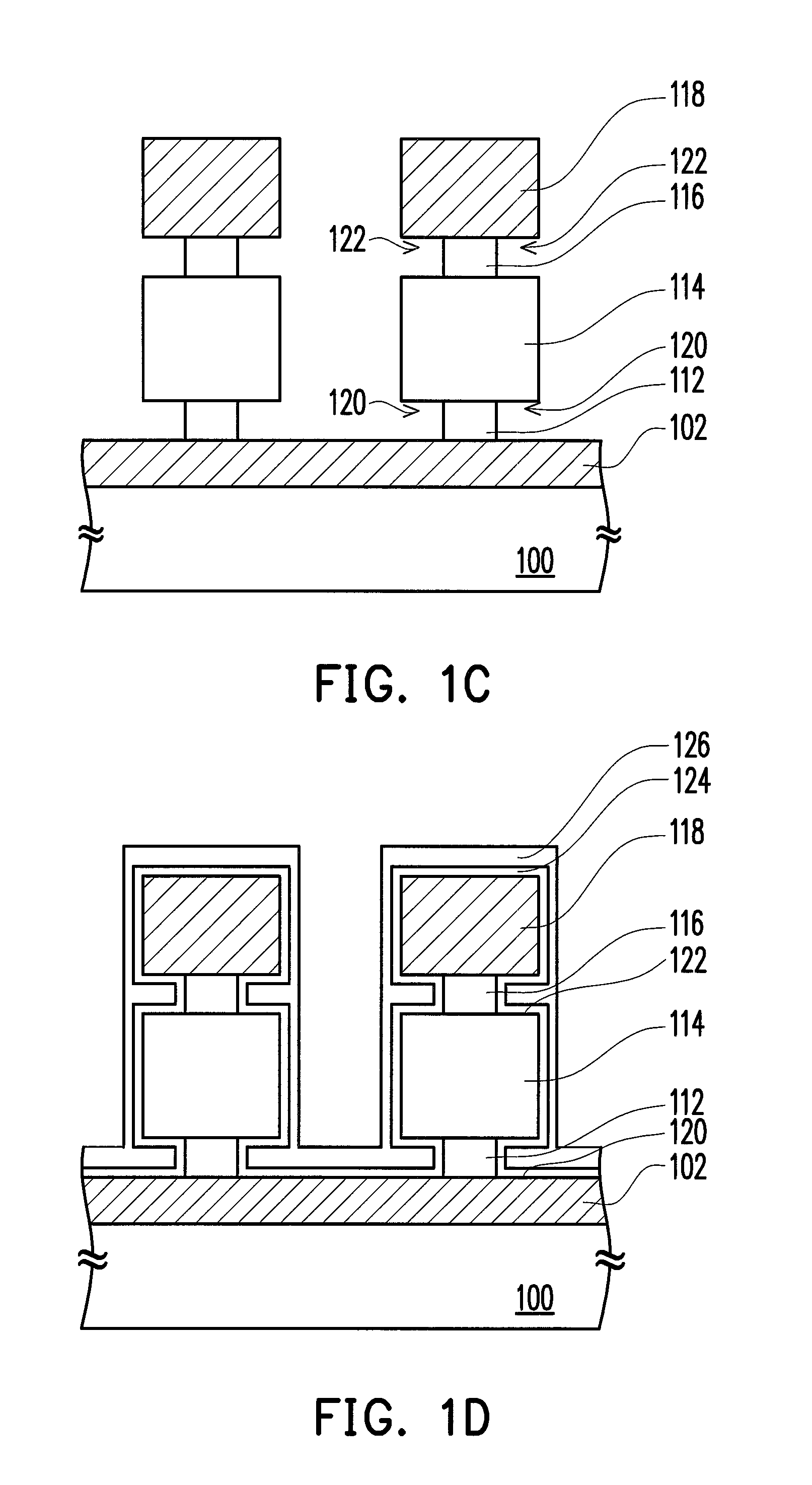

Split-gate flash memory unit and forming method thereof

ActiveCN102347281AReduce height differenceReduce voltageSolid-state devicesSemiconductor/solid-state device manufacturingCouplingMiniaturization

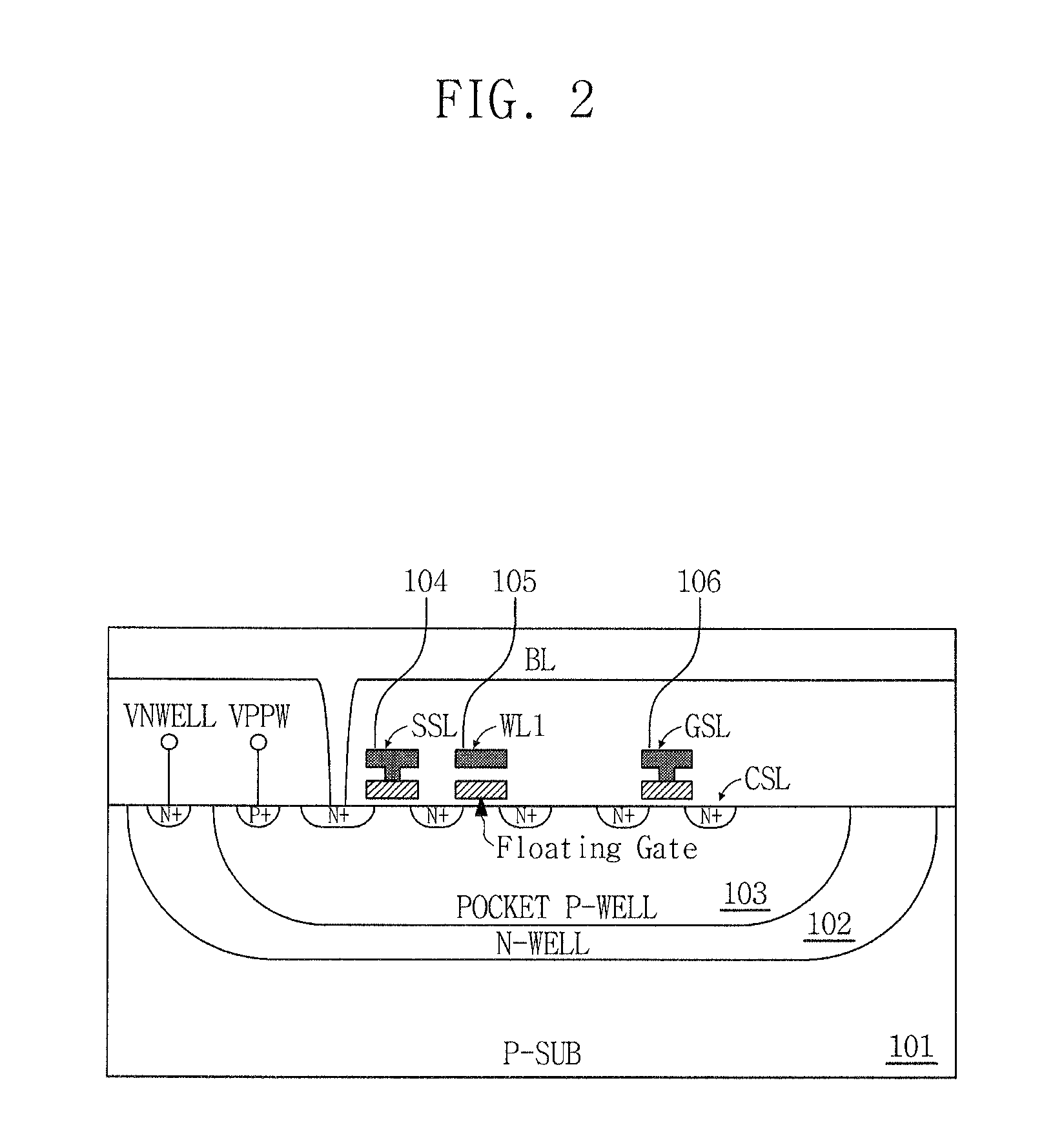

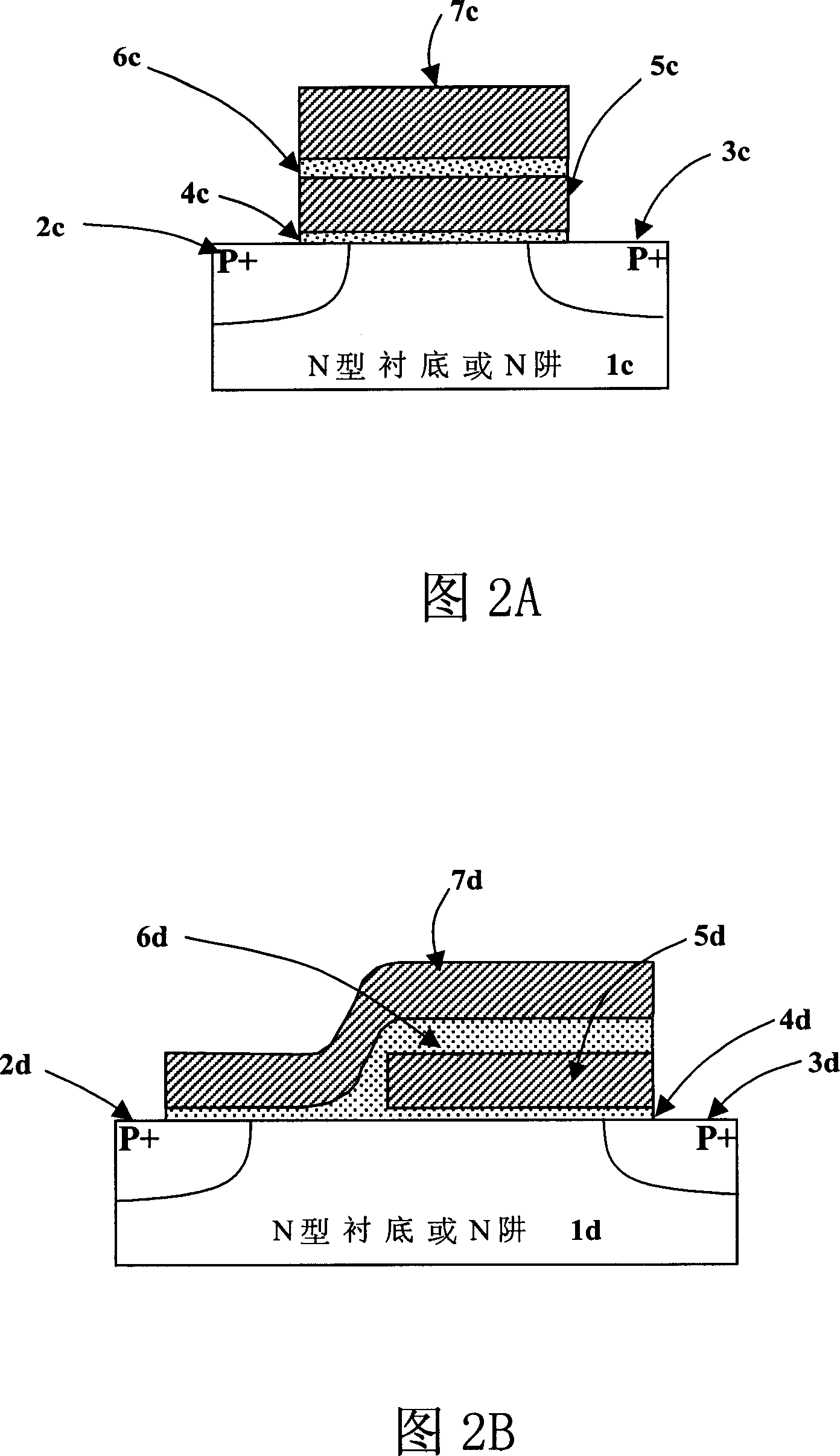

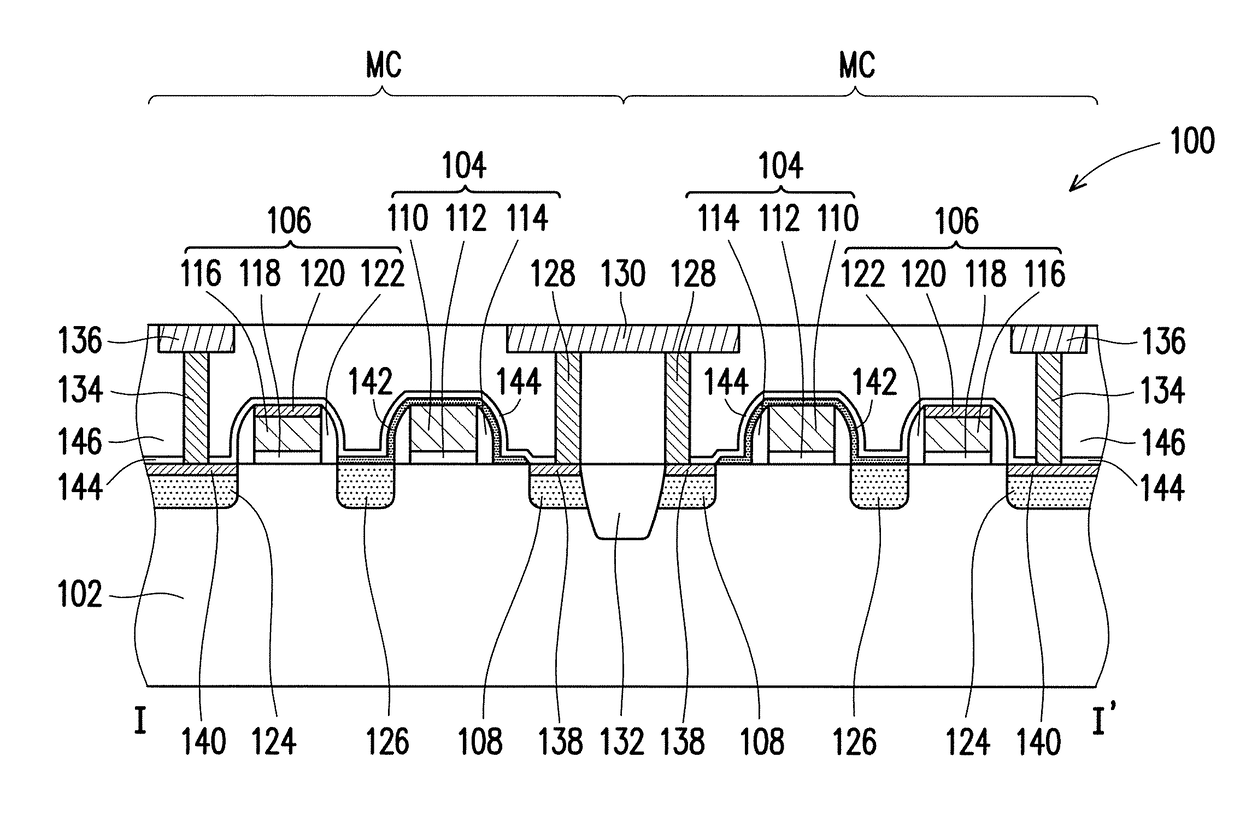

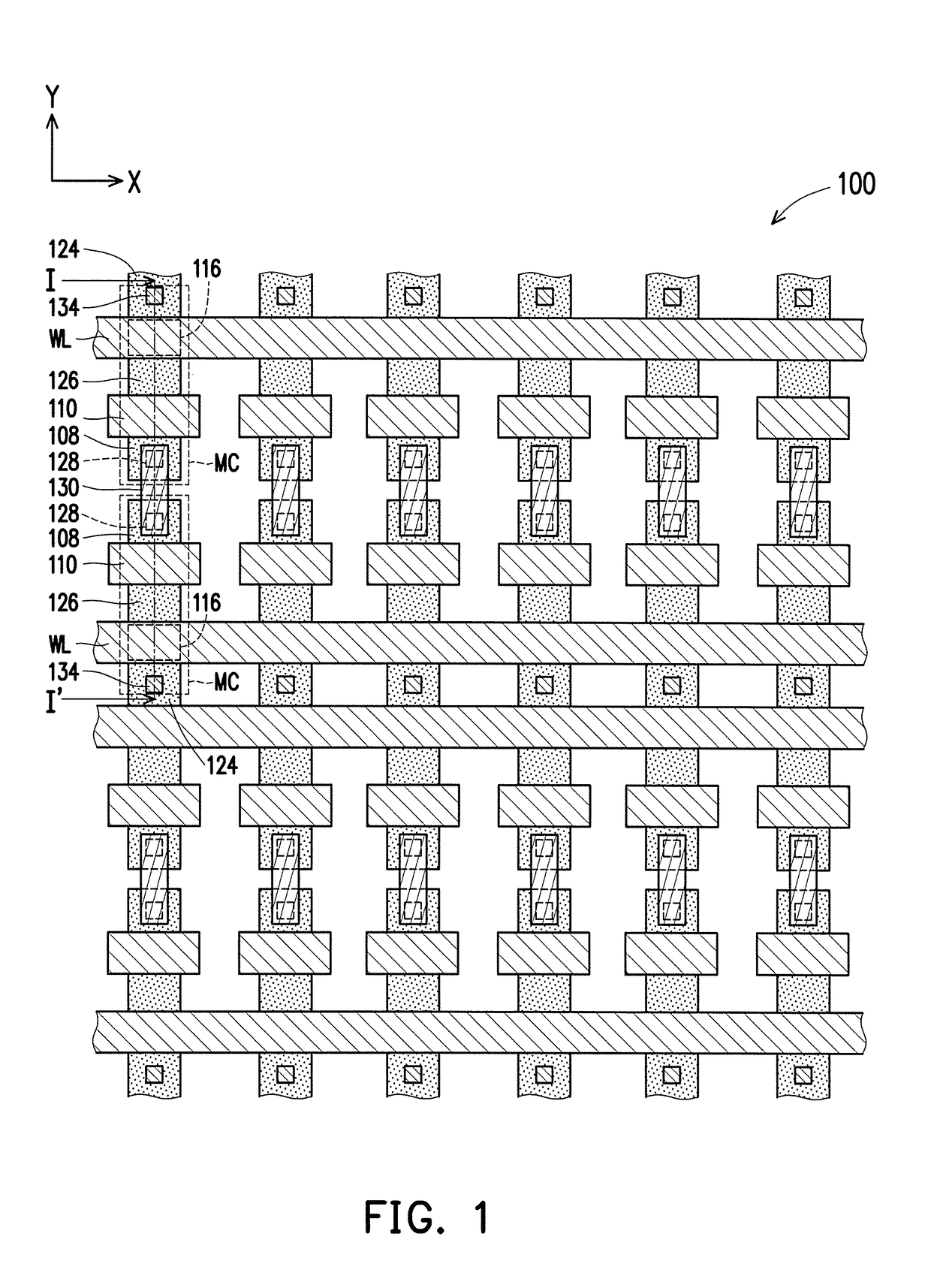

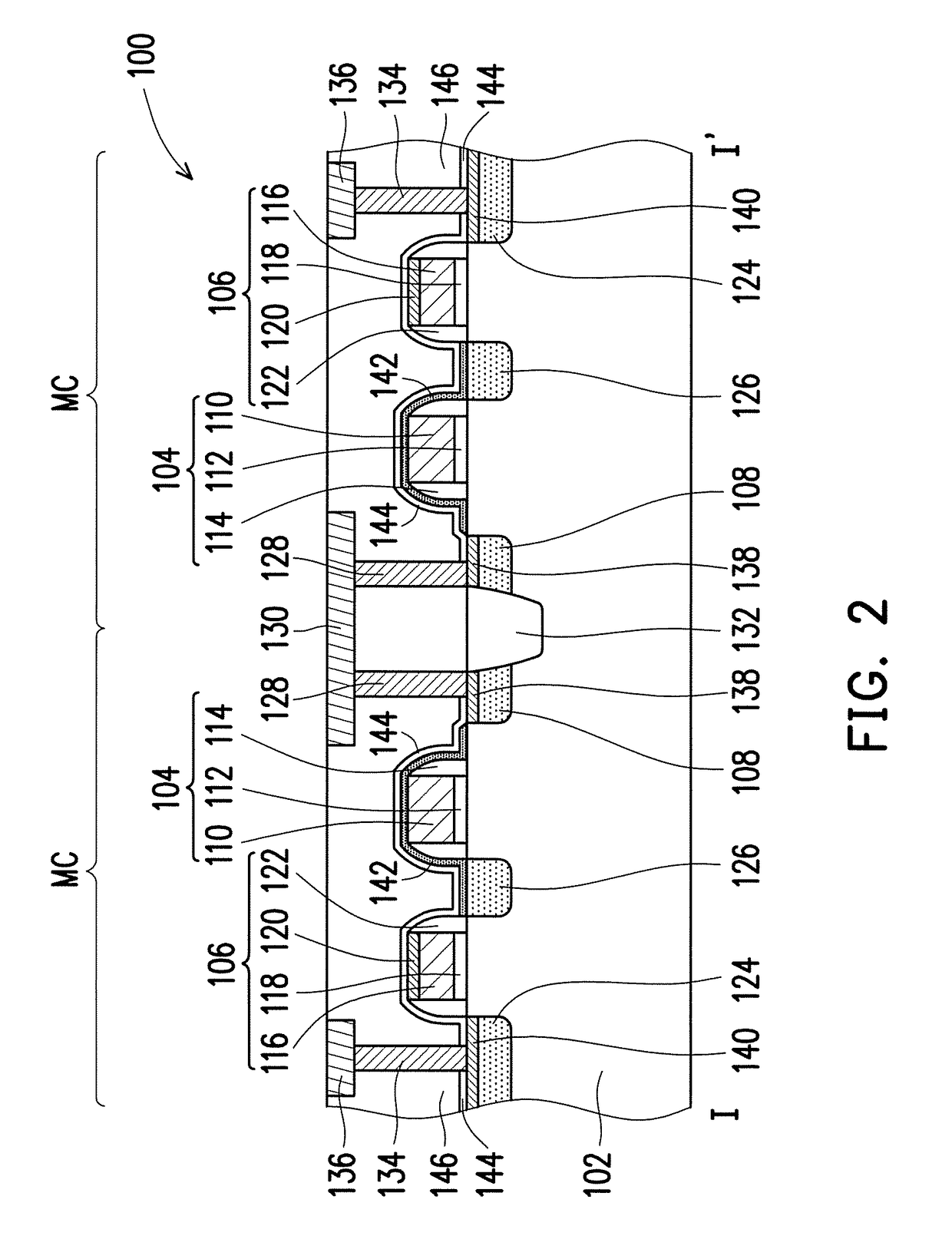

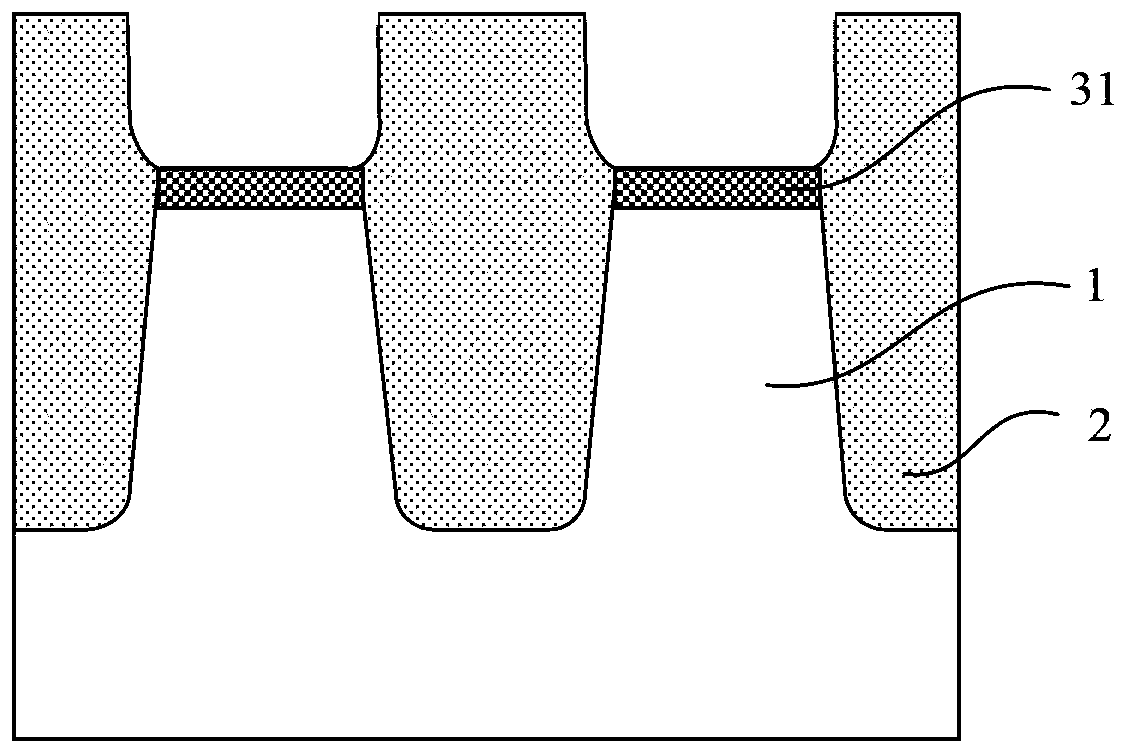

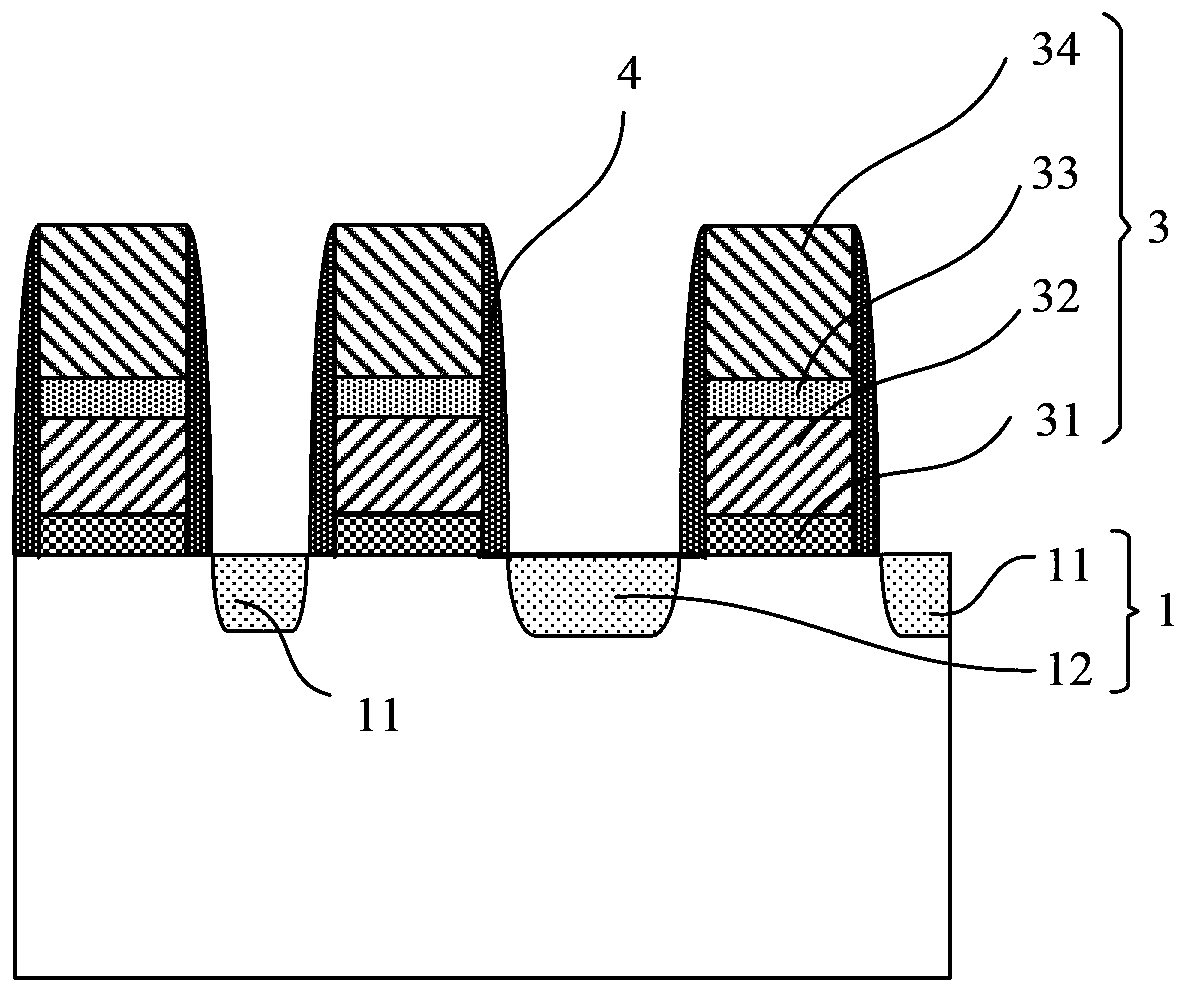

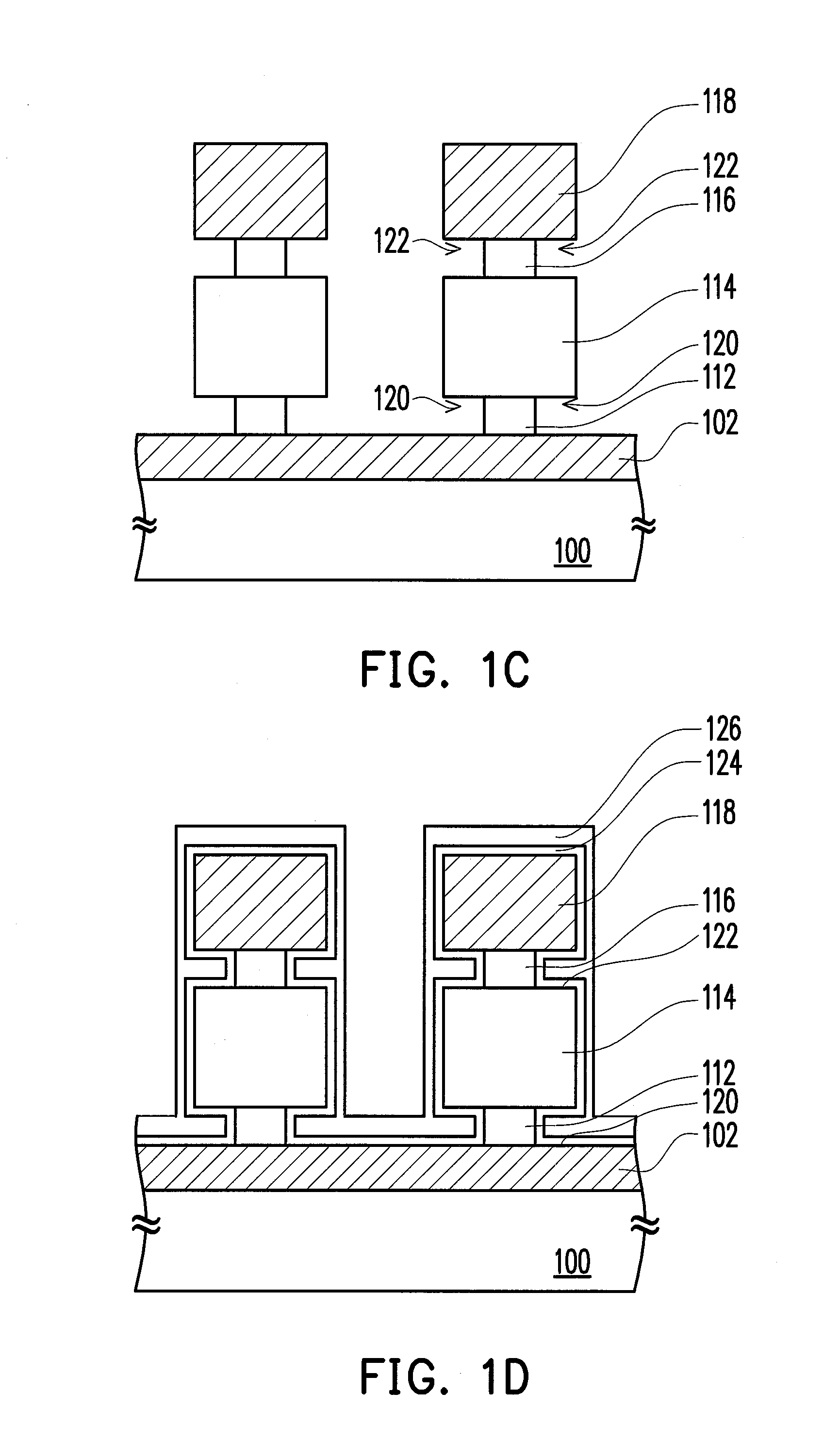

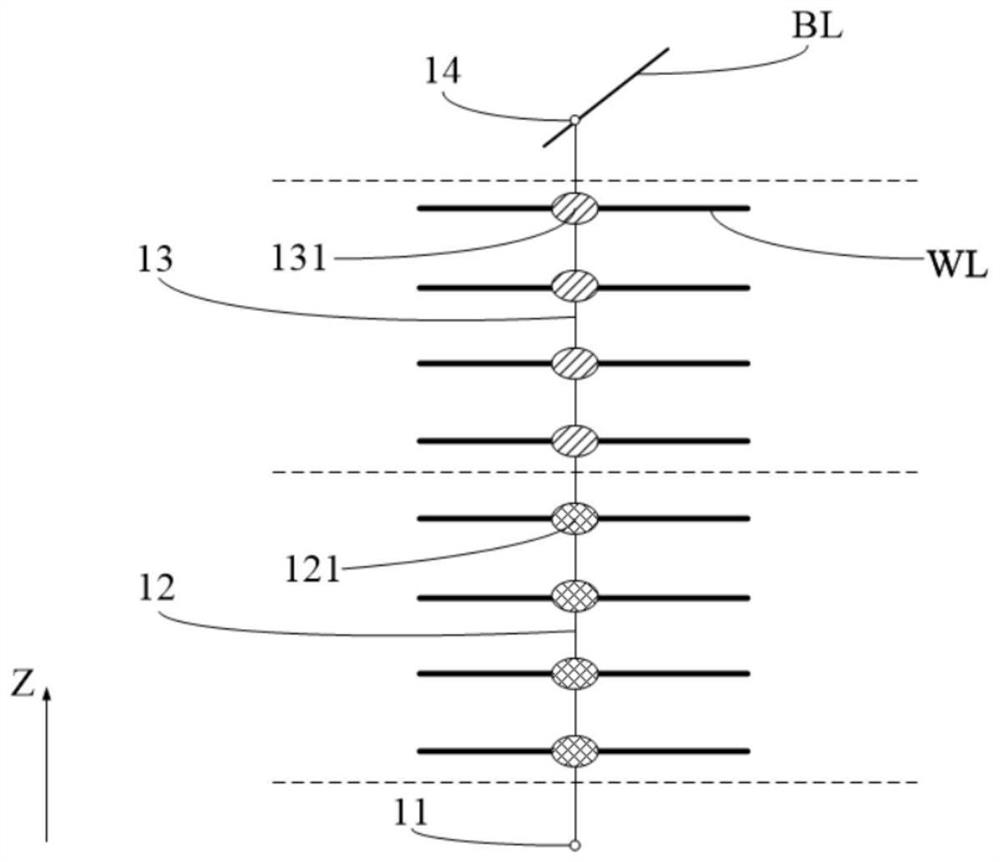

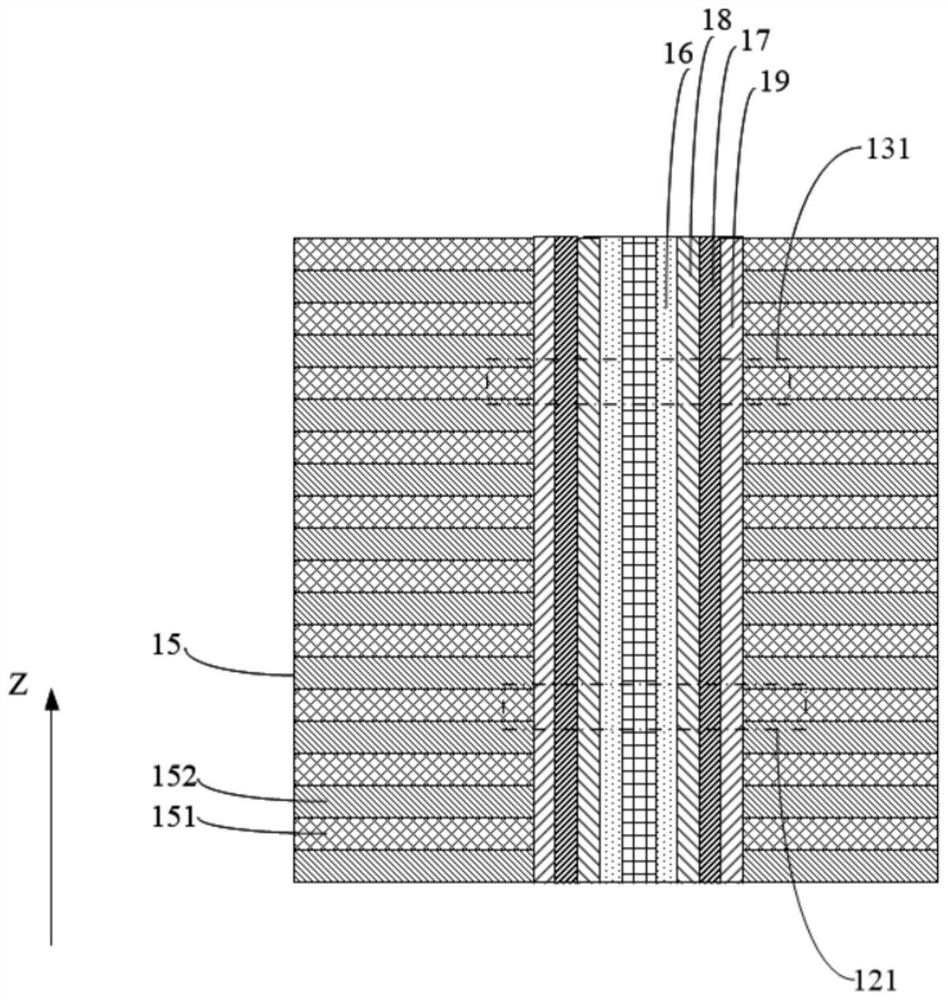

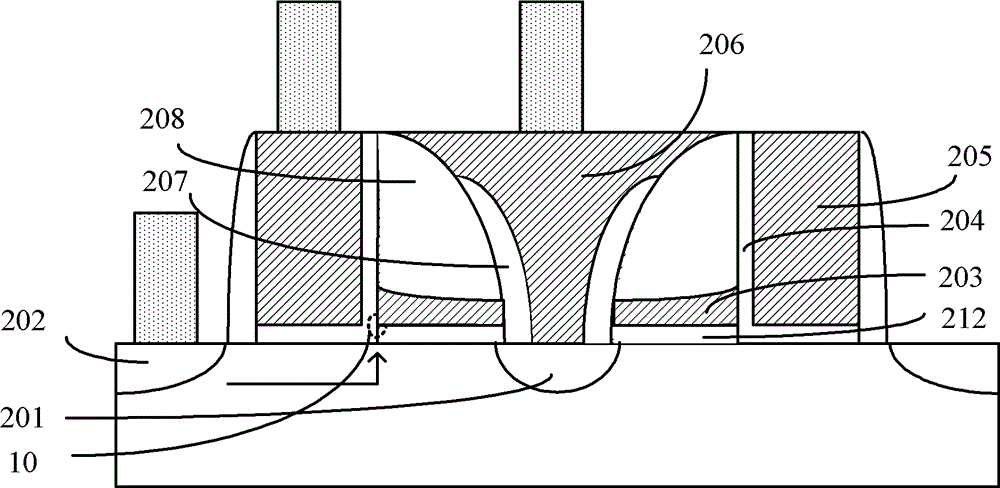

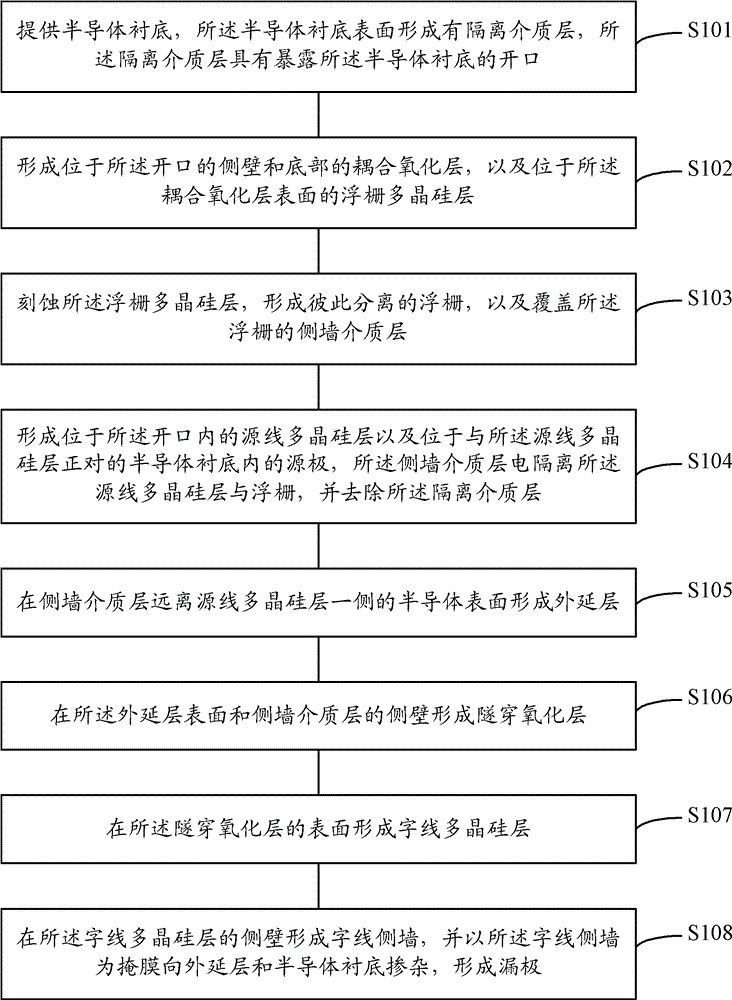

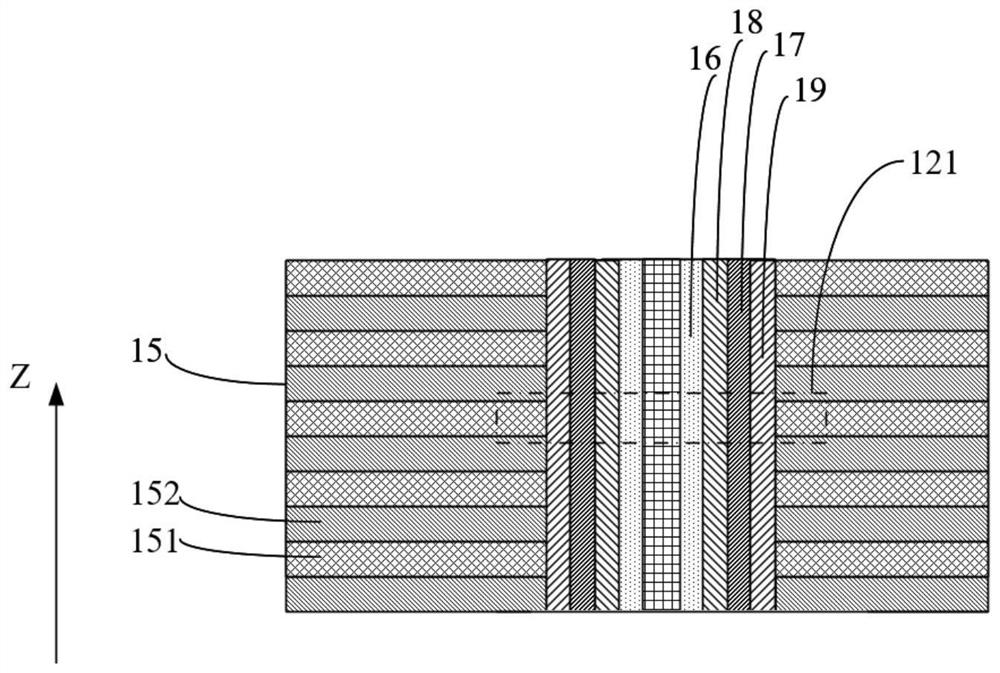

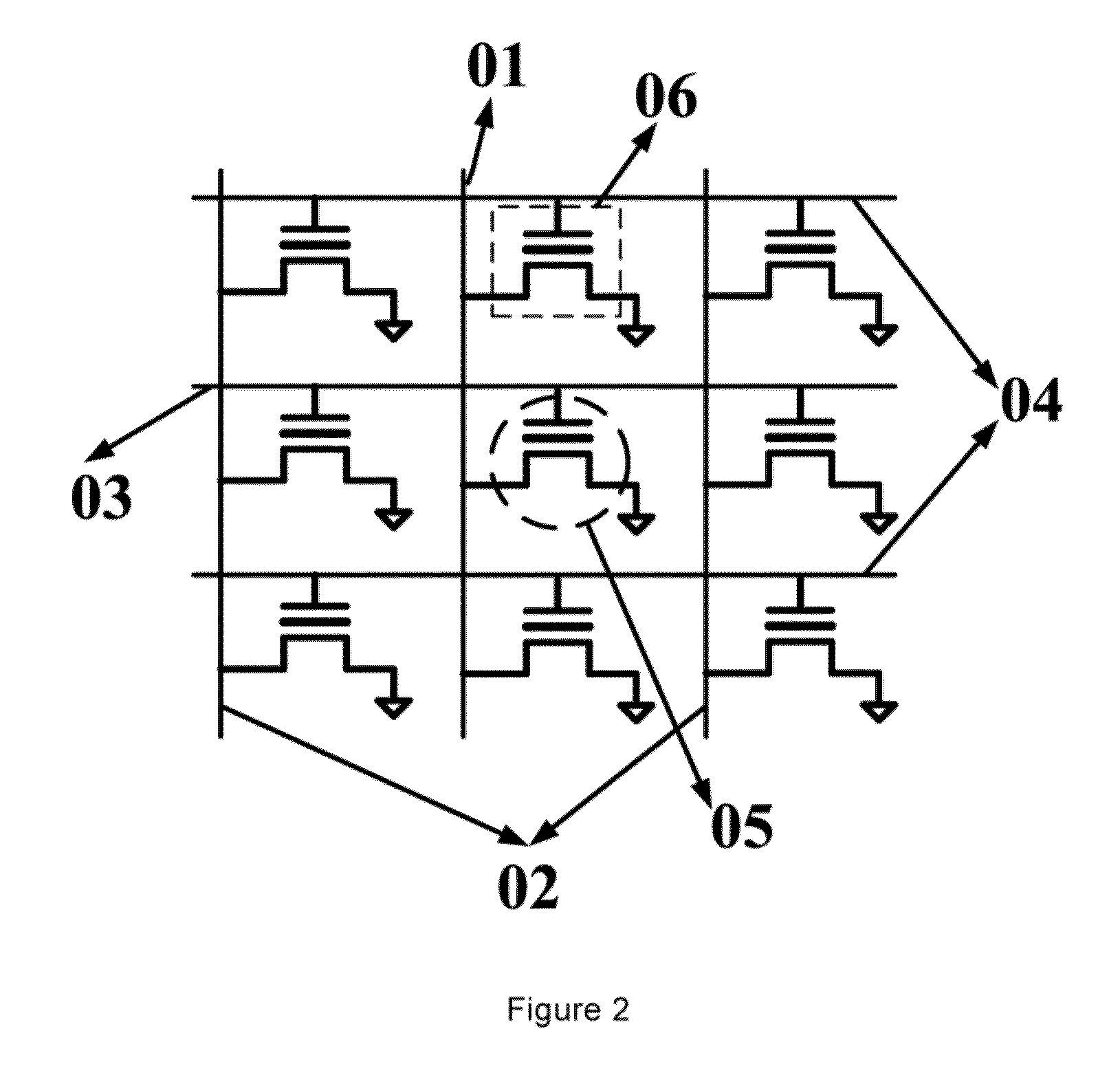

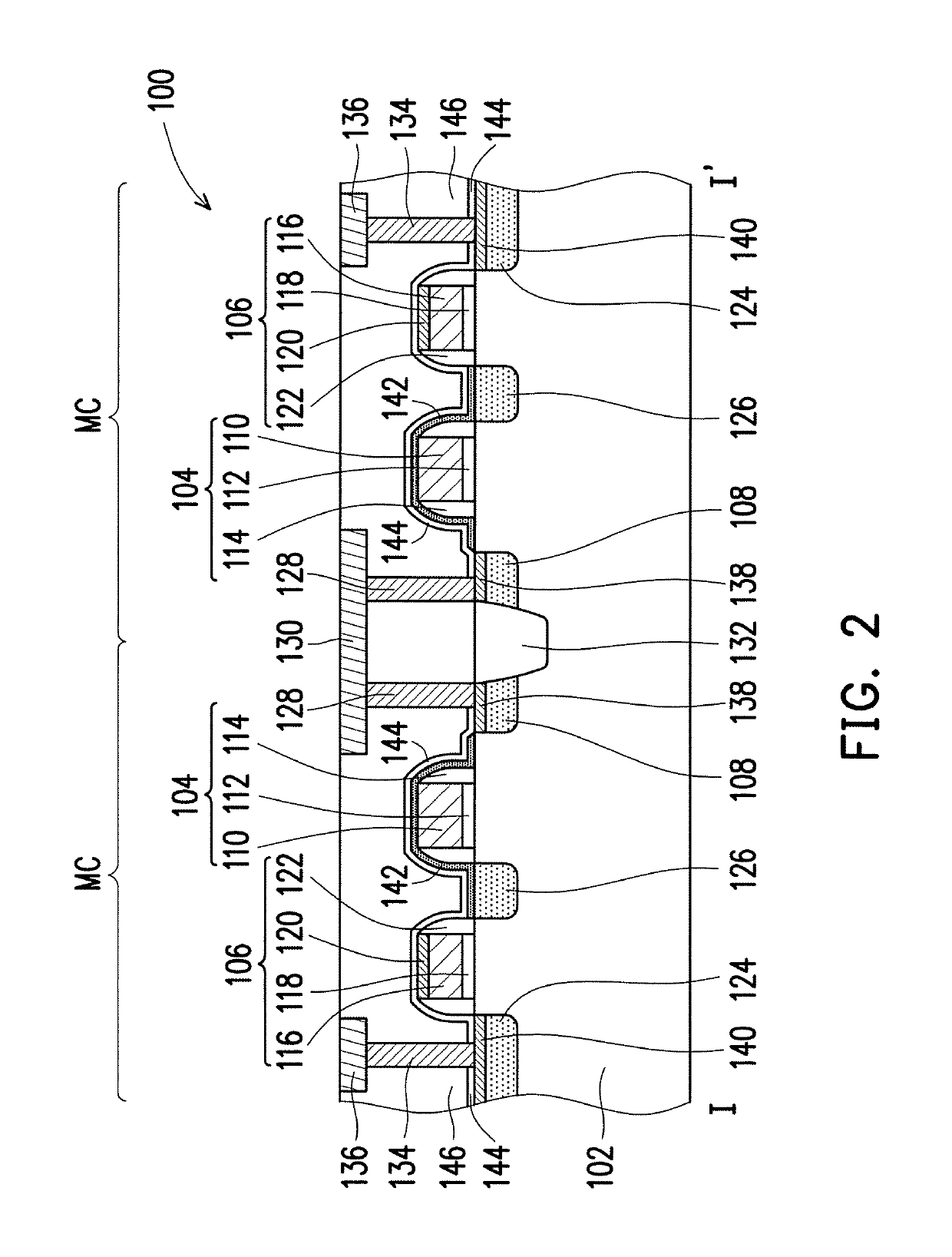

The invention provides a split-gate flash memory unit and a forming method thereof. The split-gate flash memory unit comprises a semiconductor substrate, a source line polycrystalline silicon layer which is located on the surface of the semiconductor substrate, a source electrode which is located in the semiconductor substrate aligned to the source line polycrystalline silicon layer, a coupling oxide layer and a floating gate which are sequentially located on the semiconductor substrate surfaces at two sides of the source polycrystalline silicon layer, a side wall medium layer which is used for electrically isolating the source wire line polycrystalline silicon from the coupling oxide layer and the floating gate, a coupling oxide layer which is located on the side wall of the floating gate far away from the source line polycrystalline silicon layer, an epitaxial layer which is located on the surface of the semiconductor substrate at one side of the coupling oxide layer far away from the source line polycrystalline silicon layer, tunneling oxide layers which are located on the surface of the epitaxial layer and on the side wall of the side medium layer far away from the source line polycrystalline silicon layer, word line polycrystalline silicon layers which are located on the surfaces of the tunneling oxide layers, and drainage electrodes which are located in the epitaxial layer at one side of the word line polycrystalline silicon layer far away from the floating gate and the semiconductor substrate. With the adoption of the split-gate flash memory unit provided by the invention, the programming efficiency of the split-gate flash memory unit can be improved and the miniaturization is easy to realize.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

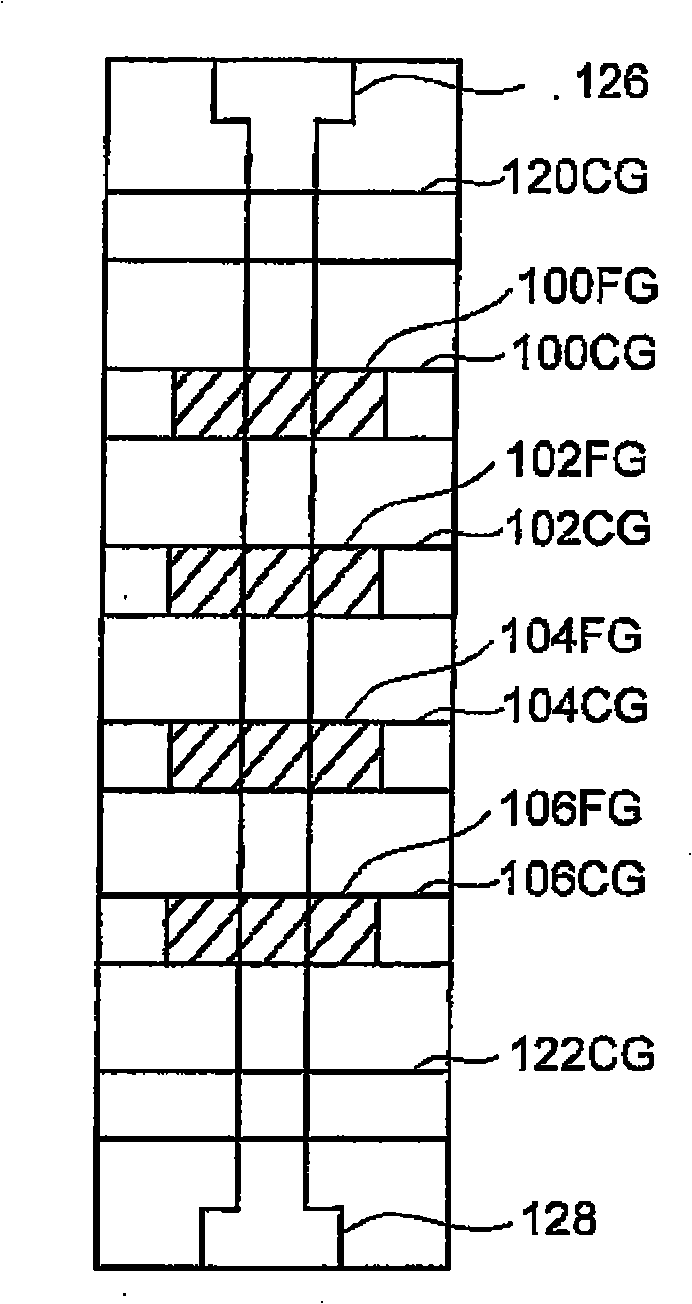

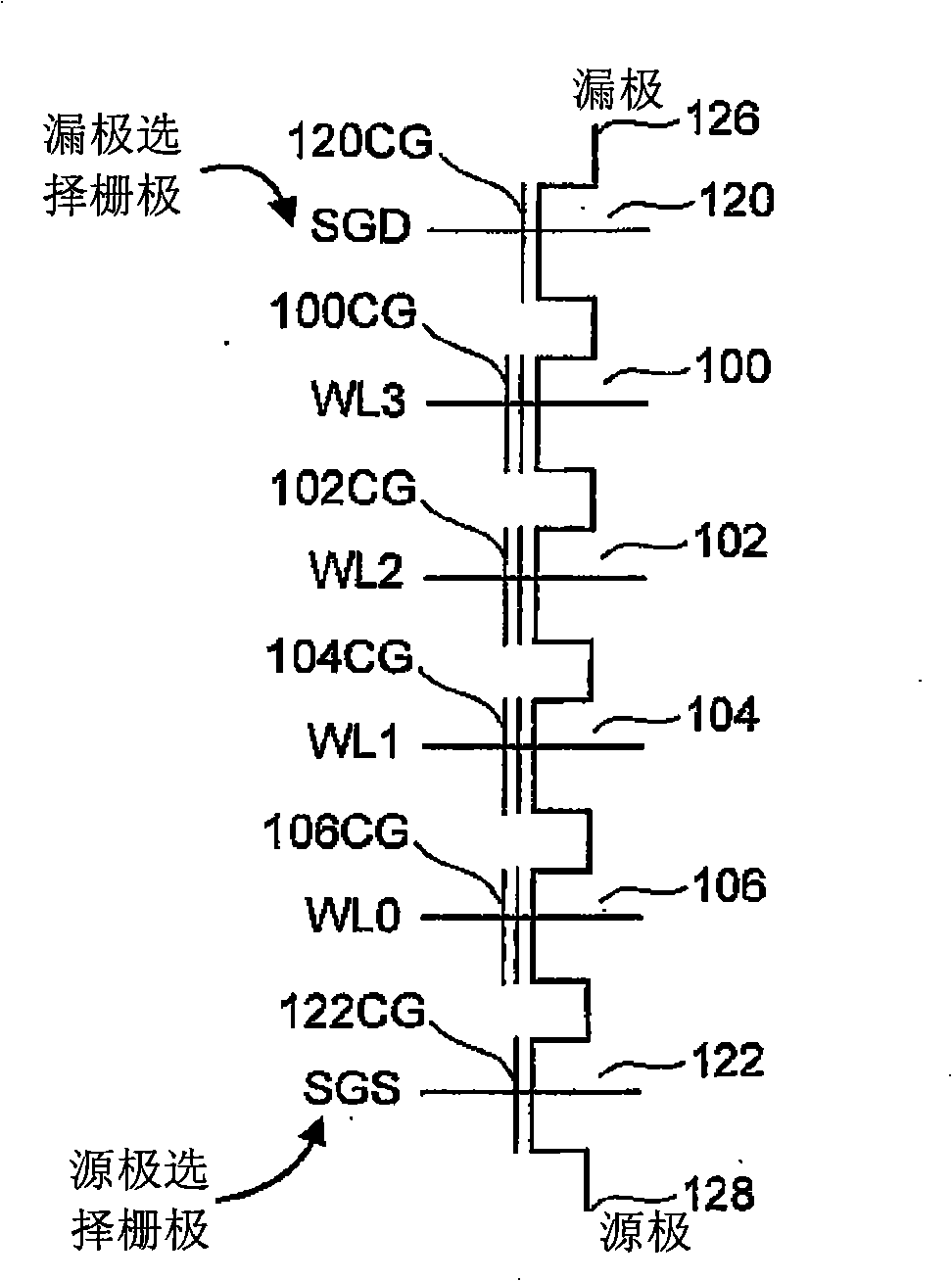

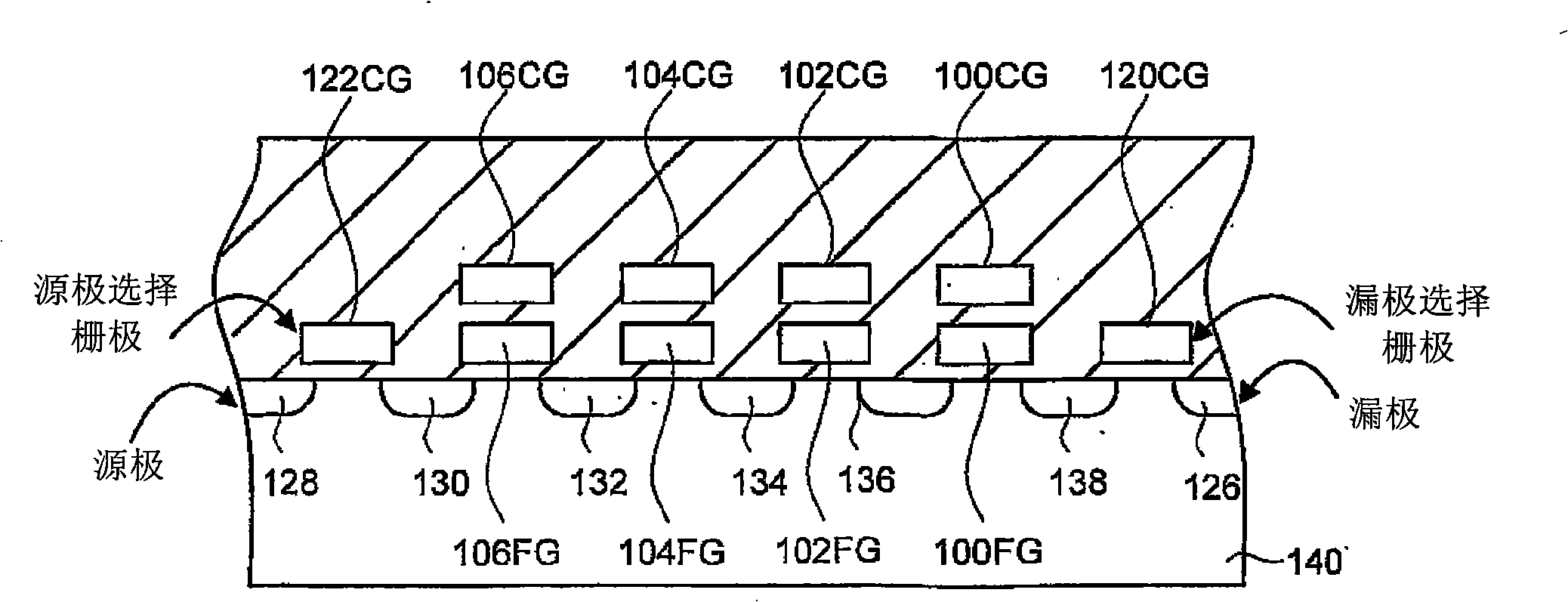

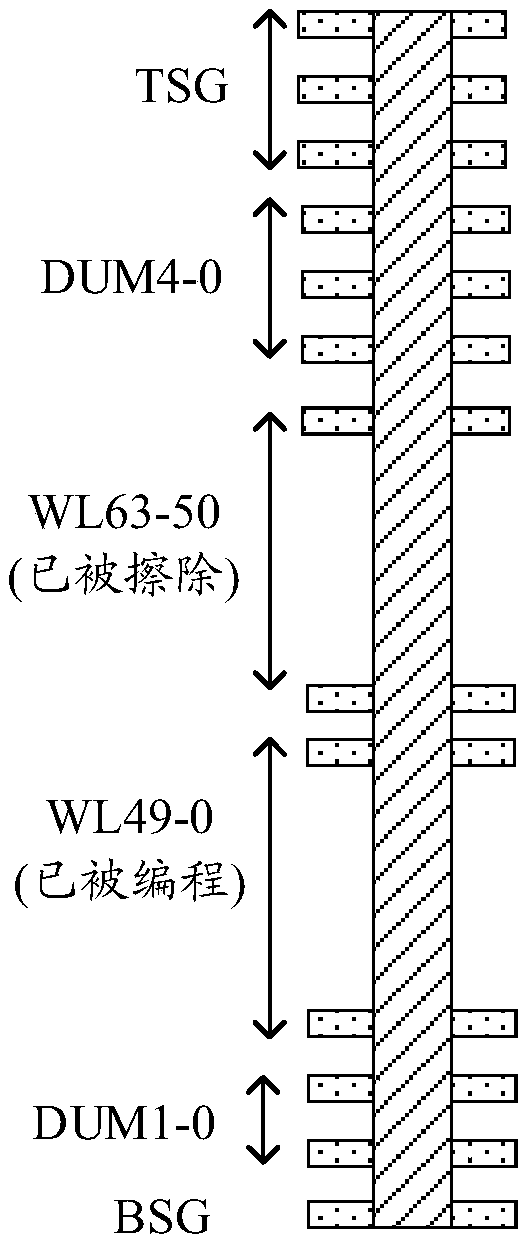

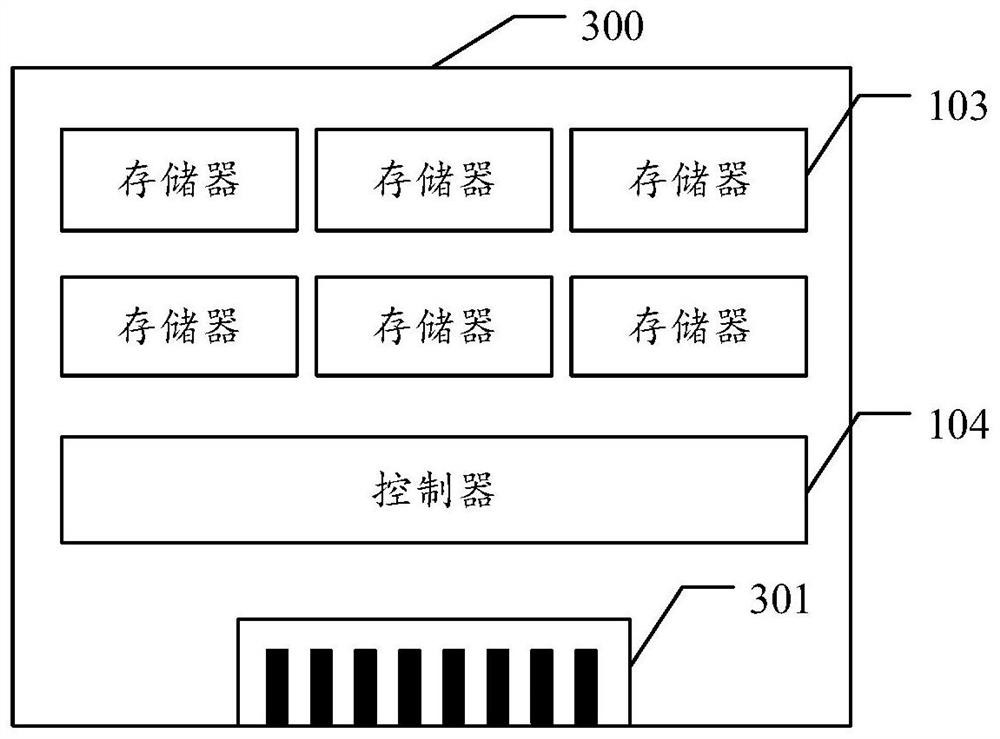

Last-first mode and method for programming of non-volatile memory of NAND type with reduced program disturb

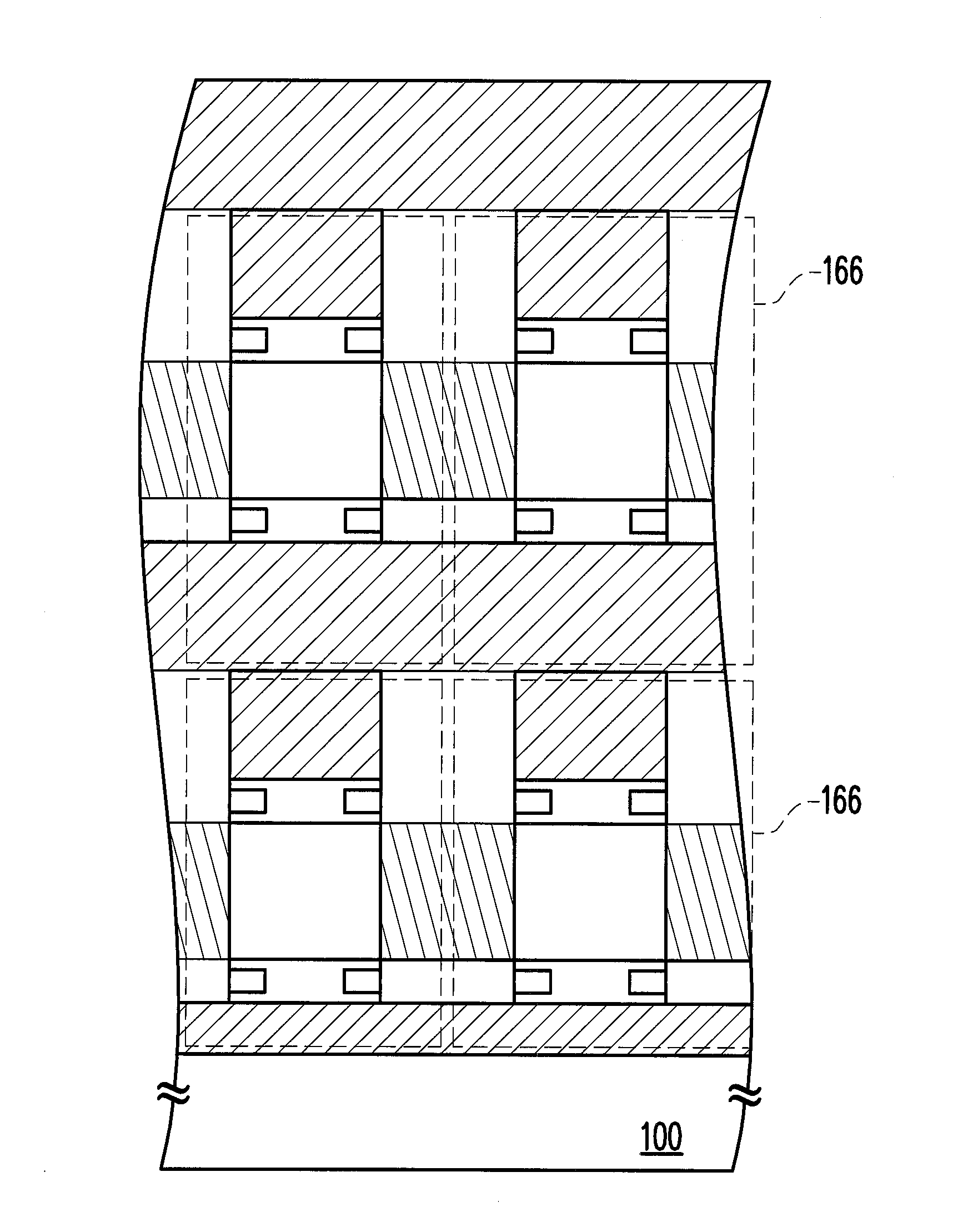

A non-volatile memory is programmed in a manner which reduces the incidence of program disturb for inhibited memory elements which undergo boosting to reduce program disturb, but which experience reduced boosting benefits due to their word line location. To achieve this result, a word line sequence in which the memory elements are programmed is adjusted so that higher word lines are programmed first, out of sequence relative to the remaining word lines. Additionally, self-boosting can be used for the higher word lines, while erased area self-boosting or a variant can be used for the remaining word lines. Furthermore, pre-charging of the channel of the inhibited memory elements may be employed prior to the self boosting, for the non-volatile storage elements which are programmed after those associated with the first word line.

Owner:SANDISK TECH LLC

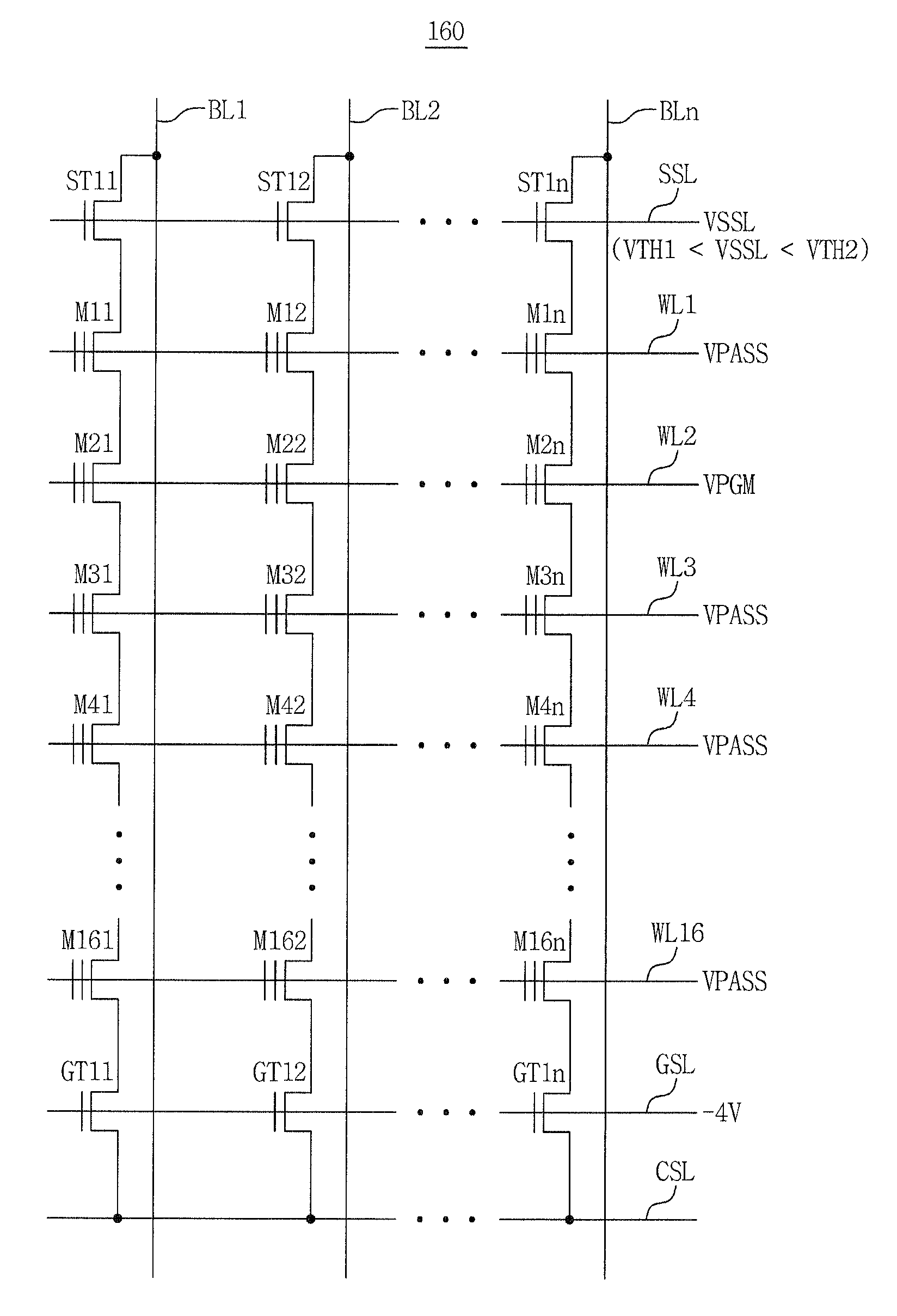

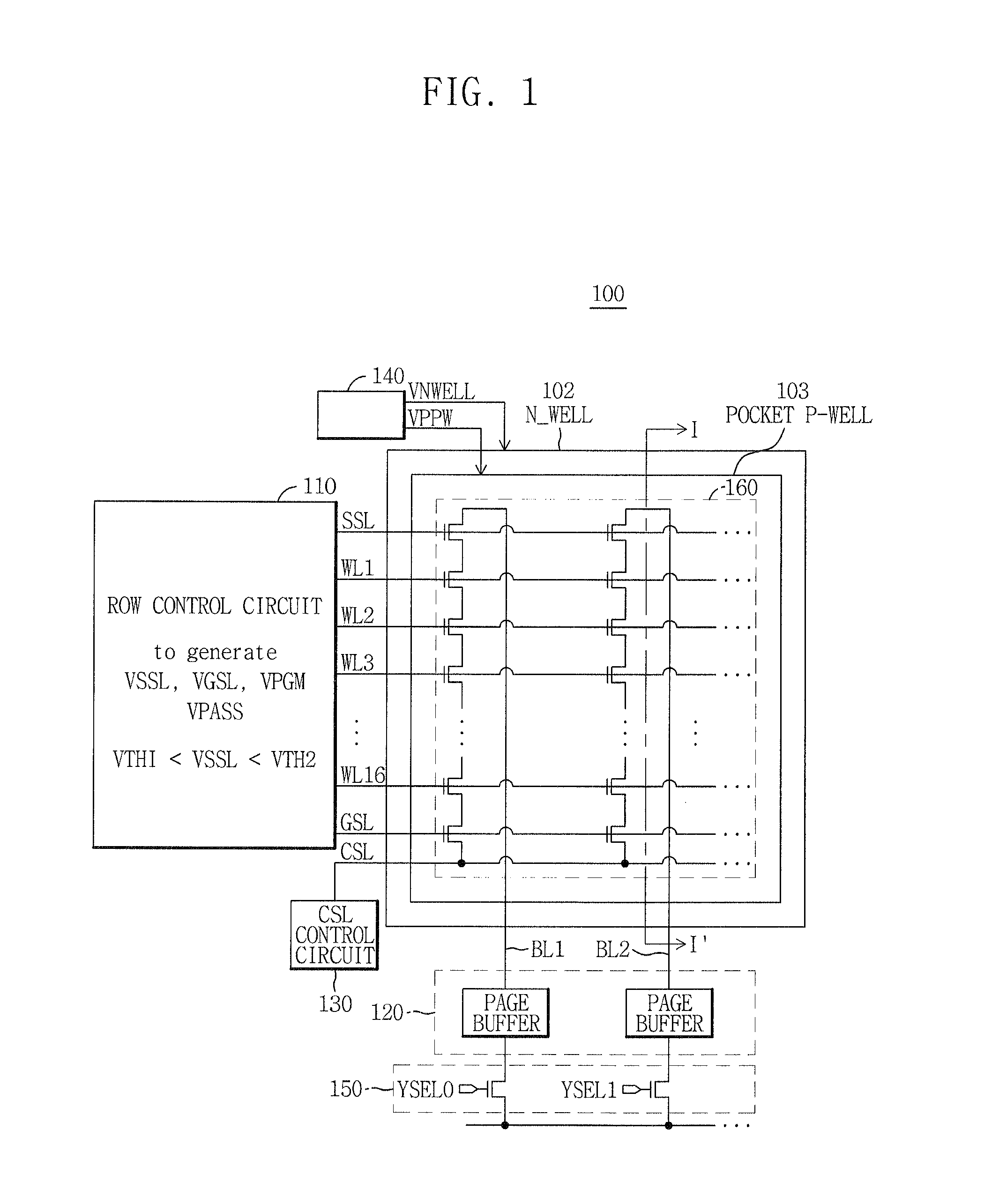

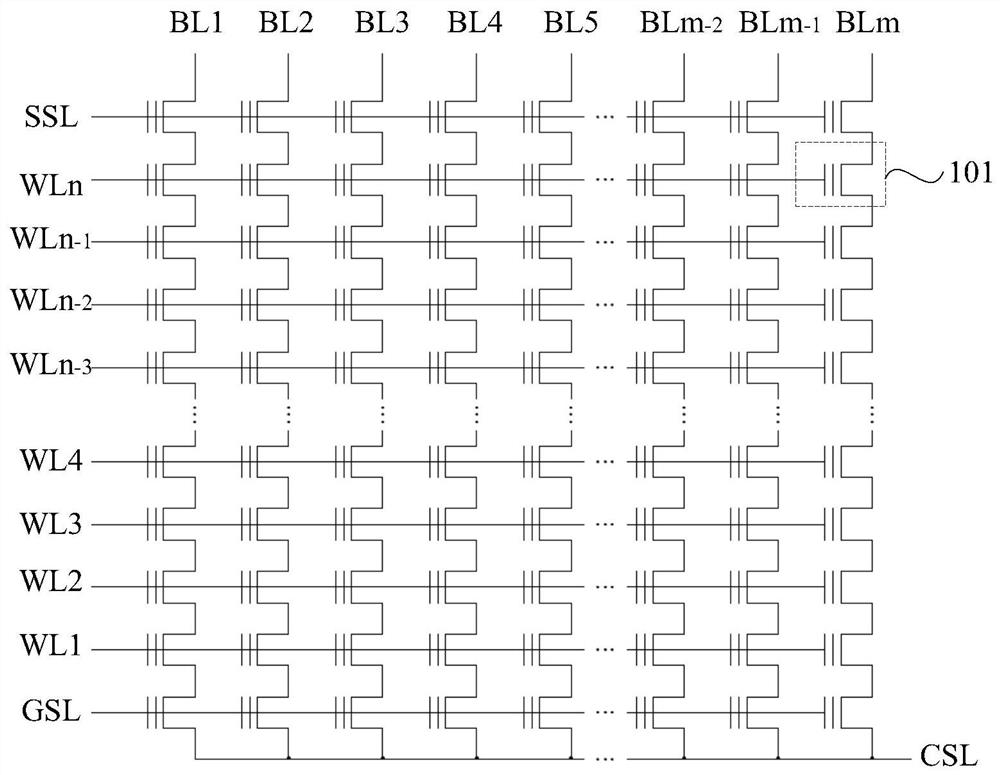

Method of programming nonvolatile semiconductor memory device

A method of programming a nonvolatile semiconductor memory device using a negative bias voltage. The method includes turning ON the string selection transistors connected to selected bit lines and turning OFF the string selection transistors connected to unselected bit lines in the same memory block, in a program mode. This can be achieved by applying a negative bias voltage to a bulk substrate and applying a voltage having a voltage level higher than the threshold voltage of string selection transistors connected to selected bit lines and lower than the threshold voltage of string selection transistors connected to unselected bit lines. The method may reduce programming disturbance between a selected cell string and an unselected cell string.

Owner:SAMSUNG ELECTRONICS CO LTD

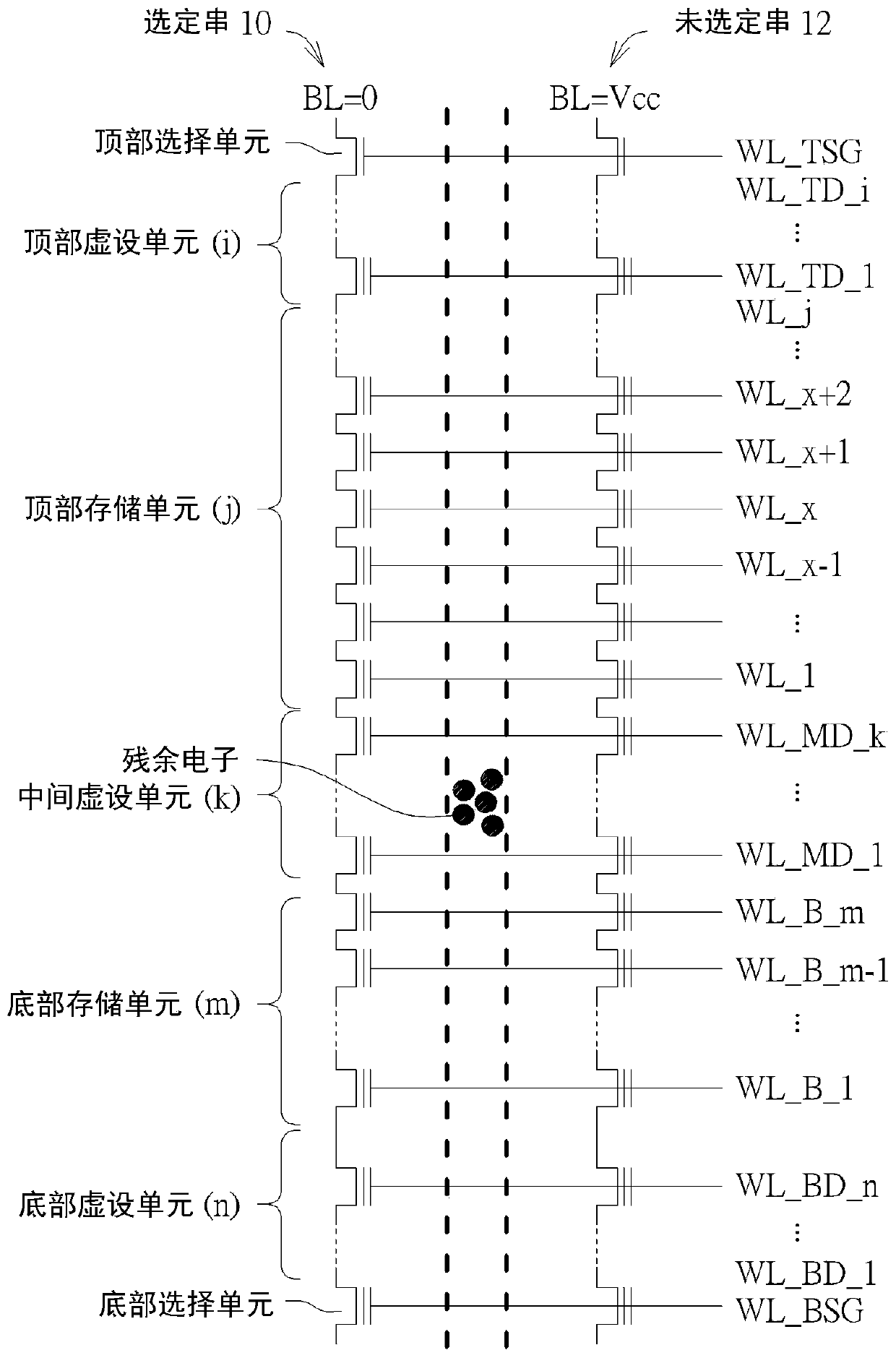

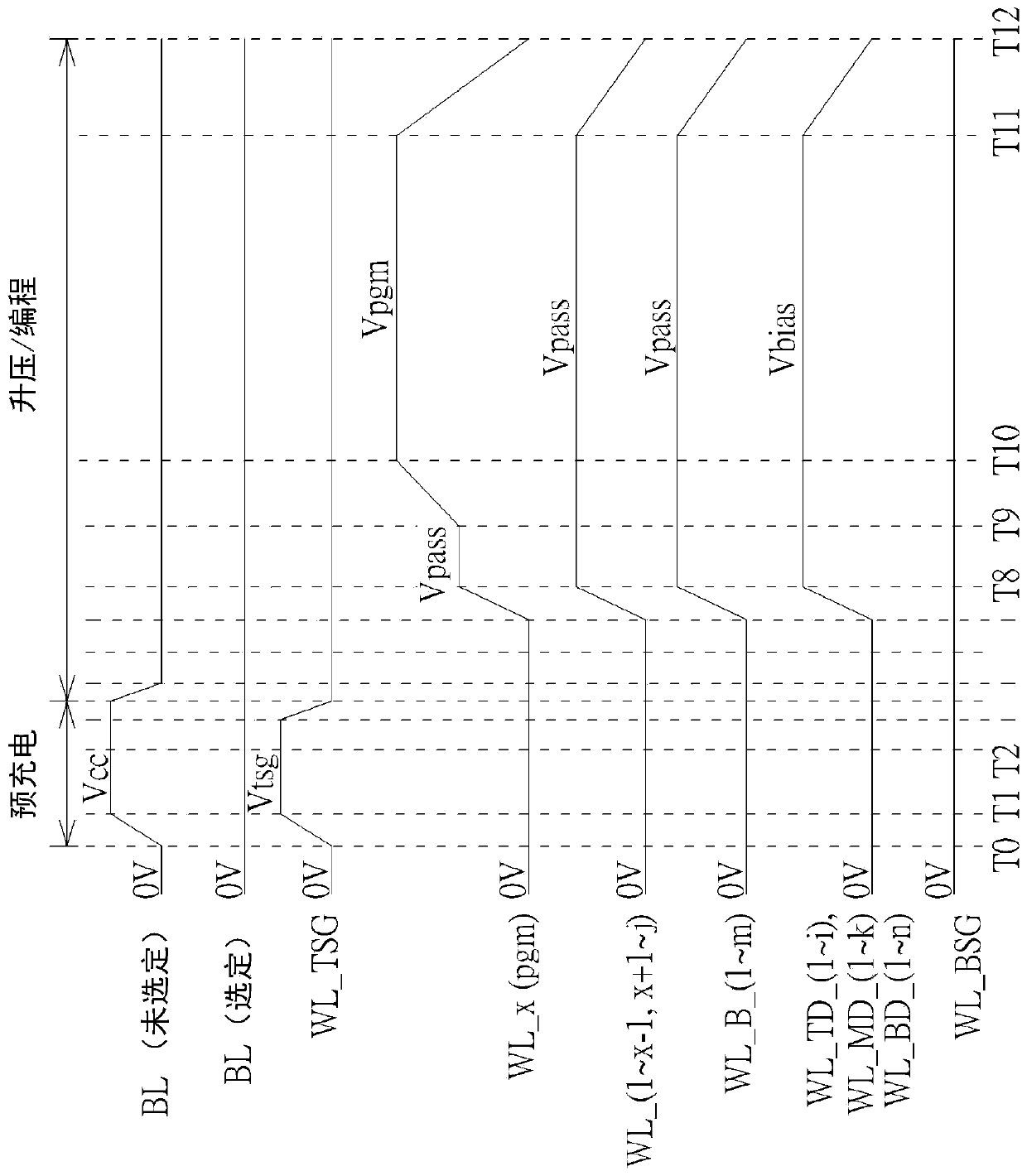

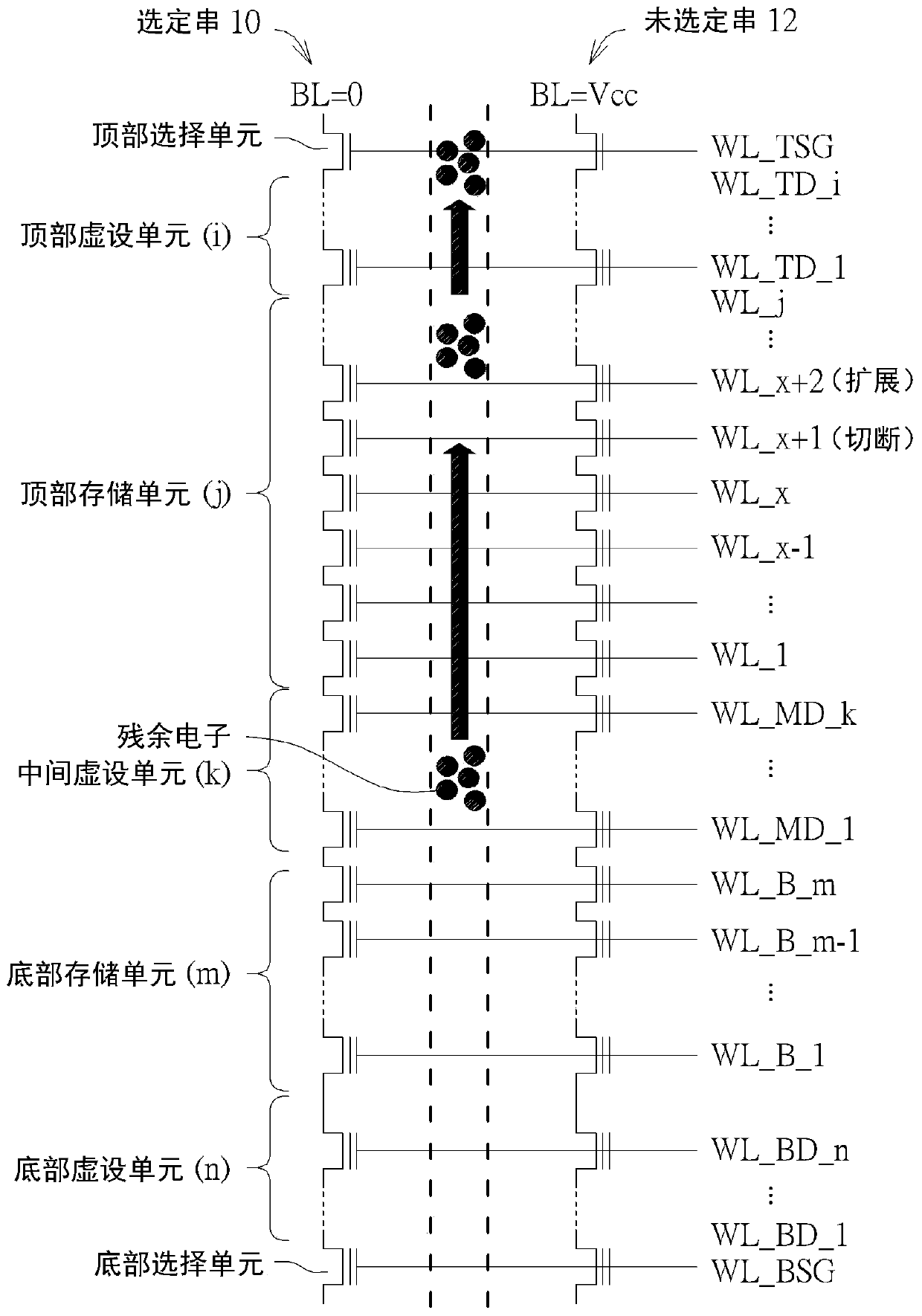

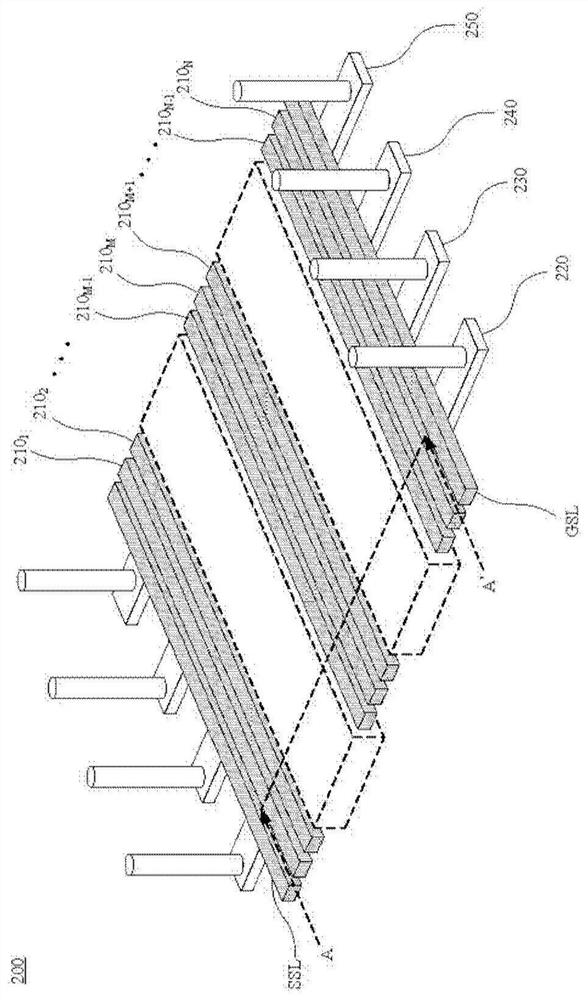

Method of performing program operation and related memory device

A method of performing a program operation on a three-dimensional (3D) NAND memory device is disclosed. The method enables removal of residual electrons trapped in a storage region of an intermediatedummy memory cell of an unselected string of the 3D NAND memory device during a pre-charge phase, thereby reducing programming disturbances to a selected string adjacent to the unselected string.

Owner:YANGTZE MEMORY TECH CO LTD

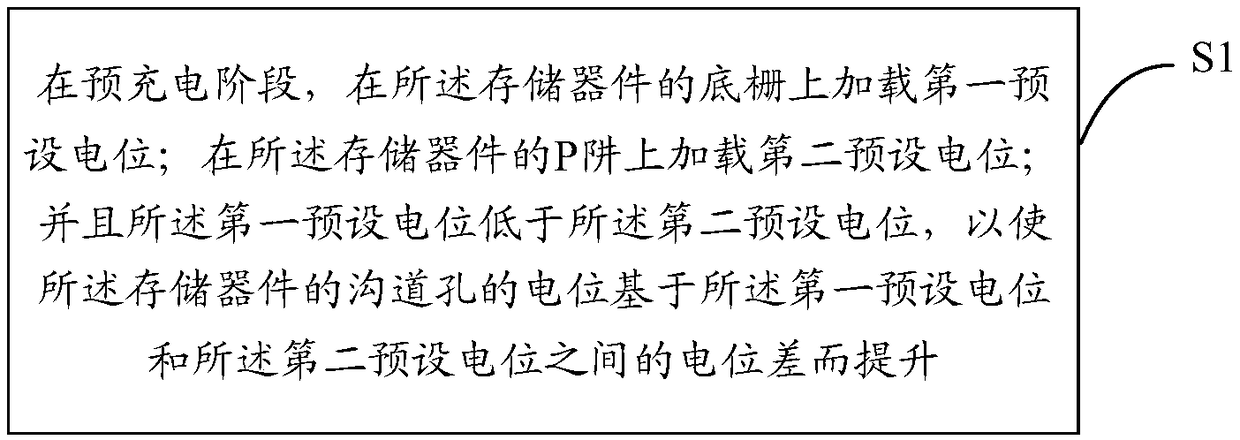

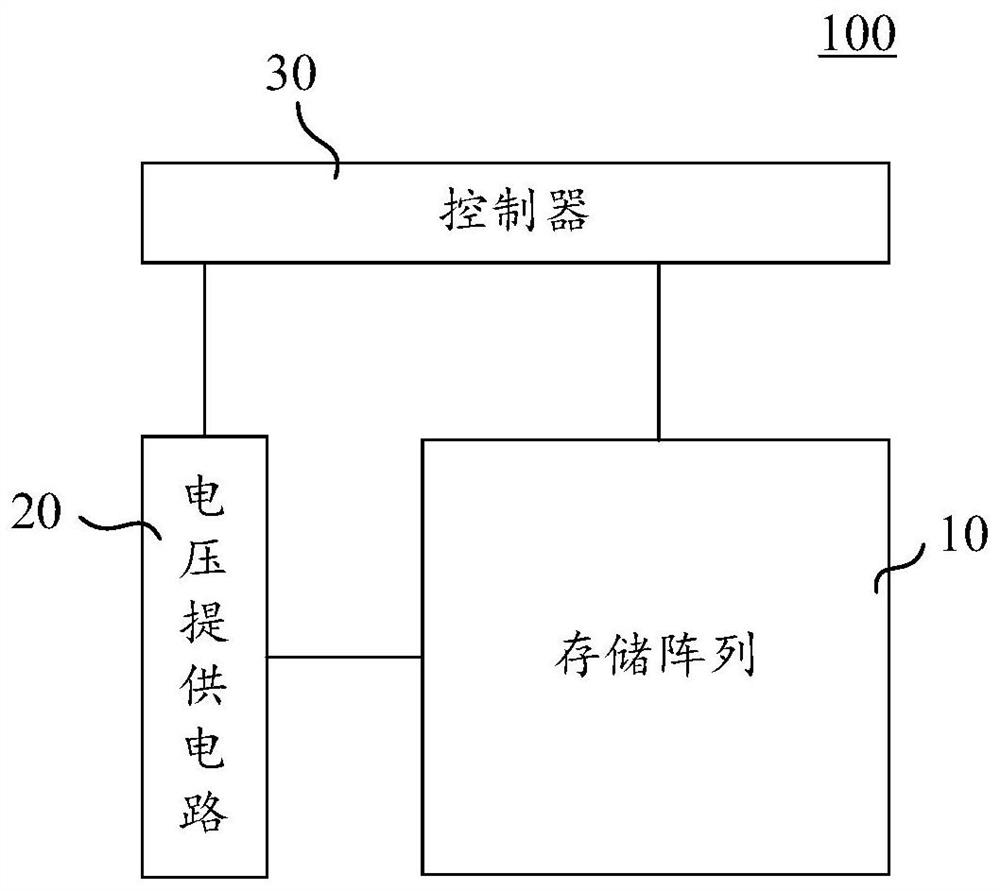

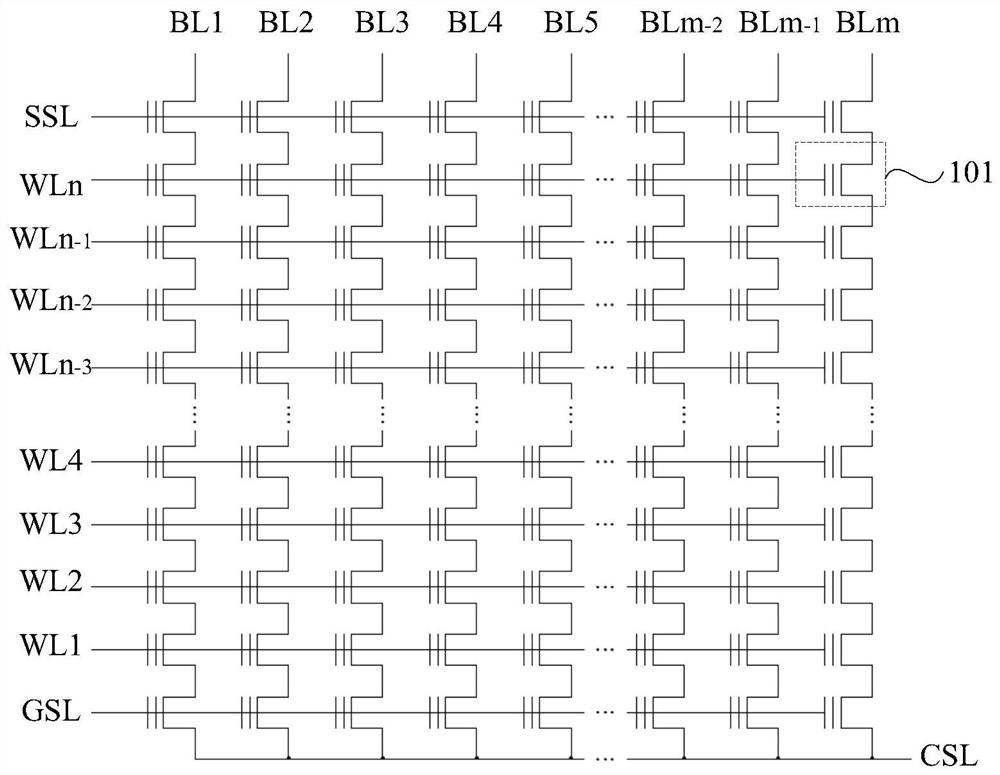

A control method and device for reducing programming interference

ActiveCN109378028ARaise the potentialProgram disturbRead-only memoriesComputer architecturePotential difference

The invention discloses a control method for reducing programming interference. The method is applied to a memory device. The method comprises the following steps: a first preset potential is loaded on a bottom gate of the memory device in a precharging stage; a second preset potential is loaded on the P well of the memory device; And the first preset potential is lower than the second preset potential so that a potential of a channel hole of the memory device is raised based on a potential difference between the first preset potential and the second preset potential.

Owner:长存创芯(上海)集成电路有限公司

Programming and erasing method for non-volatile memory

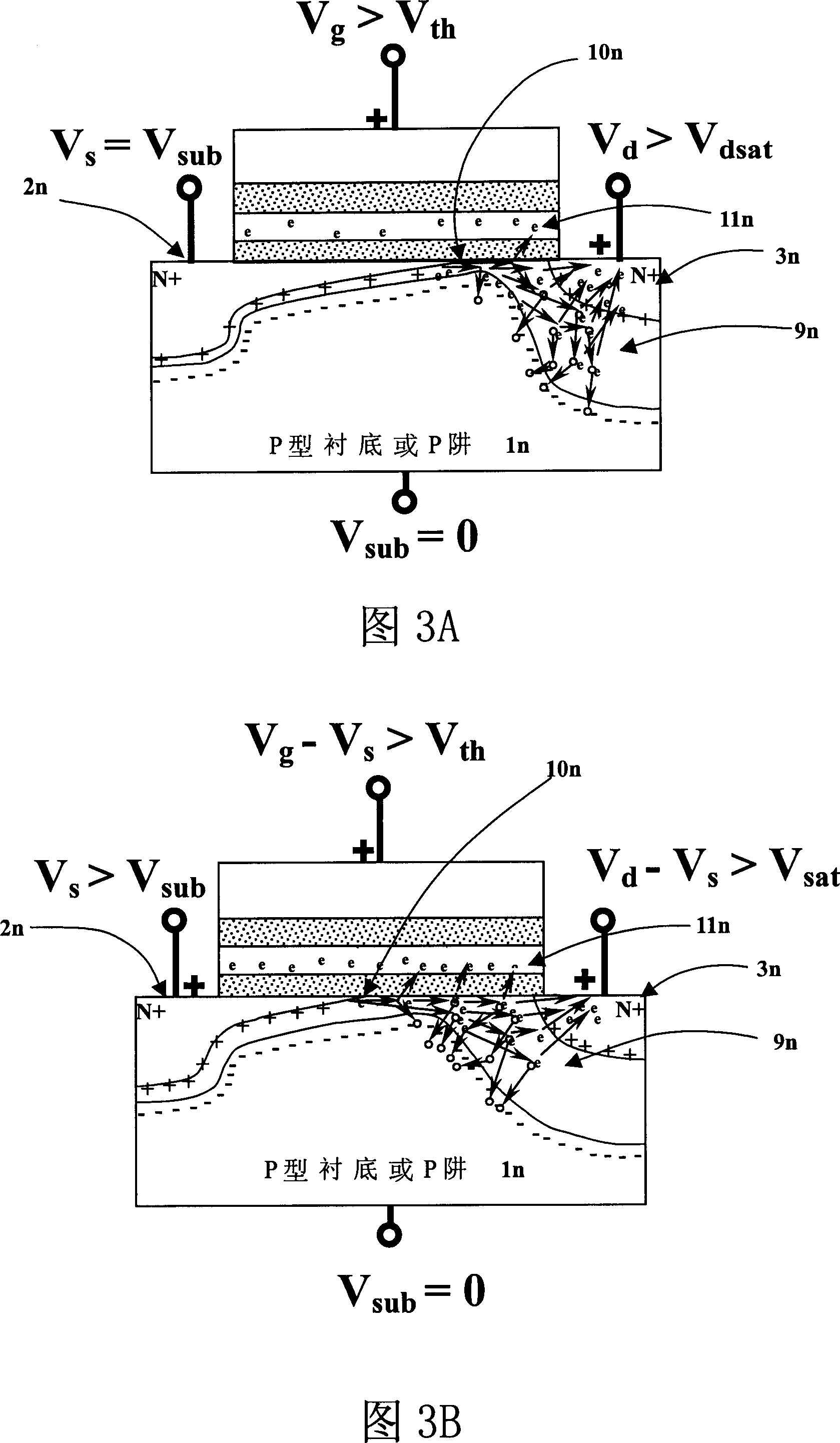

InactiveCN101000801AReduce the burden onProgram disturbRead-only memoriesDigital storageElectron injectionLow voltage

The present invention provides a high-speed low-voltage programming scheme and self-convergent high-speed low-voltage erasing schemes for Electrically Erasable Programmable Read-Only Memories. For the N-type Field Effect Transistor based NVM programming, an elevated source voltage to the substrate can achieve high efficient Drain-Avalanche-Hot-Electron Injection into the floating gate resulting in high-speed and low-voltage operations. The self-convergent and low-voltage erasing can be achieved by applying Drain-Avalanche-Hot Hole Injection with the conditions of restricted maximum drain current and a moderate control gate voltage enough to turn on the NFET. For the p-type FET based EEPROM programming, a negative source voltage relative to the substrate can achieve high efficient Drain-Avalanche-Hot-Hole Injection into the floating gate resulting in high-speed and low voltage operations. The self-convergent and low voltage erasing can be achieved by applying Drain-Avalanche-Hot-Electron Injection with the conditions of restricted maximum magnitude of drain current and a negative moderate control gate voltage enough to turn on the PFET.

Owner:YIELD MICROELECTRONICS CORP

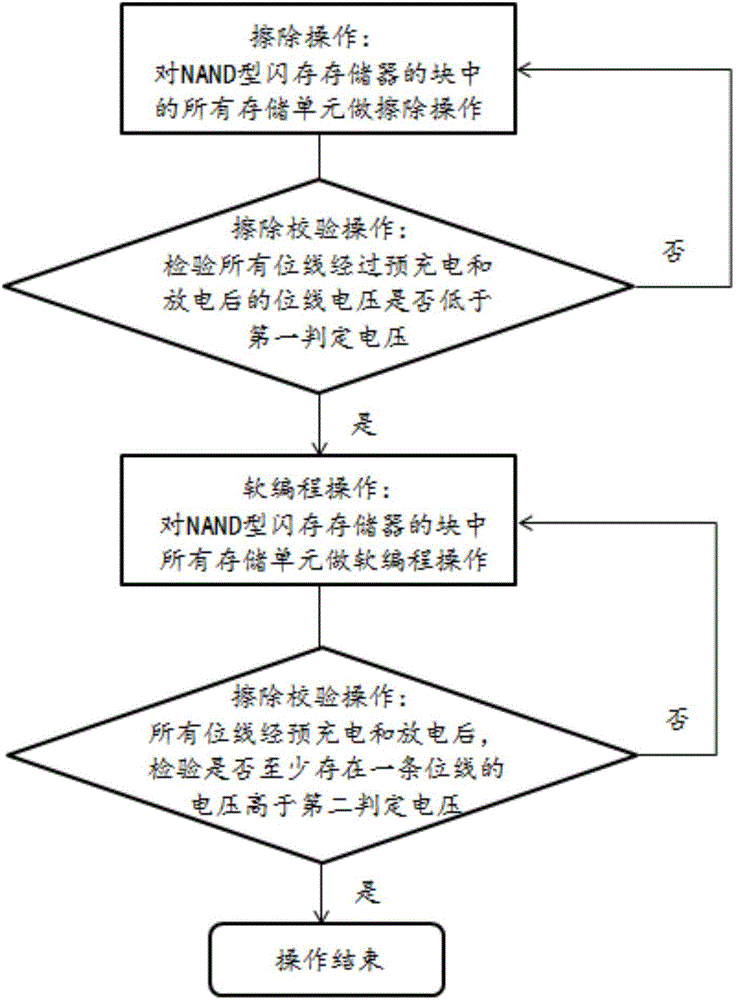

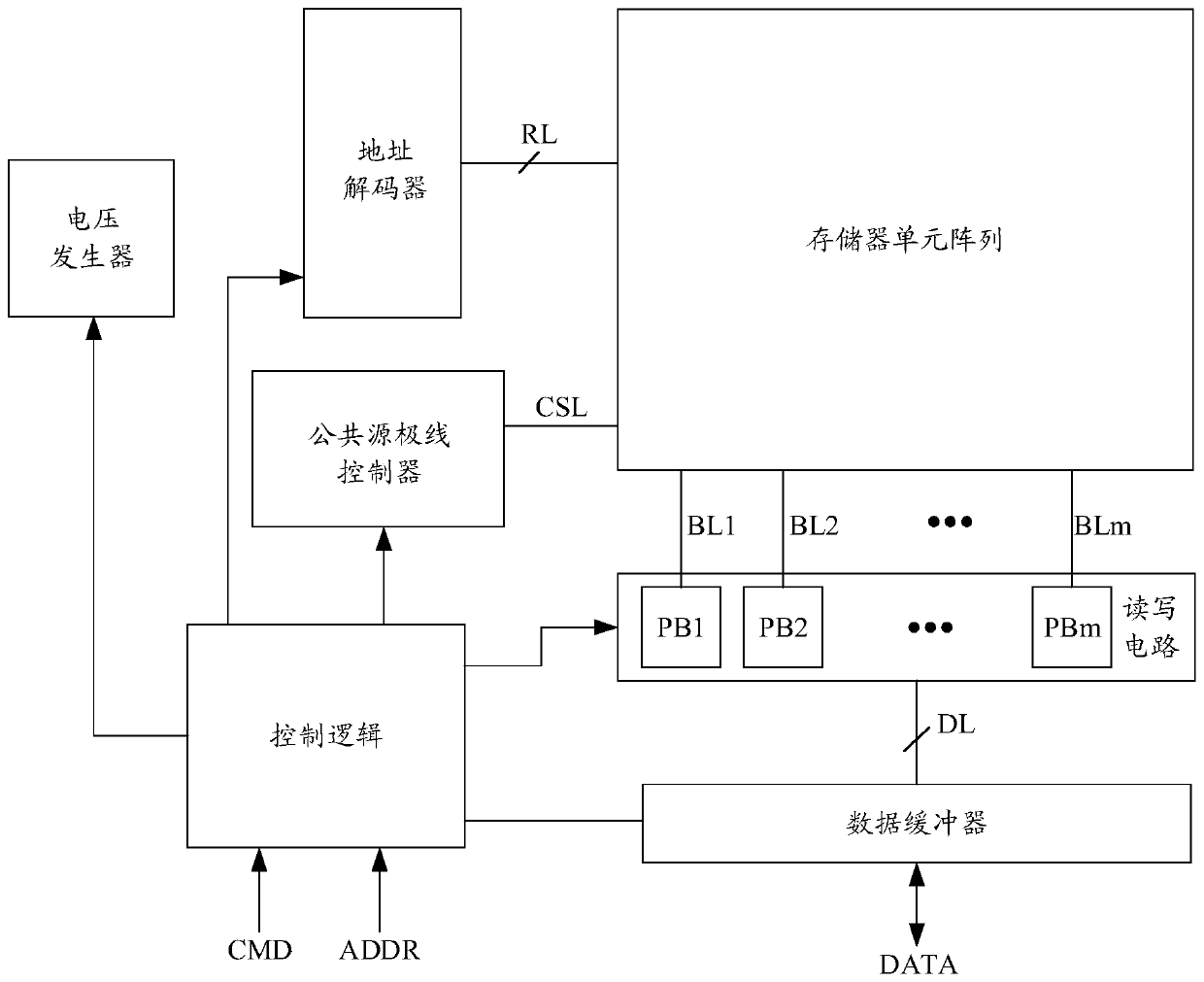

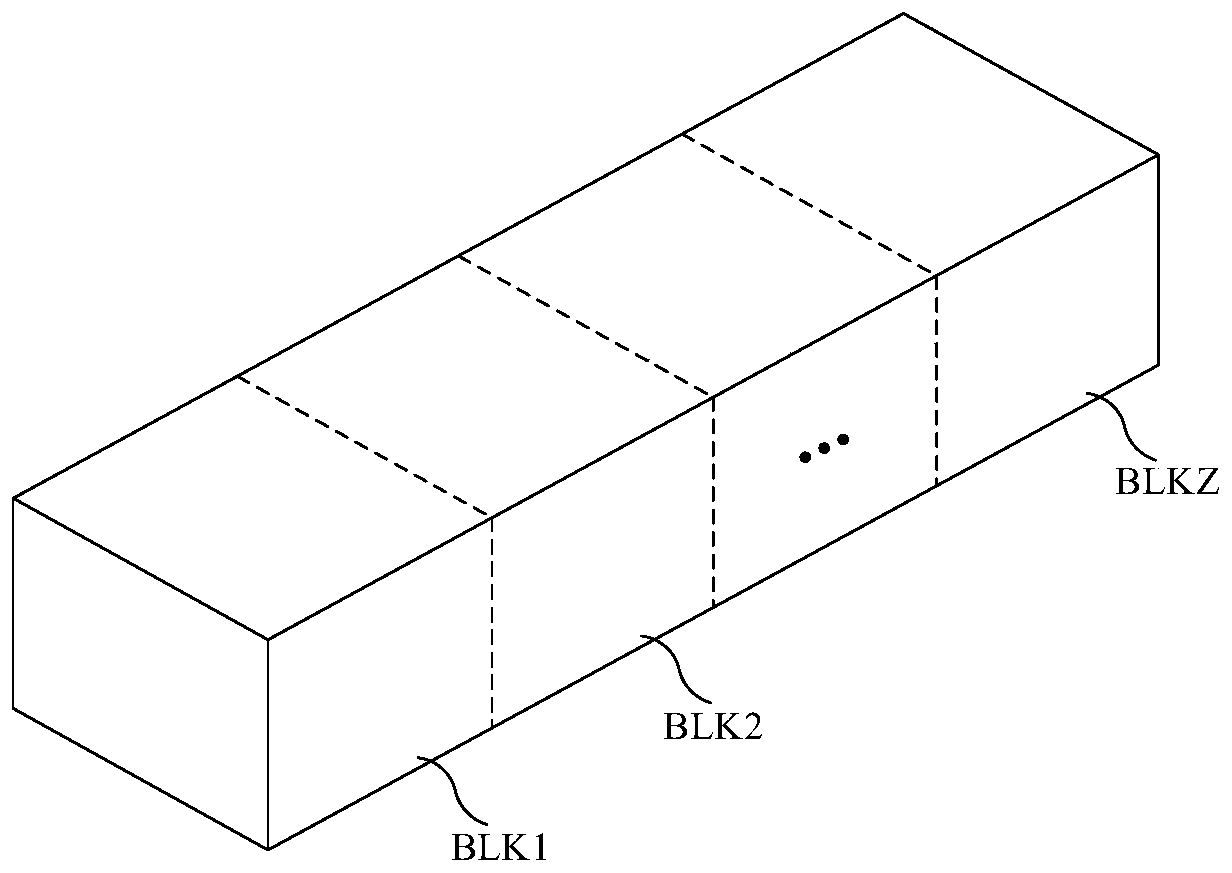

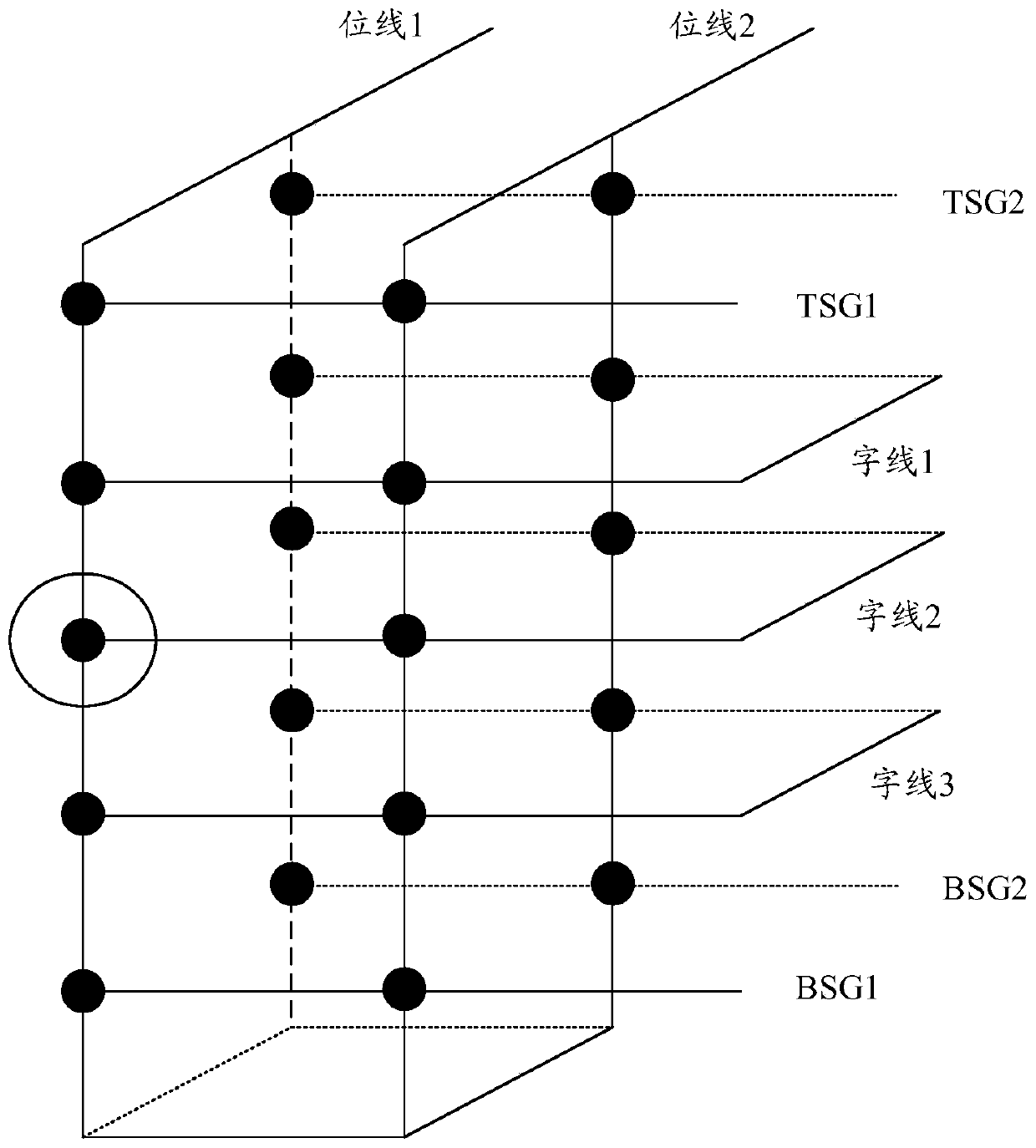

Block erasing method for NAND type flash memory

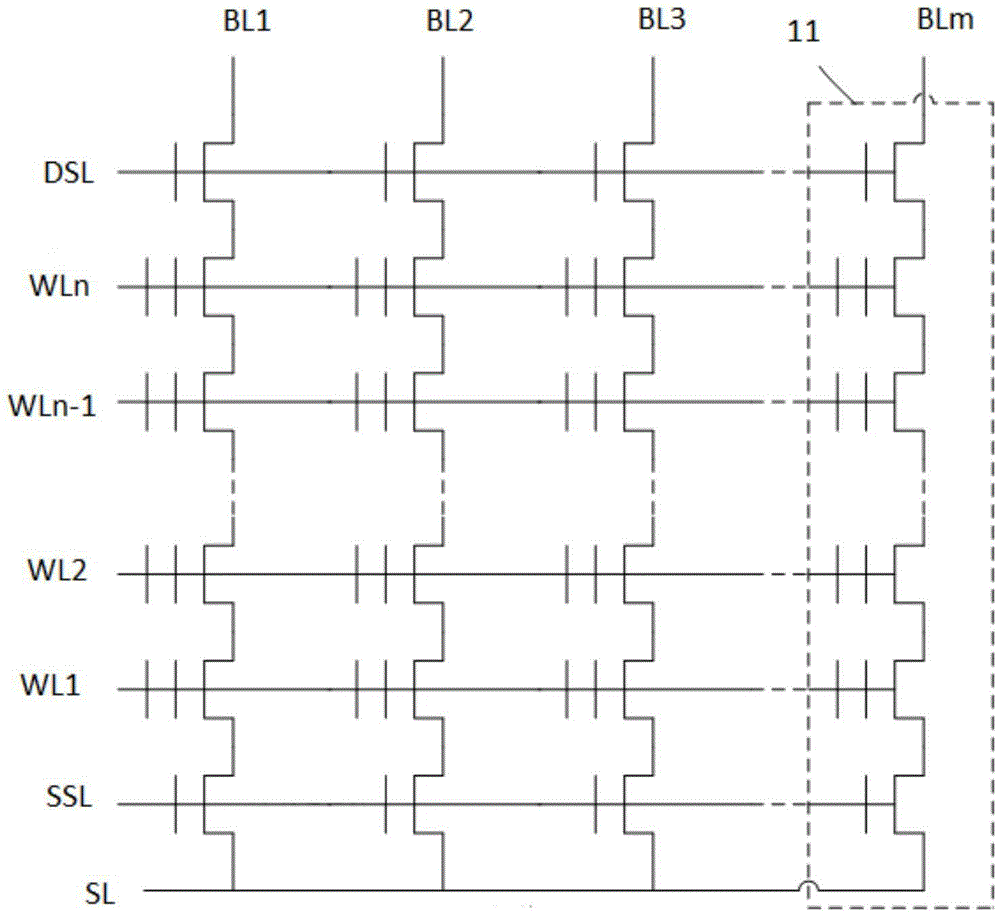

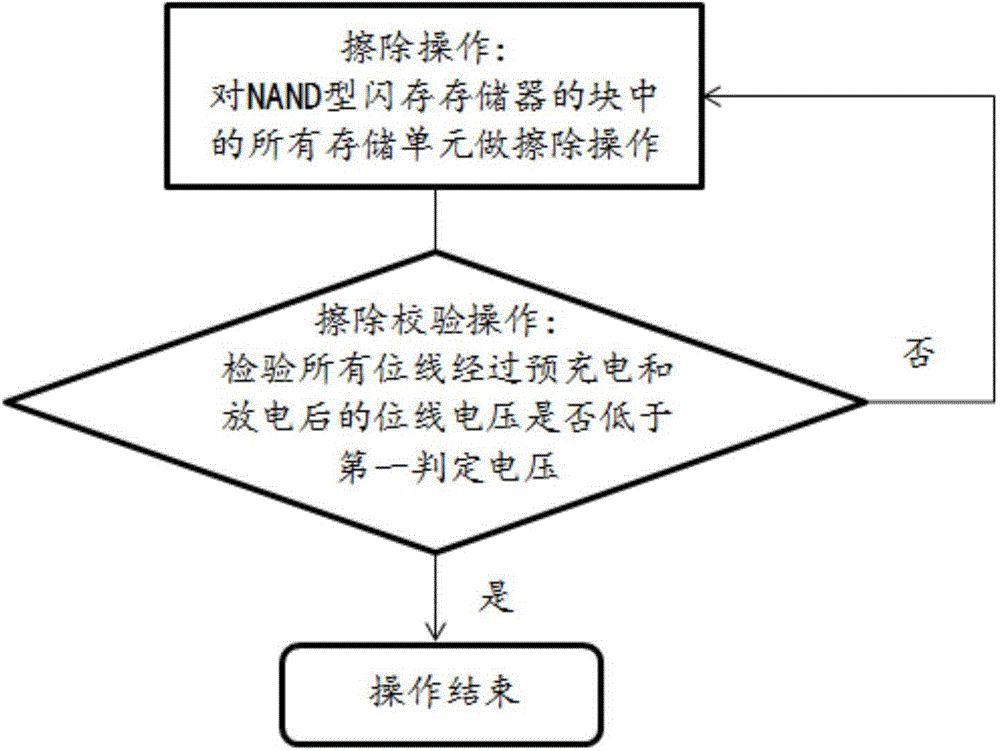

InactiveCN104934064ADoes not increase chip areaSave Channel Bootstrap EfficiencyRead-only memoriesBit lineThreshold voltage

The invention discloses a block erasing method for a NAND type flash memory. The method comprises erasing operation, erasing examination operation, soft programming operation and soft programming examination operation. By means of soft programming operation, all memory cells of a block of the NAND type flash memory are programmed together, and time for programming the memory cells can be saved greatly. By means of soft programming examination operation, all the memory cells of the block of the NAND type flash memory are examined together, the operating mode of soft programming examination operation is identical with that of erasing examination operation, and soft programming examination operation is different from erasing examination operation only in bit line discharging time or examination judgment voltage. By the adoption of the method, the threshold voltage distribution of the memory units of the block of the NAND type flash memory can be made compact, sound initial threshold voltage distribution is provided for page programming operation, so that programming time is saved, the channel bootstrap efficiency of page programming operation is improved, and programming disturbance is reduced.

Owner:HEFEI HENGSHUO SEMICON CO LTD

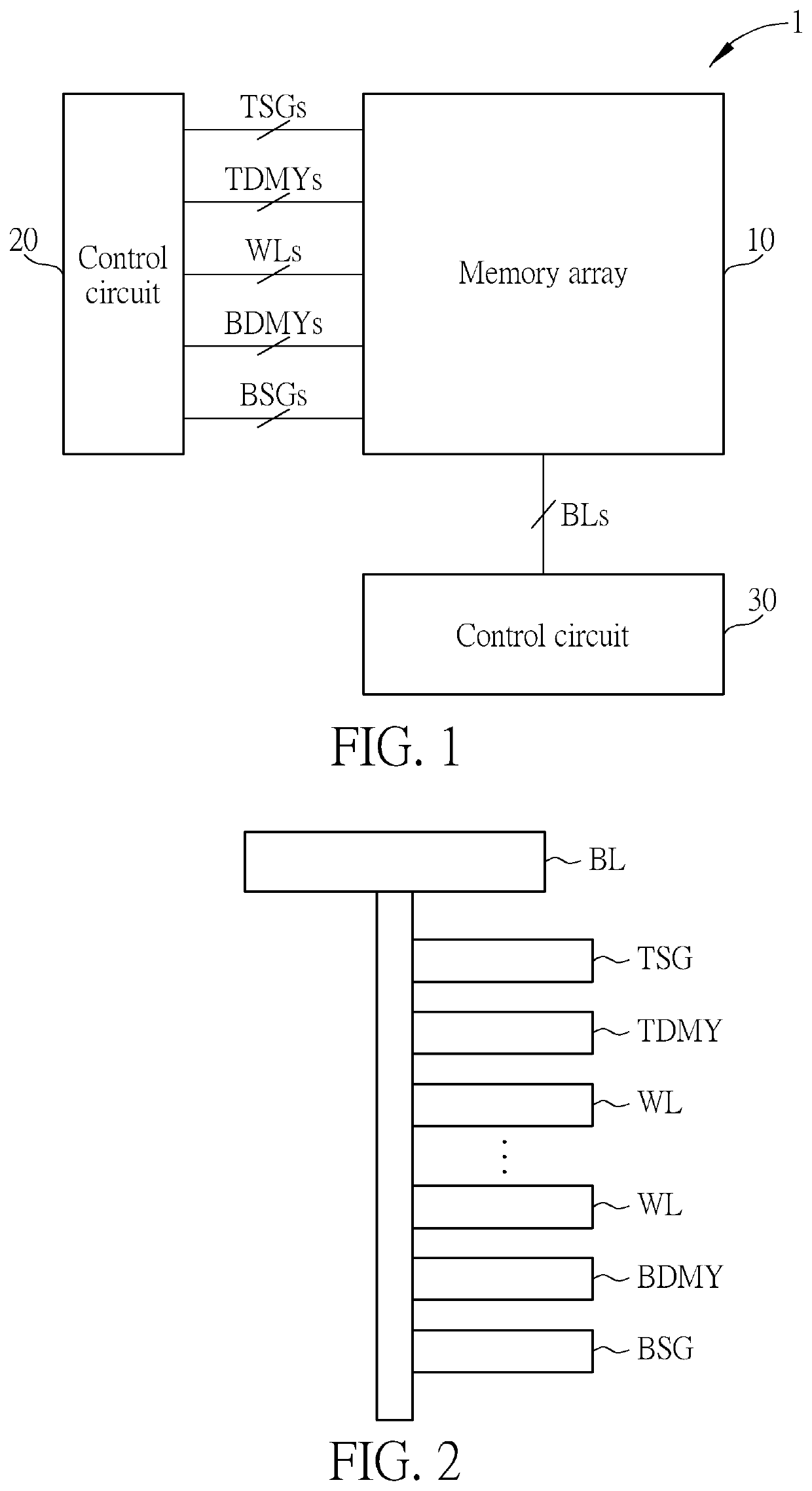

Memory control method and device and storage medium

ActiveCN110619910AProgram disturbAvoid wrong selectionRead-only memoriesSpecific timeComputer science

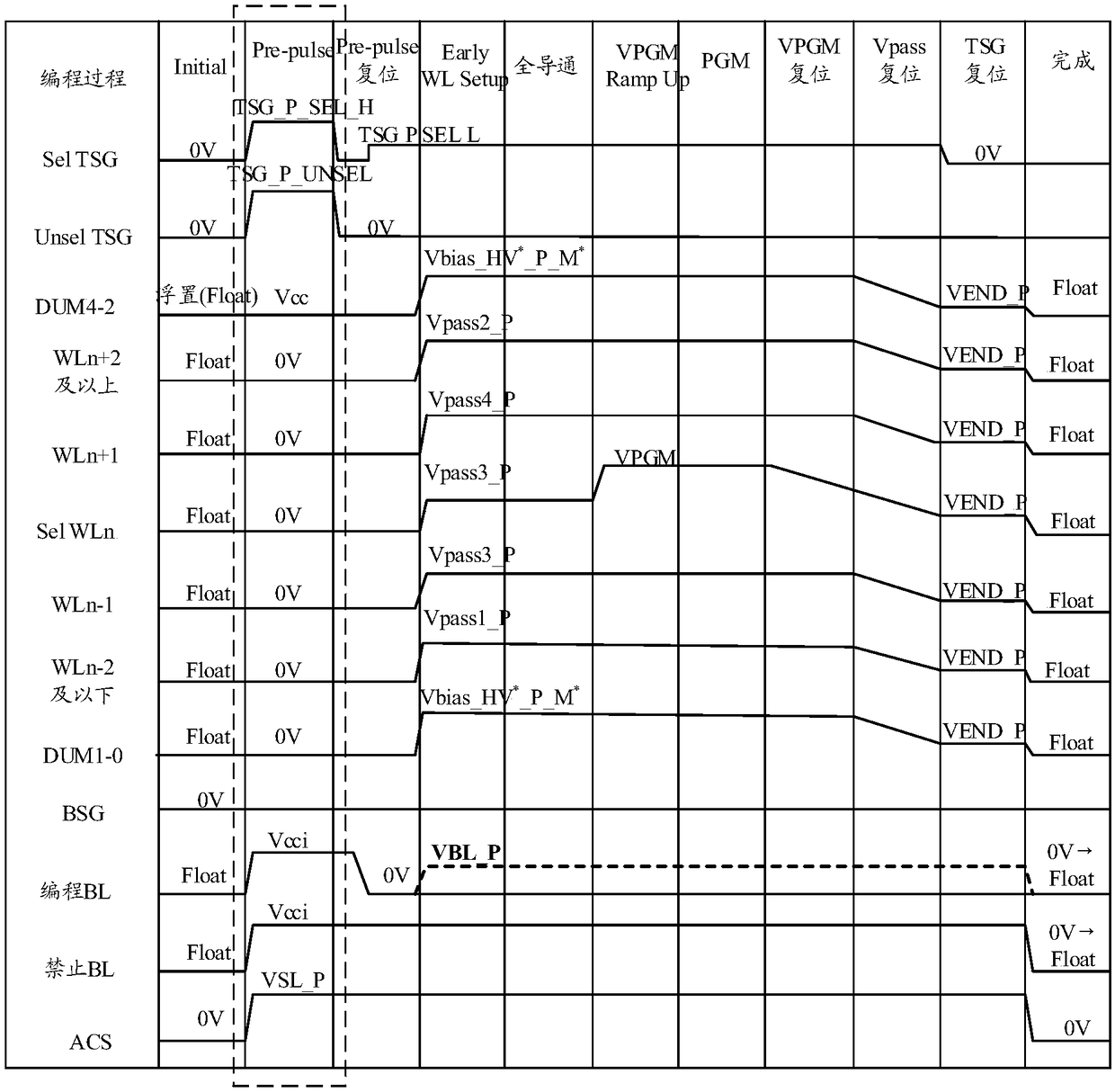

The embodiment of the invention provides a memory control method and device and a storage medium. The method comprises the following steps: carrying out programming operation on the memory, wherein afirst voltage is applied to an unselected top select gate (TSG) of the memory at least in a full-on phase of a program operation, so that the unselected TSG is in an off state, and wherein the first voltage is a negative voltage. According to the embodiment of the invention, the negative voltage is applied to the unselected TSG of the memory in the specific time period of the programming operation; therefore, the voltage of the unselected TSG is ensured to be lower than the threshold voltage of the TSG in the channel boosting period of the programming operation, so that the unselected TSG is in a completely off state, and the unselected TSG is prevented from being mistakenly selected due to the coupling effect of channel boosting. In this way, programming disturbances in the memory are reduced.

Owner:YANGTZE MEMORY TECH CO LTD

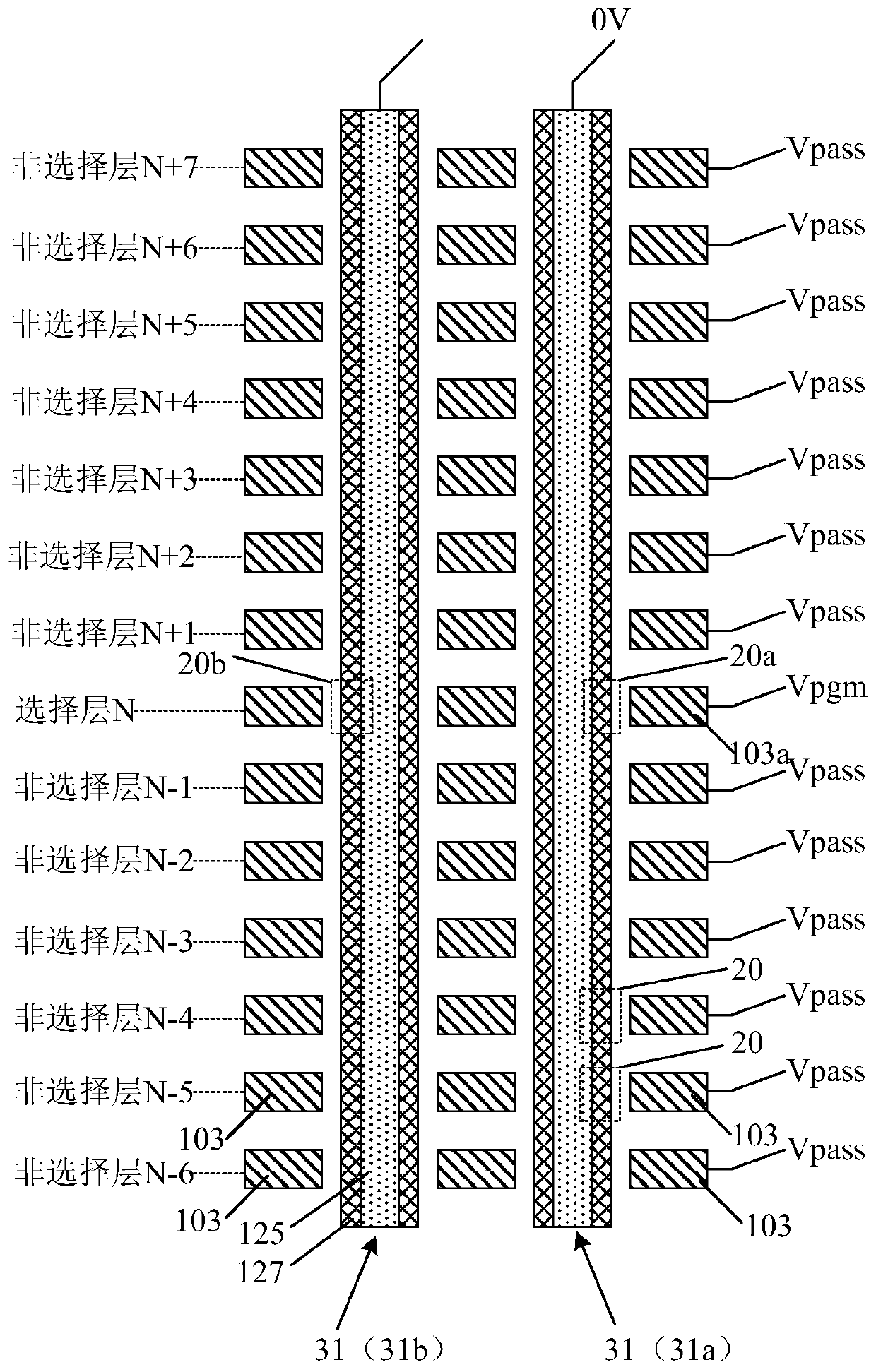

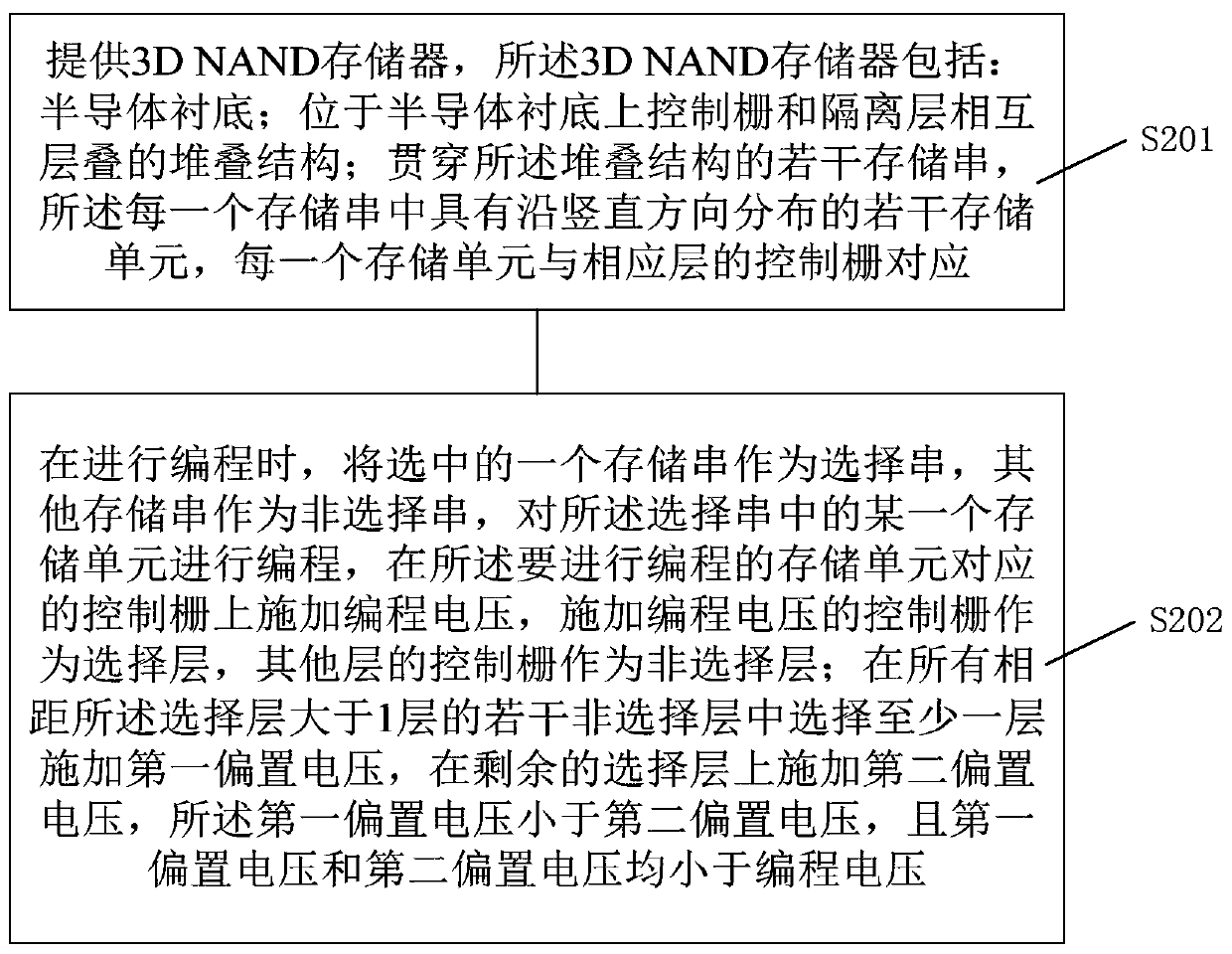

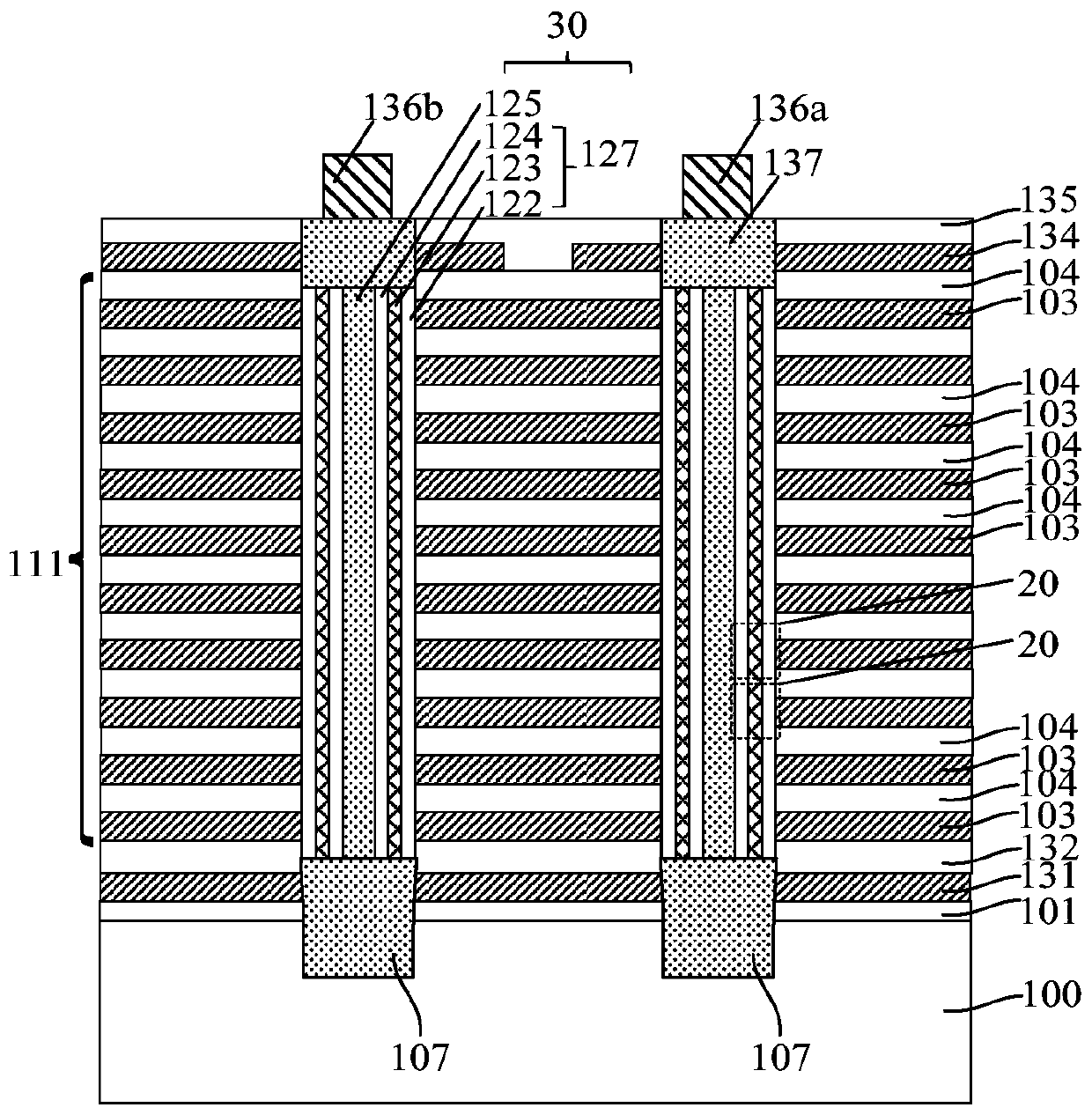

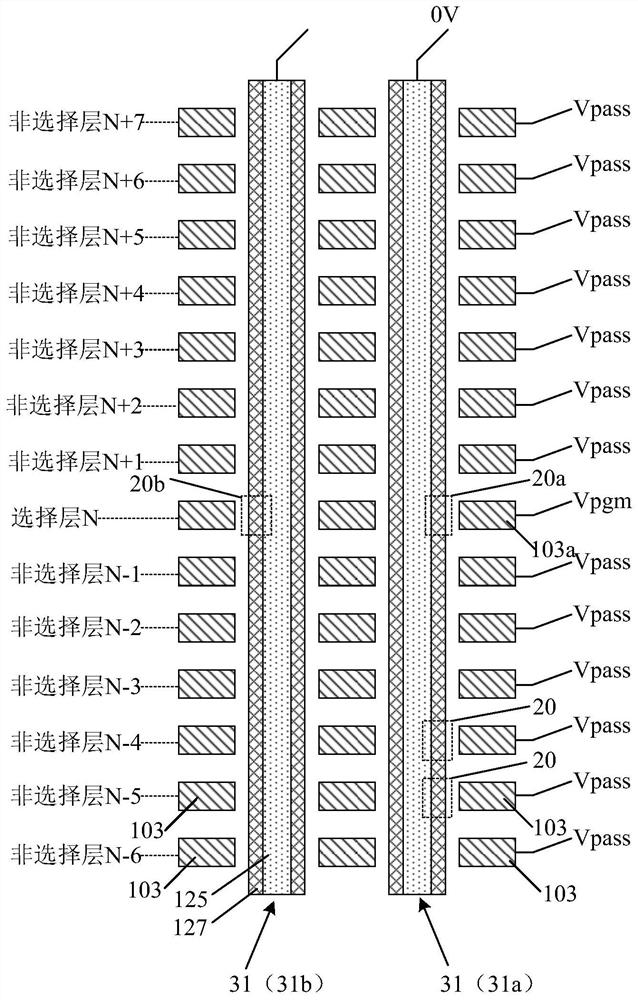

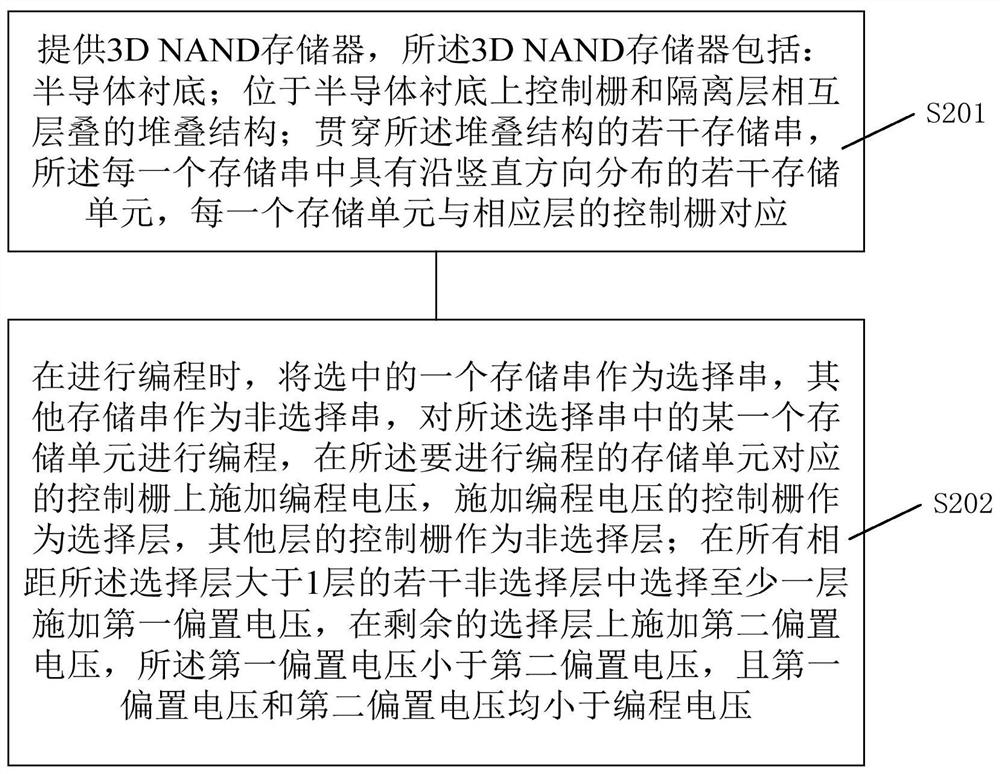

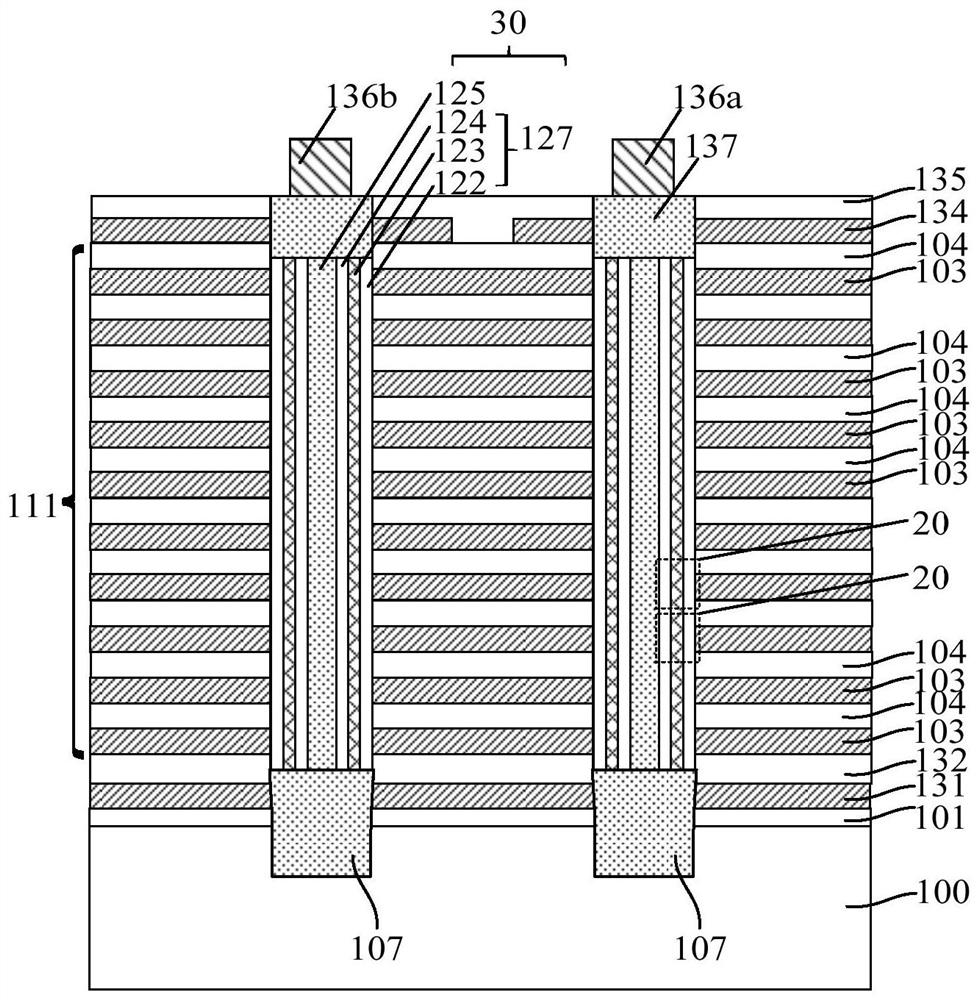

Method for reducing programming interference of 3D NAND memory

The invention discloses a method for reducing programming interference of a 3D NAND memory. The method comprises the following steps of during programming, taking the selected storage string as a selection string; taking a to-be-programmed memory cell as a control grid, taking other memory strings as non-selection strings, programming a certain memory cell in the selection strings, applying a programming voltage to the control grid corresponding to the to-be-programmed memory cell, taking the control grid to which the programming voltage is applied as a selection layer, and taking the controlgrids of other layers as non-selection layers; and selecting at least one of a plurality of non-selection layers which are more than one away from the selection layer to apply first bias voltage, andapplying second bias voltage to the rest of the selection layers, with the first bias voltage being less than the second bias voltage, with the first bias voltage and the second bias voltage being less than the programming voltage. The method provided by the invention reduces programming interference on the memory cell located on a same layer as the programmed memory cell in the non-selection string.

Owner:YANGTZE MEMORY TECH CO LTD

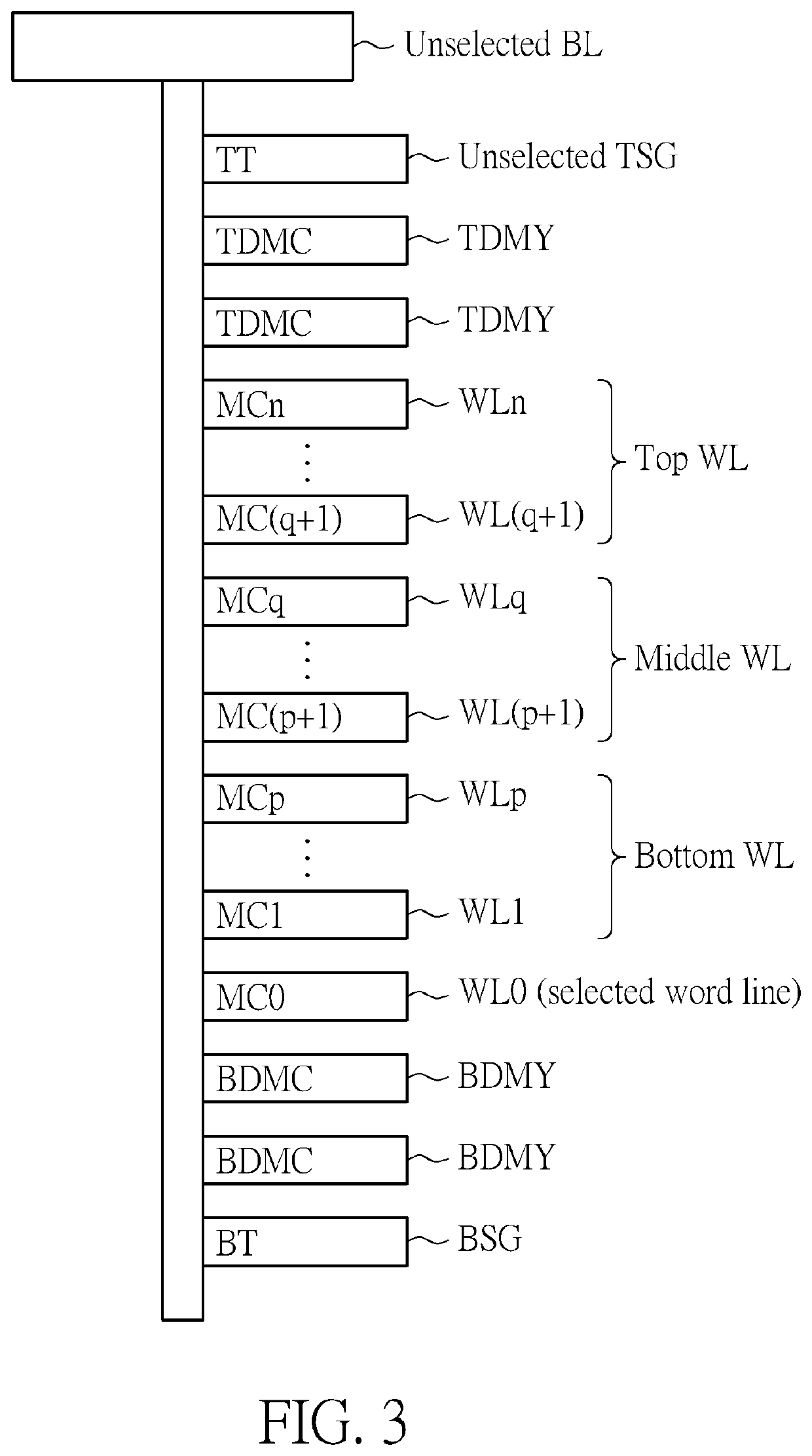

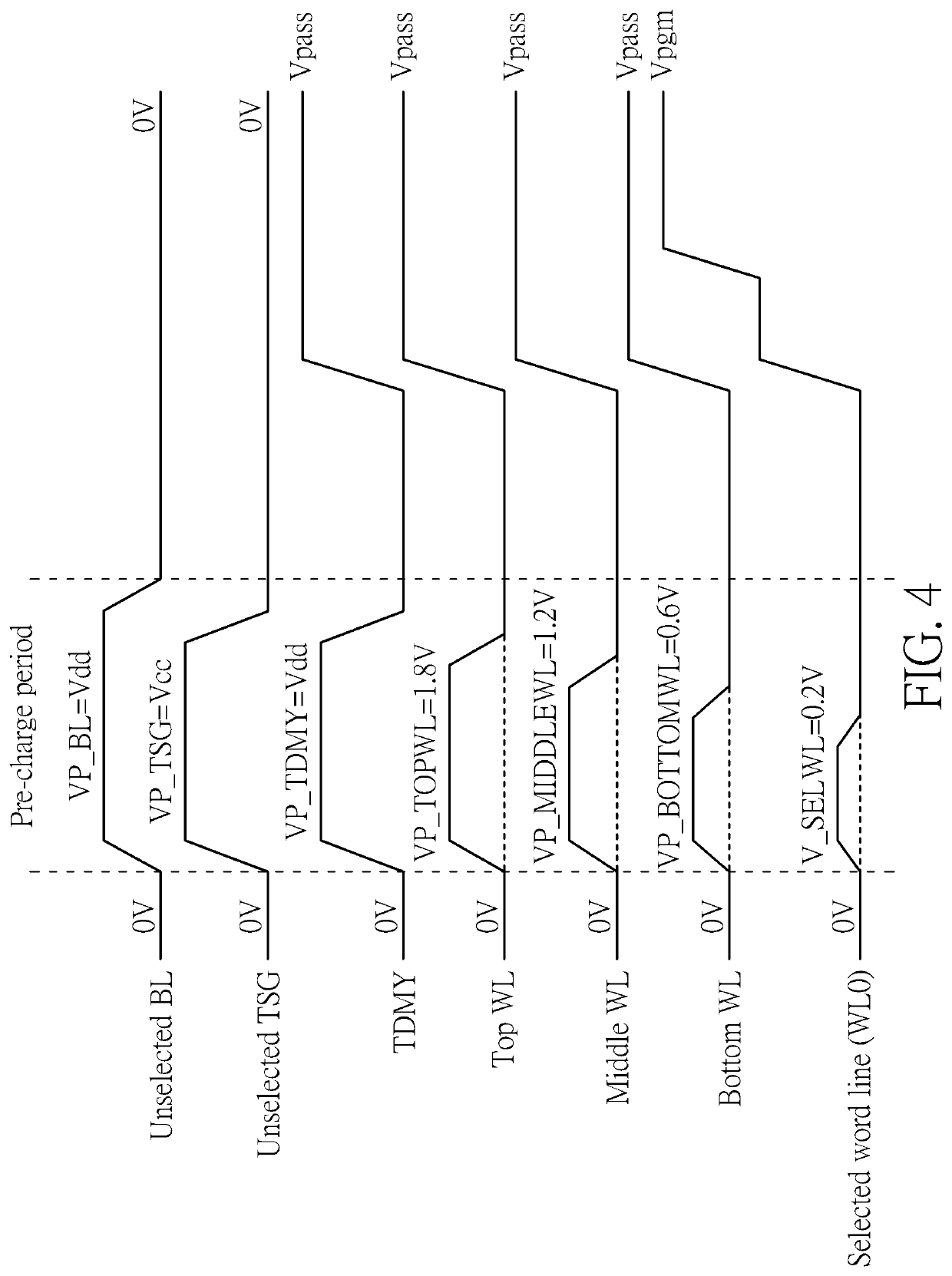

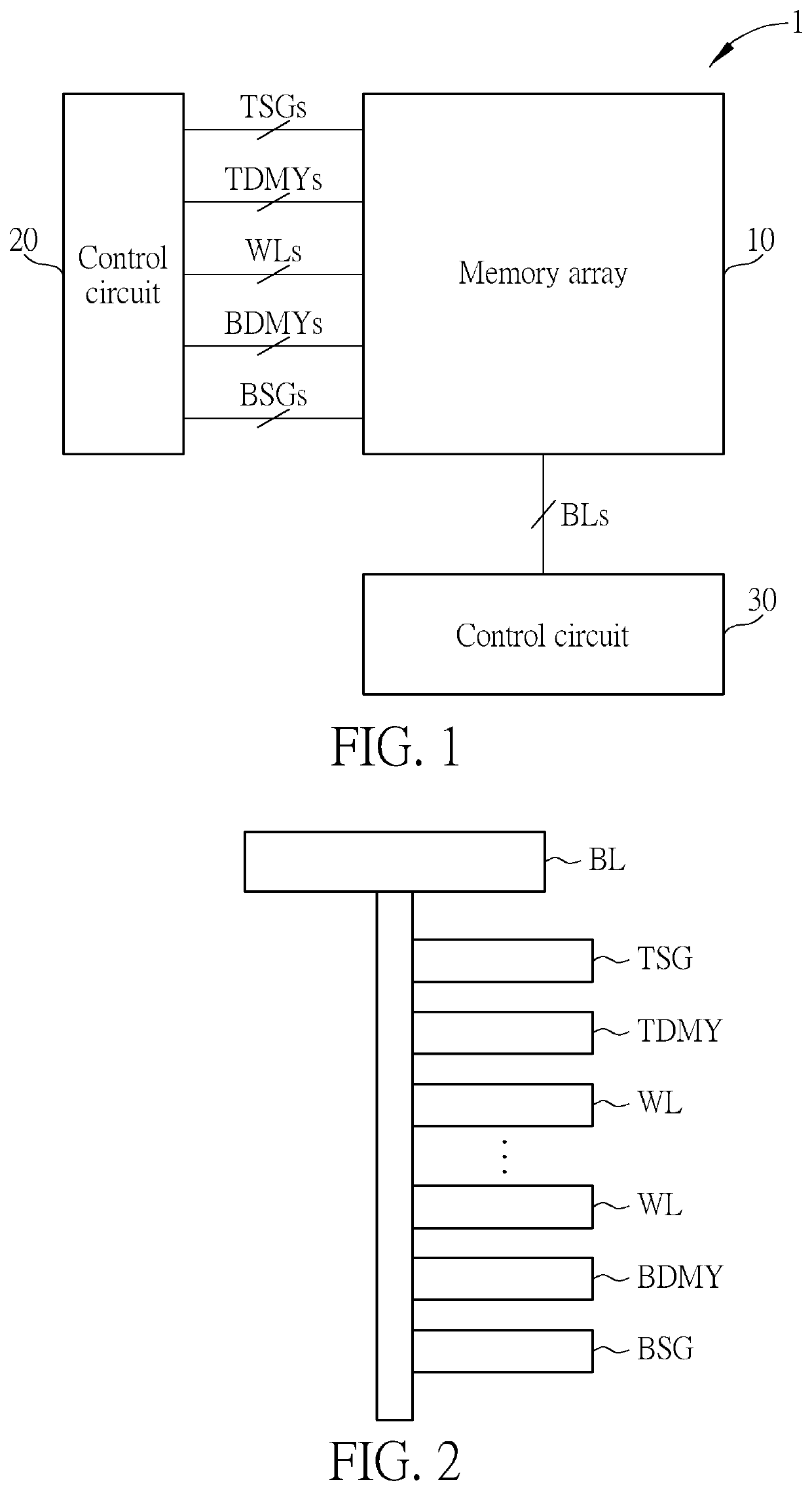

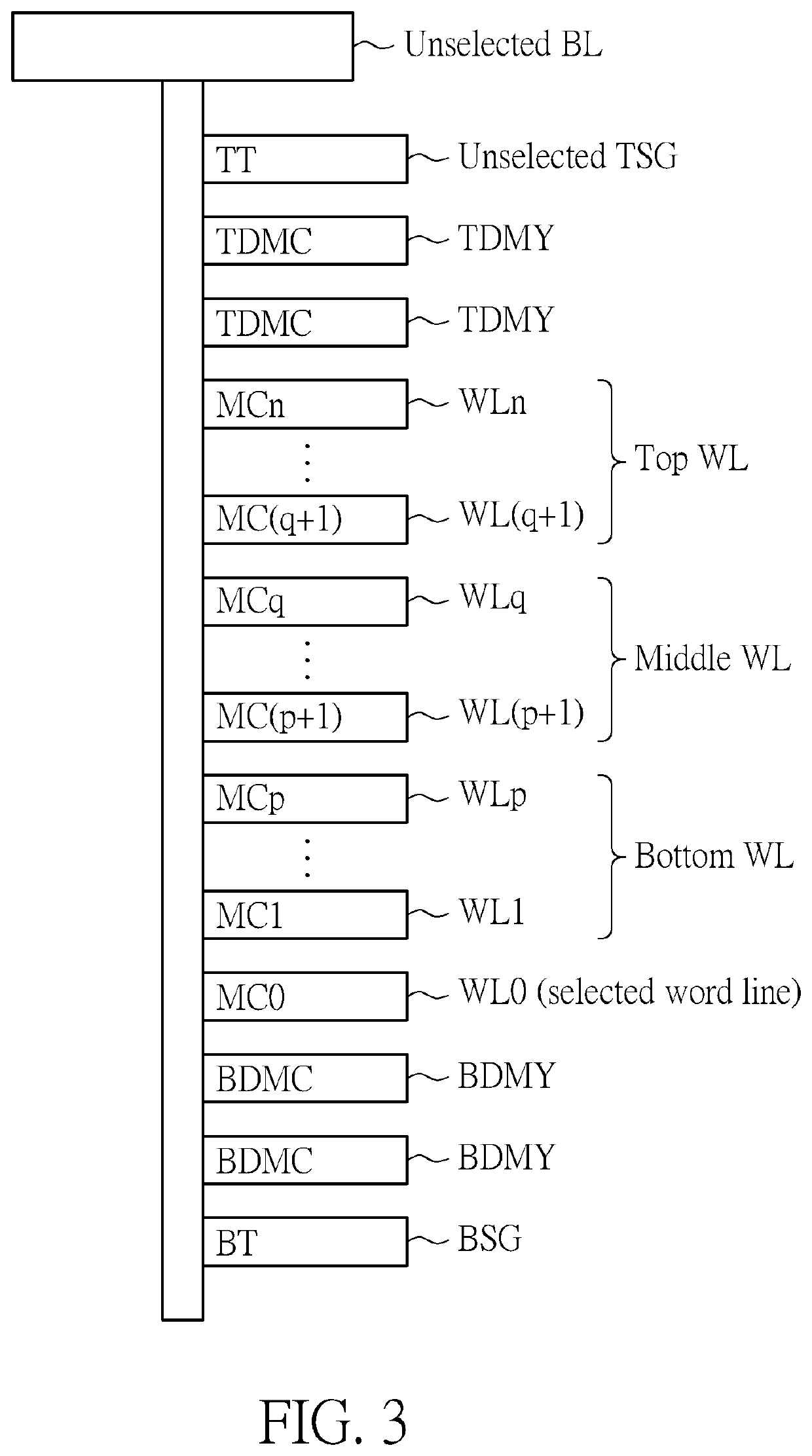

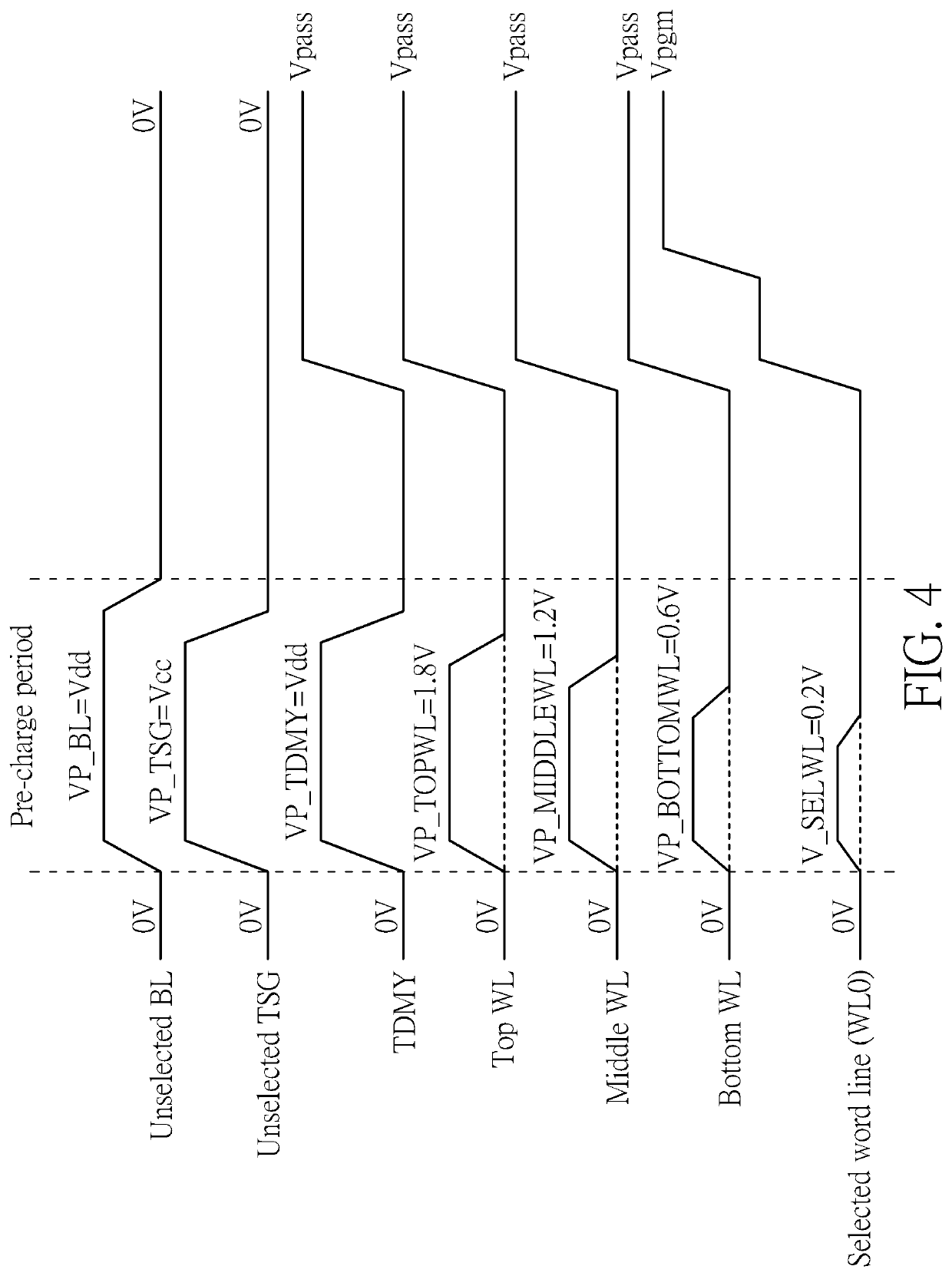

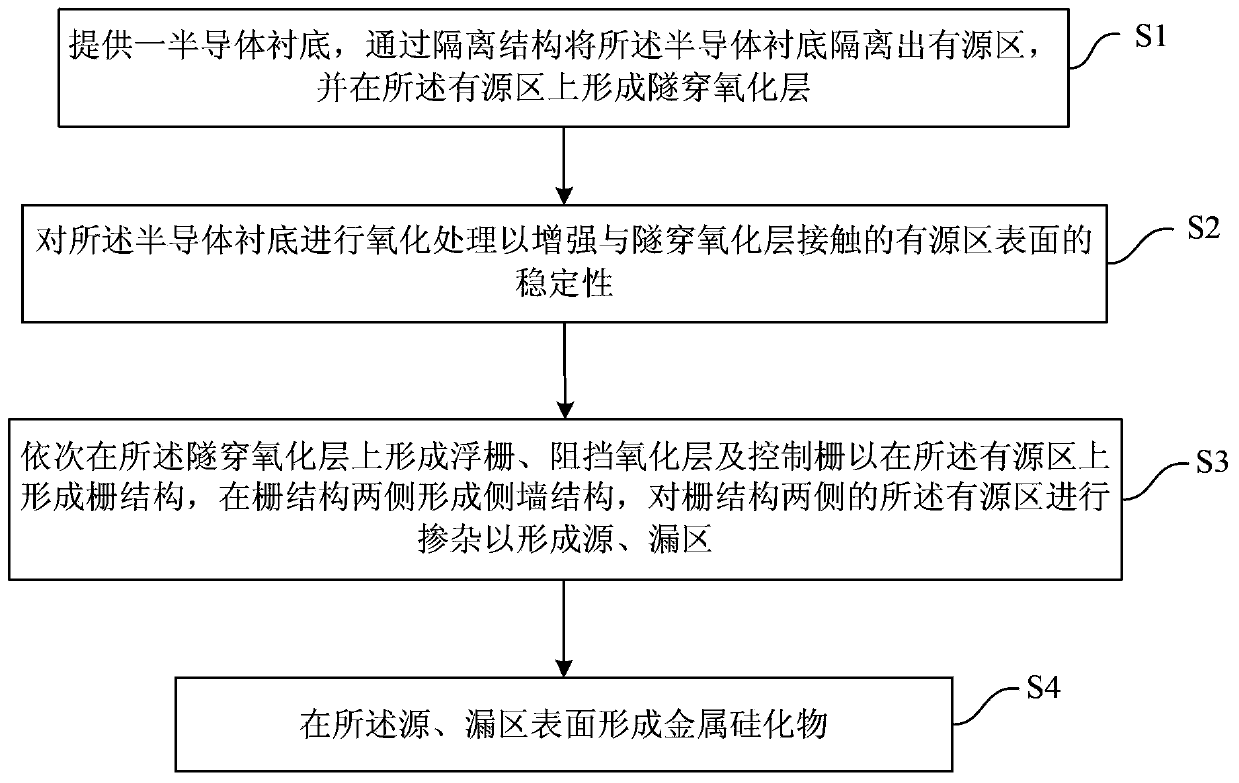

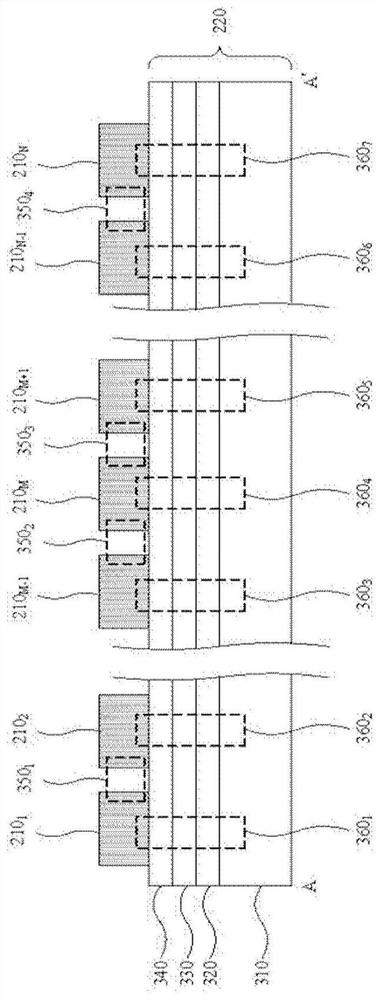

Non-volatile memory device and control method

A non-volatile memory device and a control method are provided e disclosed. The non-volatile memory device includes a memory array, a bit line, a plurality of word lines, a first control circuit, and second control circuit. The bit line is connected to a first memory string of the memory array. The plurality of word lines are connected to memory cells of the first memory string and each word line is connected to a respective memory cell. The first control circuit is configured to apply a bit line pre-pulse signal to the bit line during a pre-charge period. The second control circuit is configured to apply a word line signal to a selected word line and apply a plurality of word line pre-pulse signals to word lines disposed between a select gate line and the selected word line. Voltage levels of the plurality of word line pre-pulse signals are incremental.

Owner:YANGTZE MEMORY TECH CO LTD

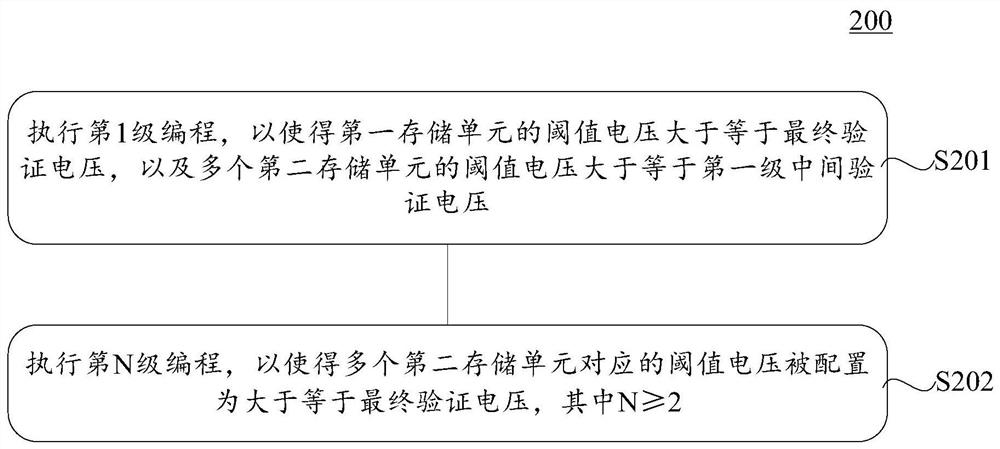

Memory system and programming method thereof

ActiveCN113284541ALower programming voltageProgram disturbRead-only memoriesDigital storageMemory cellParallel computing

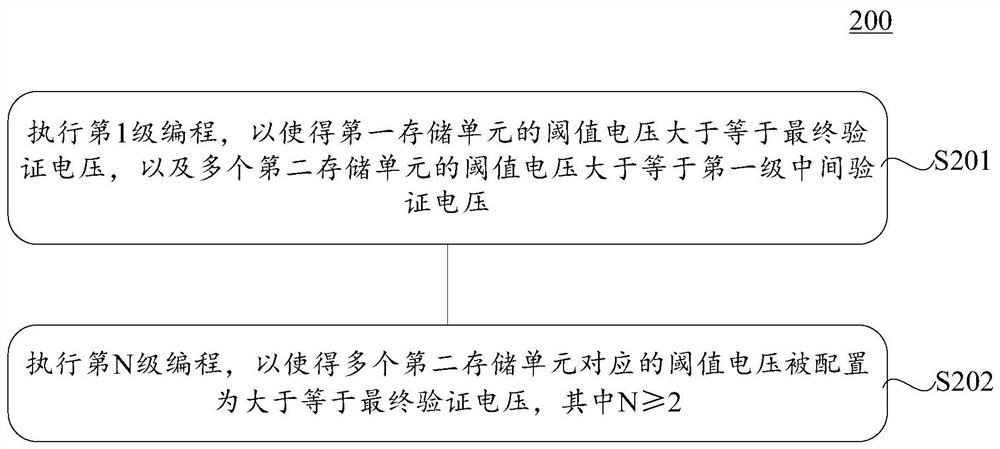

The invention provides a memory system and a programming method. Each word line of a memory connects a plurality of memory cells, the plurality of memory cells including a first memory cell and a second memory cell other than the first memory cell. The programming method includes performing first level programming to program a threshold voltage of the first memory cell to be greater than or equal to a final verify voltage of the first memory cell, and to program a threshold voltage of the second memory cell to be greater than or equal to the first-stage intermediate verification voltage, with the first-stage intermediate verification voltage of the storage unit being smaller than the final verification voltage, and the threshold voltage of the first storage unit being larger than the threshold voltage of the second storage unit; and executing Nth-level programming, and configuring the threshold voltages of the plurality of second memory cells to be greater than or equal to the final verification voltage, wherein the N is greater than or equal to 2.

Owner:YANGTZE MEMORY TECH CO LTD

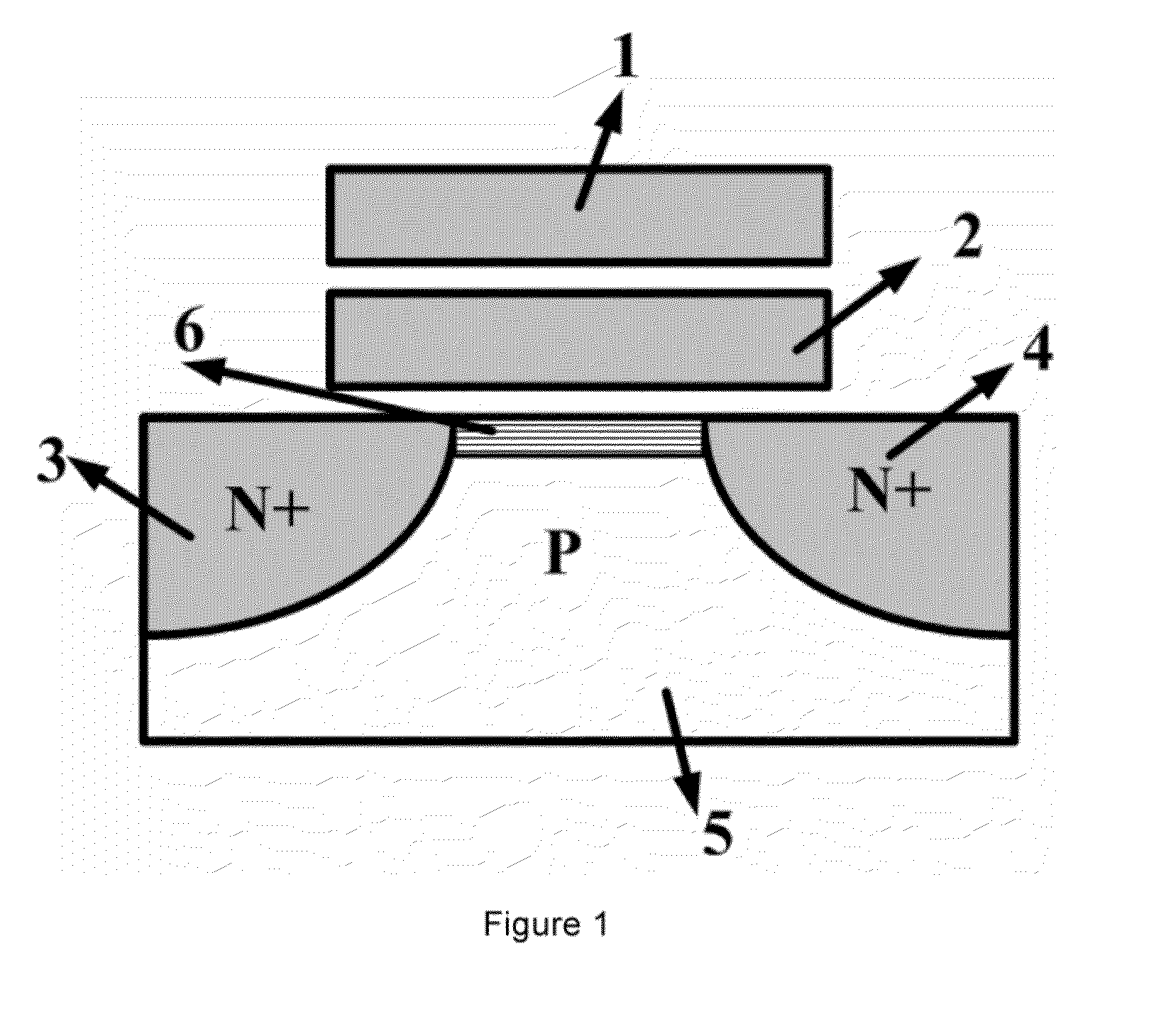

Non-volatile memory

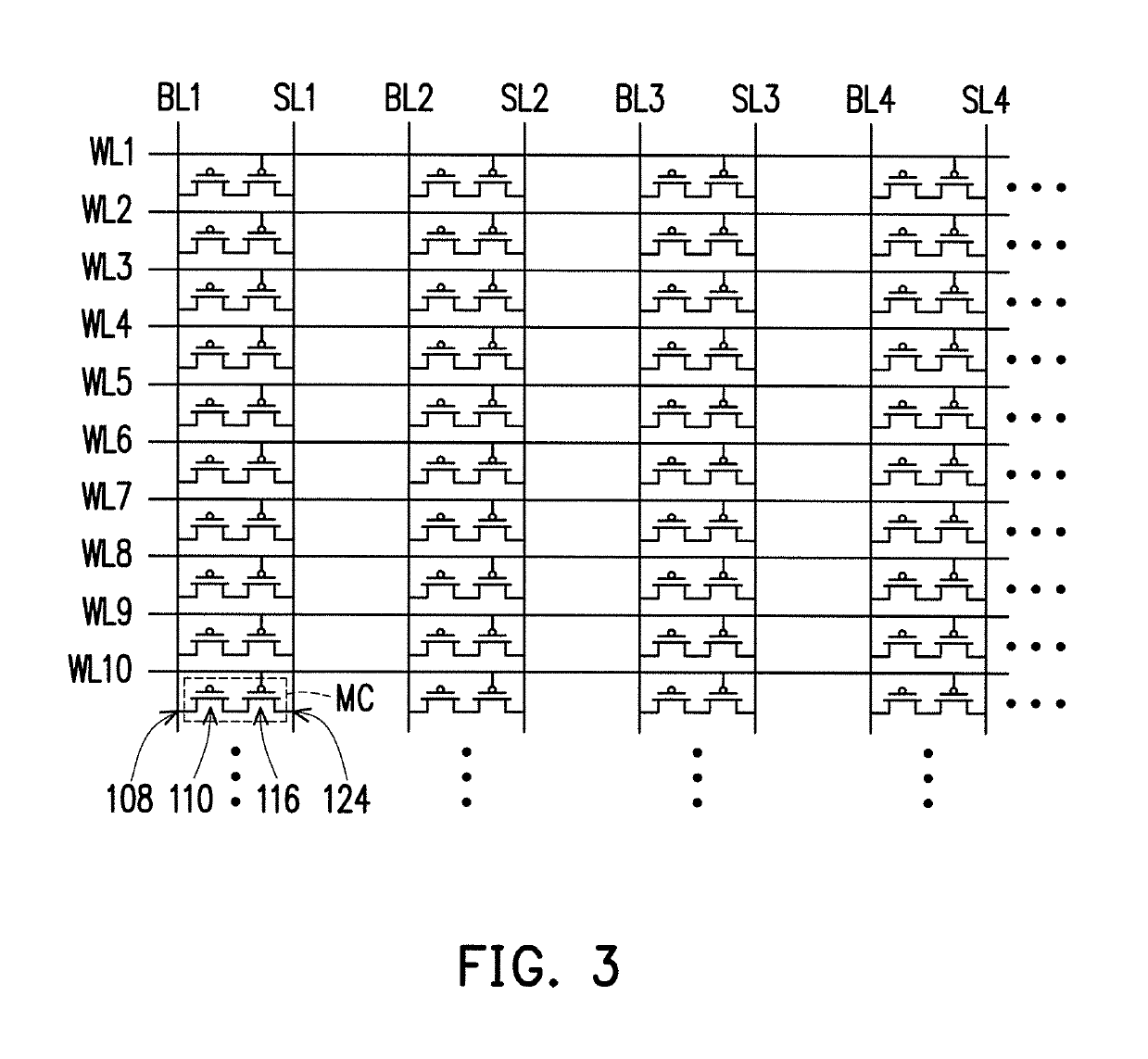

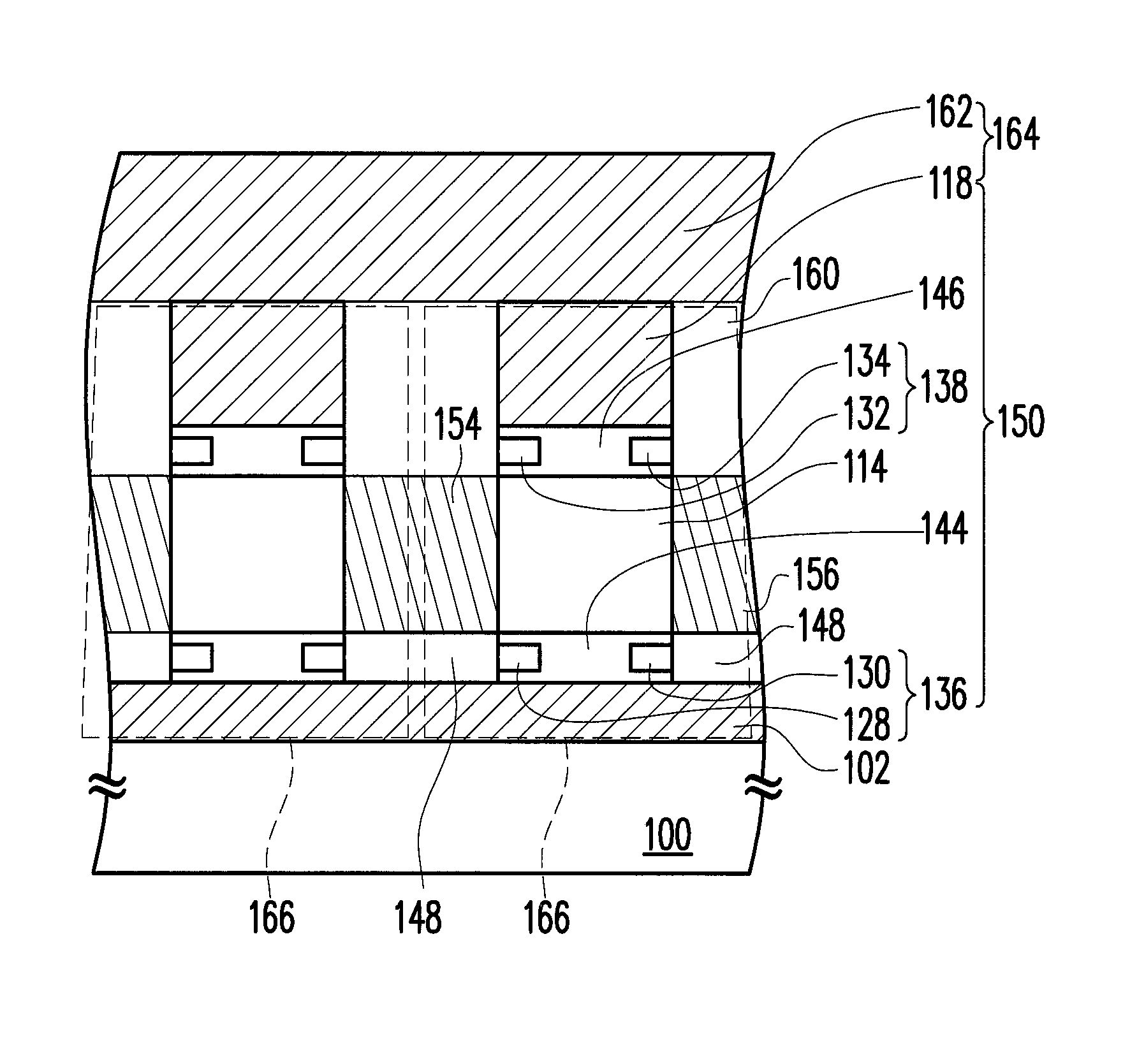

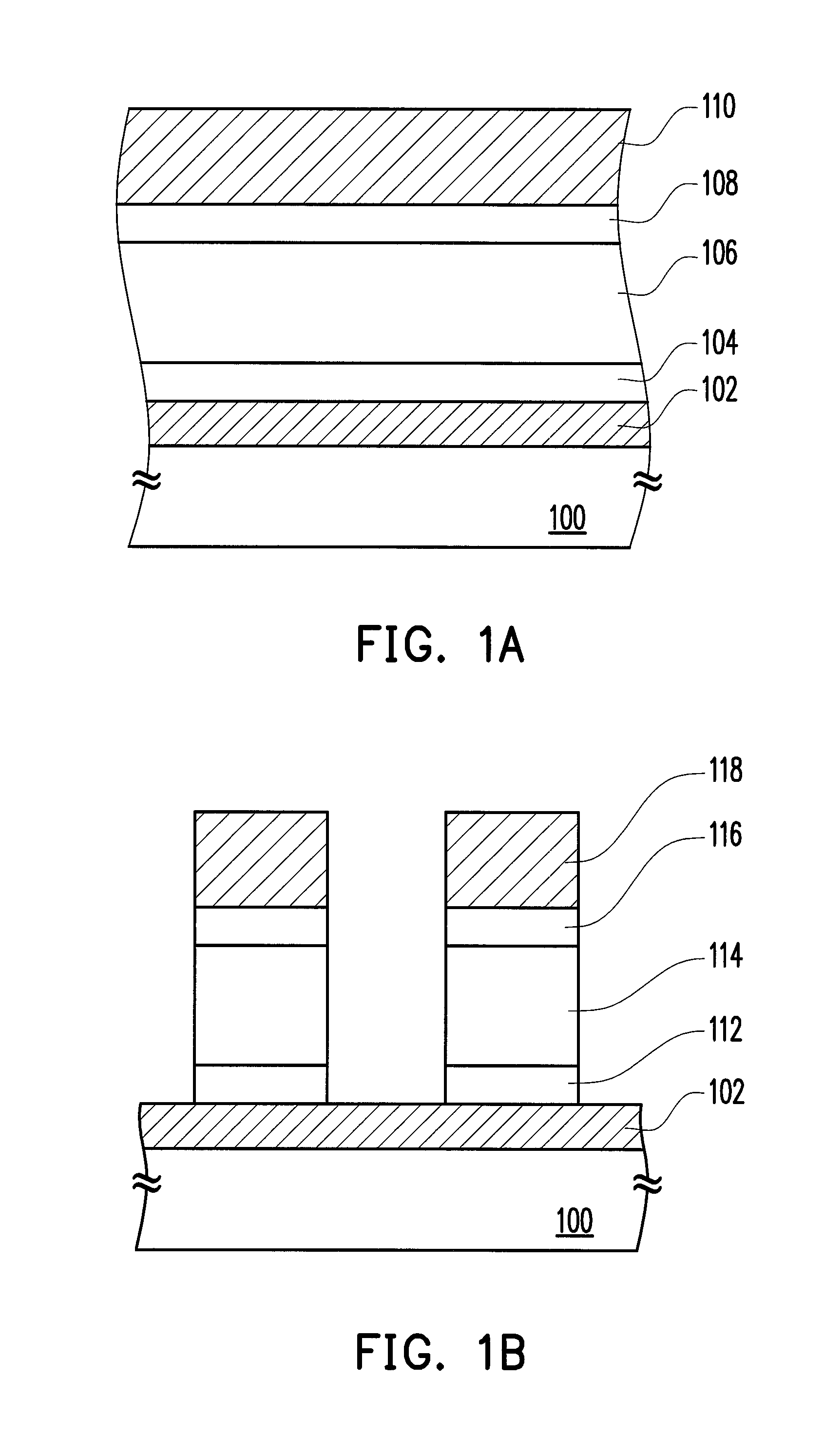

ActiveUS20180102376A1Avoid it happening againOperation efficiency can be improvedSemiconductor/solid-state device detailsSolid-state devicesEngineeringNon-volatile memory

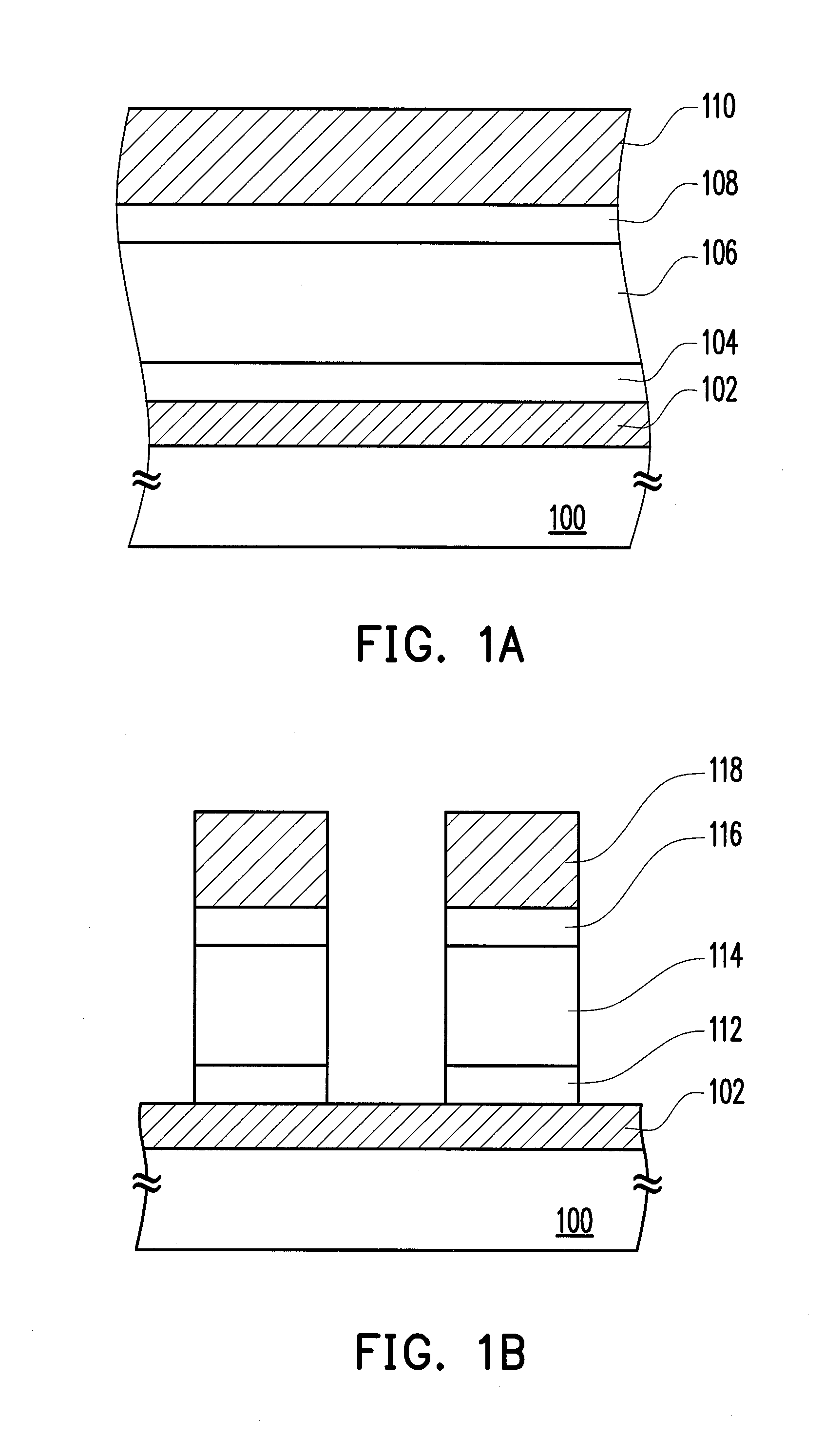

A non-volatile memory including memory cells is provided. Each of the memory cells includes a substrate, a floating gate structure, a select gate structure, and a first doped region. The floating gate structure is disposed on the substrate. The select gate structure is disposed on the substrate and located at one side of the floating gate structure. The first doped region is disposed in the substrate at another side of the floating gate structure. The first doped regions between two adjacent memory cells are adjacent to one another and separated from one another.

Owner:EMEMORY TECH INC

Non-volatile memory device and control method

ActiveUS20210118484A1Reduce disturbanceProgram disturbRead-only memoriesDigital storageEmbedded systemMemory cell

A non-volatile memory device and a control method are provided e disclosed. The non-volatile memory device includes a memory array, a bit line, a plurality of word lines, a first control circuit, and second control circuit. The bit line is connected to a first memory string of the memory array. The plurality of word lines are connected to memory cells of the first memory string and each word line is connected to a respective memory cell. The first control circuit is configured to apply a bit line pre-pulse signal to the bit line during a pre-charge period. The second control circuit is configured to apply a word line signal to a selected word line and apply a plurality of word line pre-pulse signals to word lines disposed between a select gate line and the selected word line. Voltage levels of the plurality of word line pre-pulse signals are incremental.

Owner:YANGTZE MEMORY TECH CO LTD

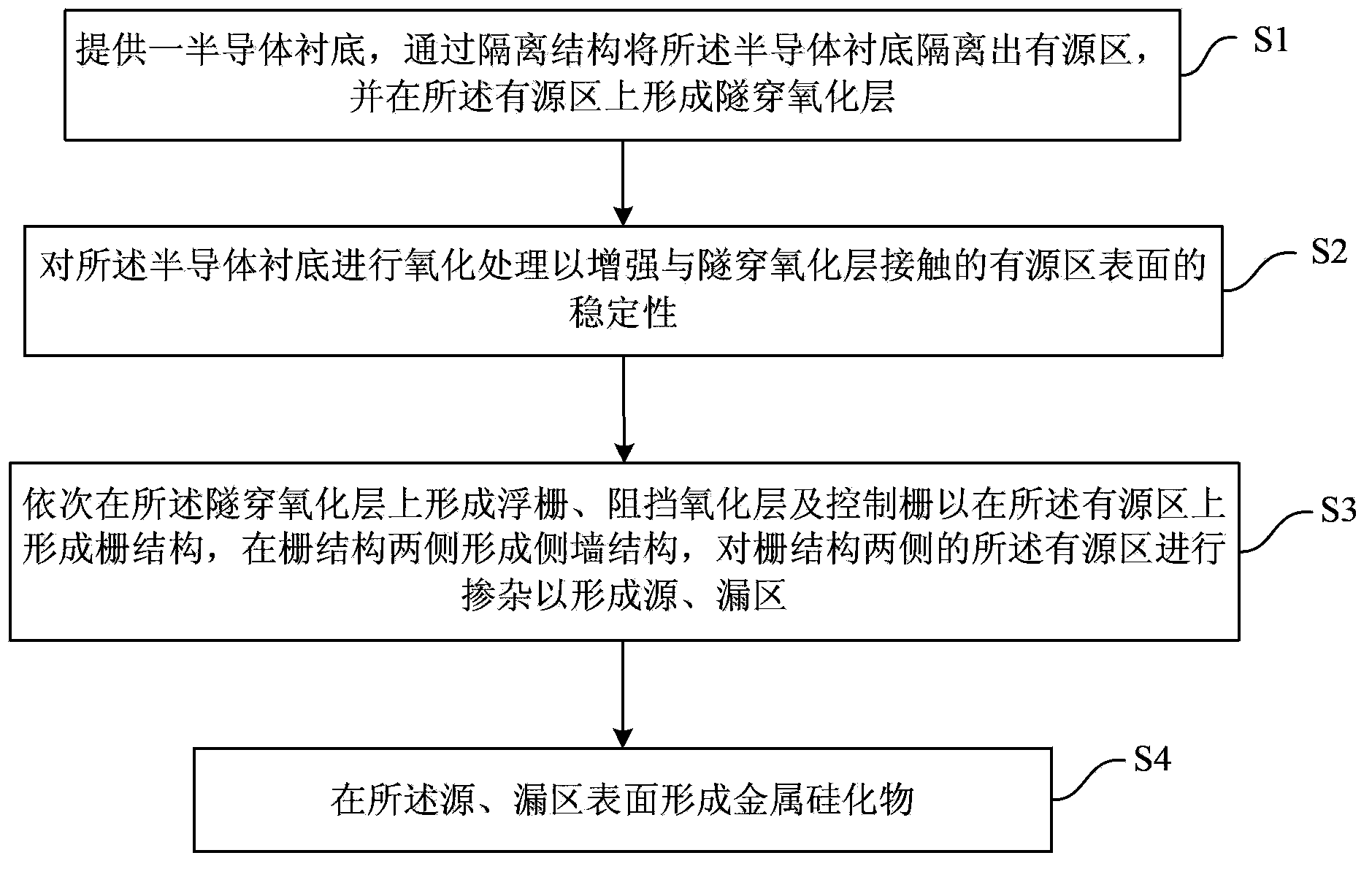

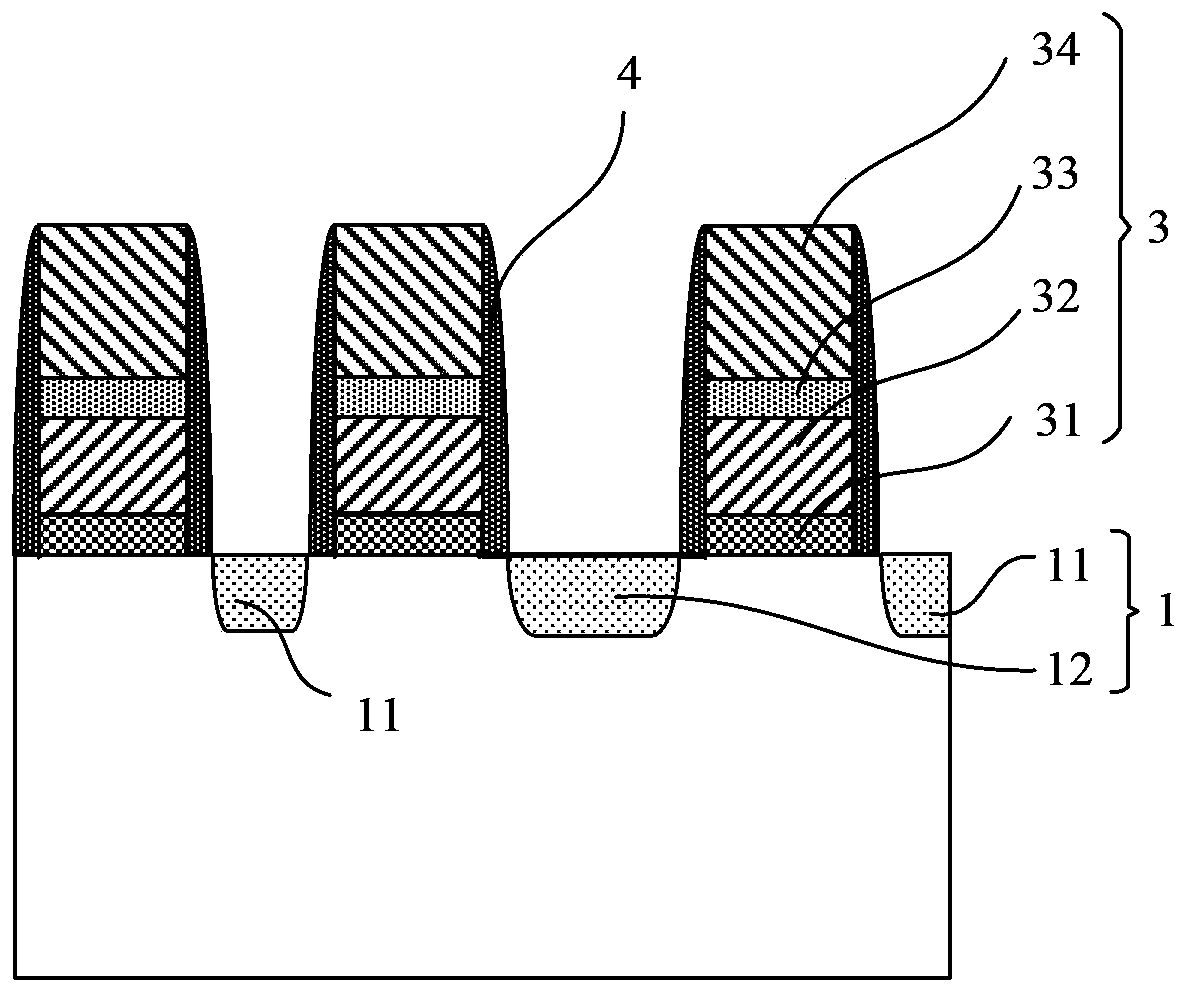

A kind of preparation method of flash memory

ActiveCN104347515BReduce deposition thicknessImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingPhysical chemistryMetal silicide

The invention provides a method for preparing a flash memory. The invention performs oxidation treatment on a semiconductor substrate formed with a tunnel oxide layer before forming a floating gate, so as to enhance the stability of the surface of the active region in contact with the tunnel oxide layer. Simultaneously, the present invention reduces the deposition thickness of the metal layer that prepares metal silicide and carries out the heat treatment that will form metal silicide in two stages, helps to strengthen the stability and the surface uniformity of metal silicide, wherein, the second heat treatment Phase is higher temperature and shorter than the first phase. The present invention uses the above method to prevent the metal silicide from irregularly corroding to the contact surface of the gate structure and the active region, thereby reducing the programming interference caused by the irregular erosion, achieving the purpose of suppressing the programming interference of the flash memory, and further avoiding The reliability of the drain region is reduced during cycle operation, while avoiding the data retention of the flash memory to generate tail bits.

Owner:SEMICON MFG INT (SHANGHAI) CORP

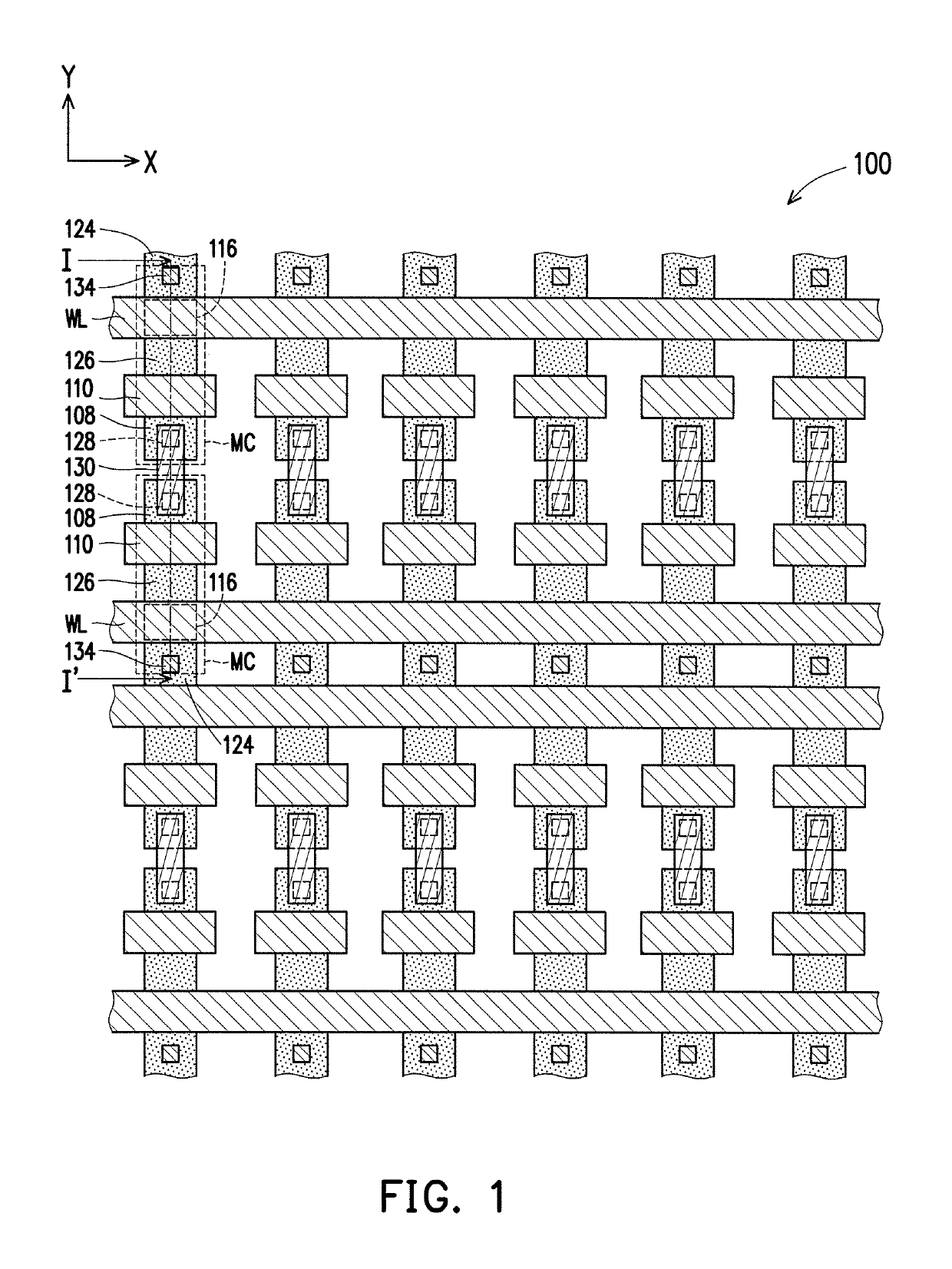

Memory structure and fabricating method thereof

ActiveUS20120326222A1Fix bugsProgram disturbSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric structure

A memory structure including a memory cell is provided, and the memory cell includes following elements. A first gate is disposed on a substrate. A stacked structure includes a first dielectric structure, a channel layer, a second dielectric structure and a second gate disposed on the first gate, a first charge storage structure disposed in the first dielectric structure and a second charge storage structure disposed in the second dielectric structure. At least one of the first charge storage structure and the second charge storage structure includes two charge storage units which are physically separated. A first dielectric layer is disposed on the first gate at two sides of the stacked structure. A first source and drain and a second source and drain are disposed on the first dielectric layer and located at two sides of the channel layer.

Owner:MACRONIX INT CO LTD

Preparation method for flash memory

ActiveCN104347515AReduce deposition thicknessImprove stabilitySemiconductor/solid-state device manufacturingSalicideMetal silicide

The invention provides a preparation method for a flash memory. Oxidation processing is performed on a semiconductor substrate with formation of a tunneling oxidation layer before formation of a floating gate so that stability of an active region surface contacted with the tunneling oxidation layer is enhanced. Meanwhile, deposition thickness of a metal layer for preparation of a metal silicide is reduced, and heat treatment for formation of the metal silicide is performed via two divided phases so that enhancement of stability and surface uniformity of the metal silicide is facilitated, wherein temperature of the second phase of heat treatment is higher than that of the first phase, and time of the second phase of heat treatment is shorter than that of the first phase. With application of the aforementioned method, the metal silicide can be prevented from irregularly eroding to the gate structure and the contact surface of the active region so that programming interference caused by irregular erosion can be reduced, an objective of suppressing programming interference of the flash memory is achieved, reduction of reliability of a drain region in cycle operation can be further avoided, and generation of tail bits of data retention of the flash memory can also be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

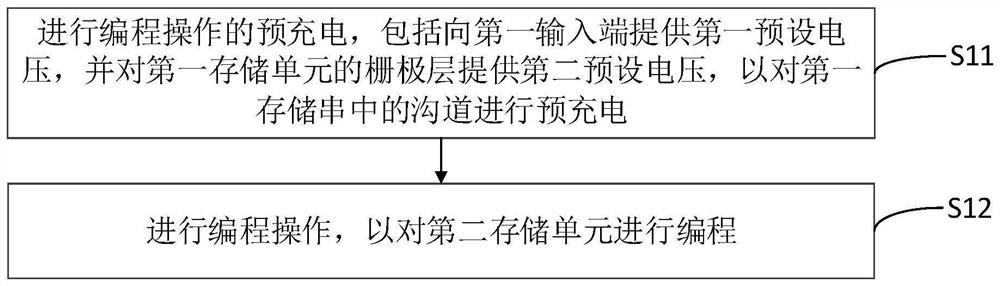

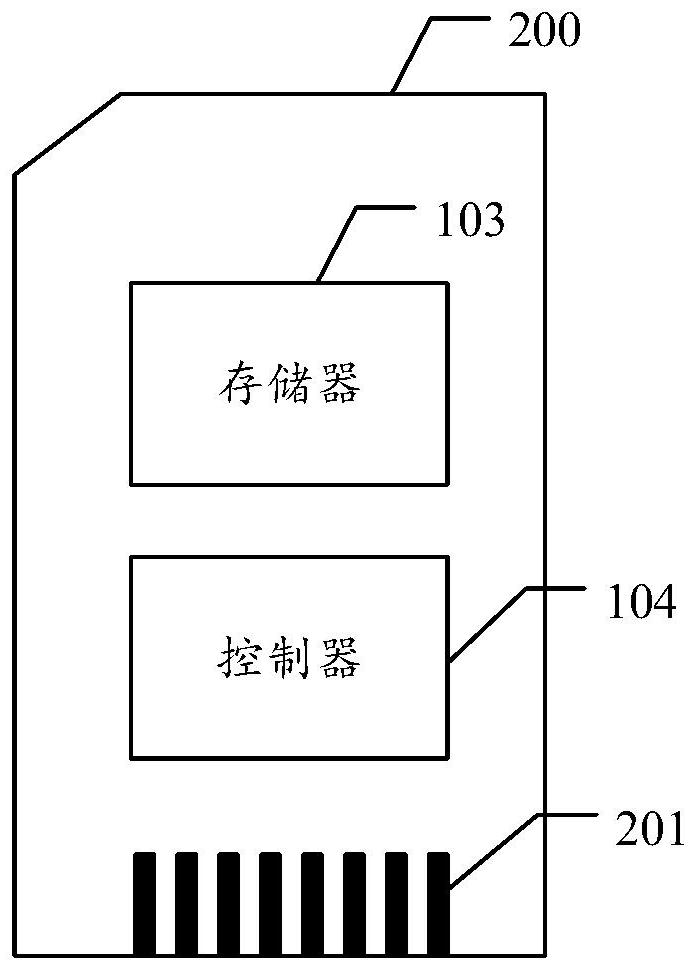

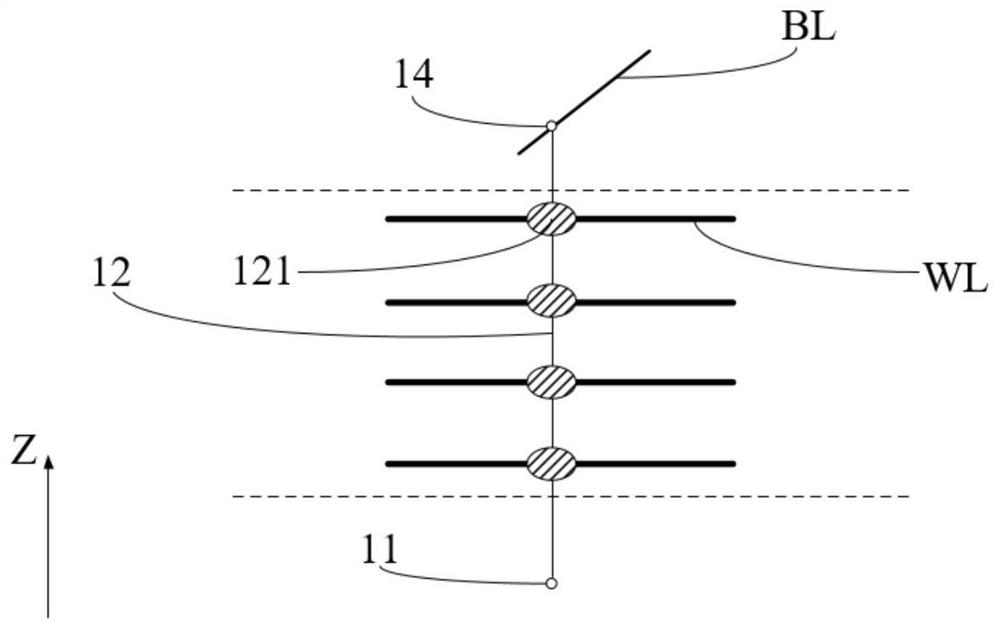

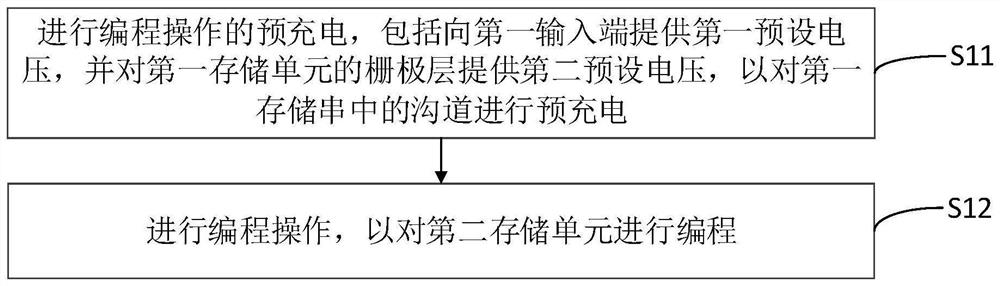

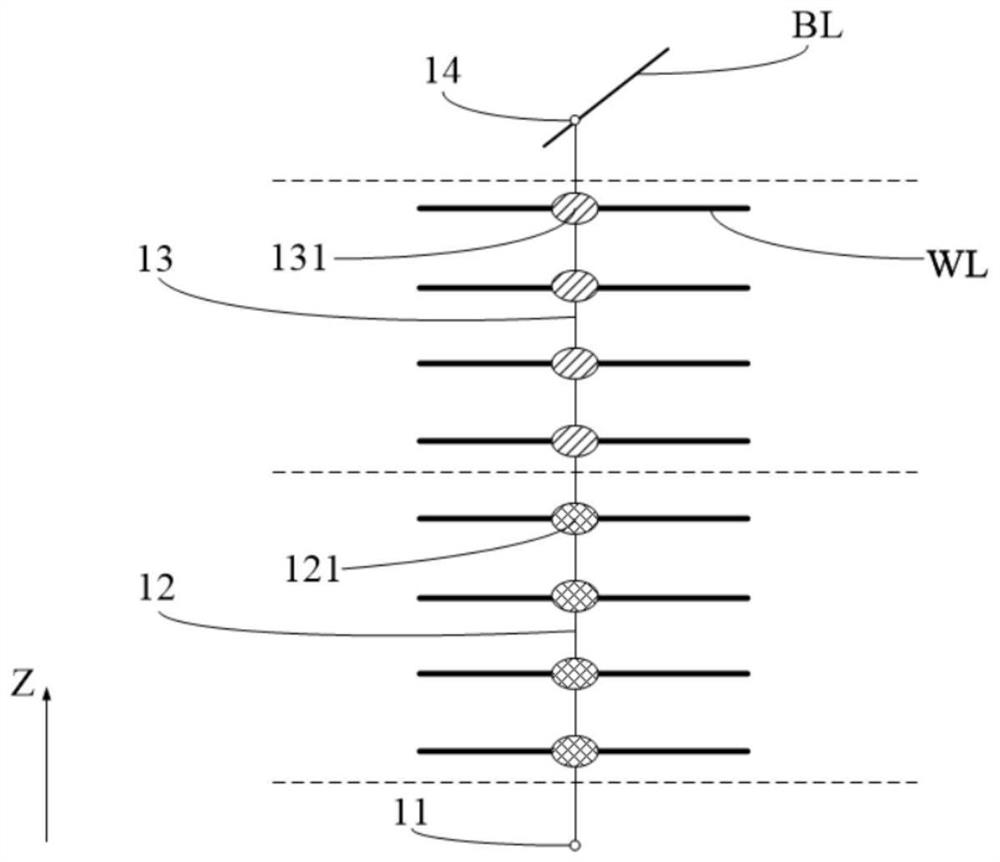

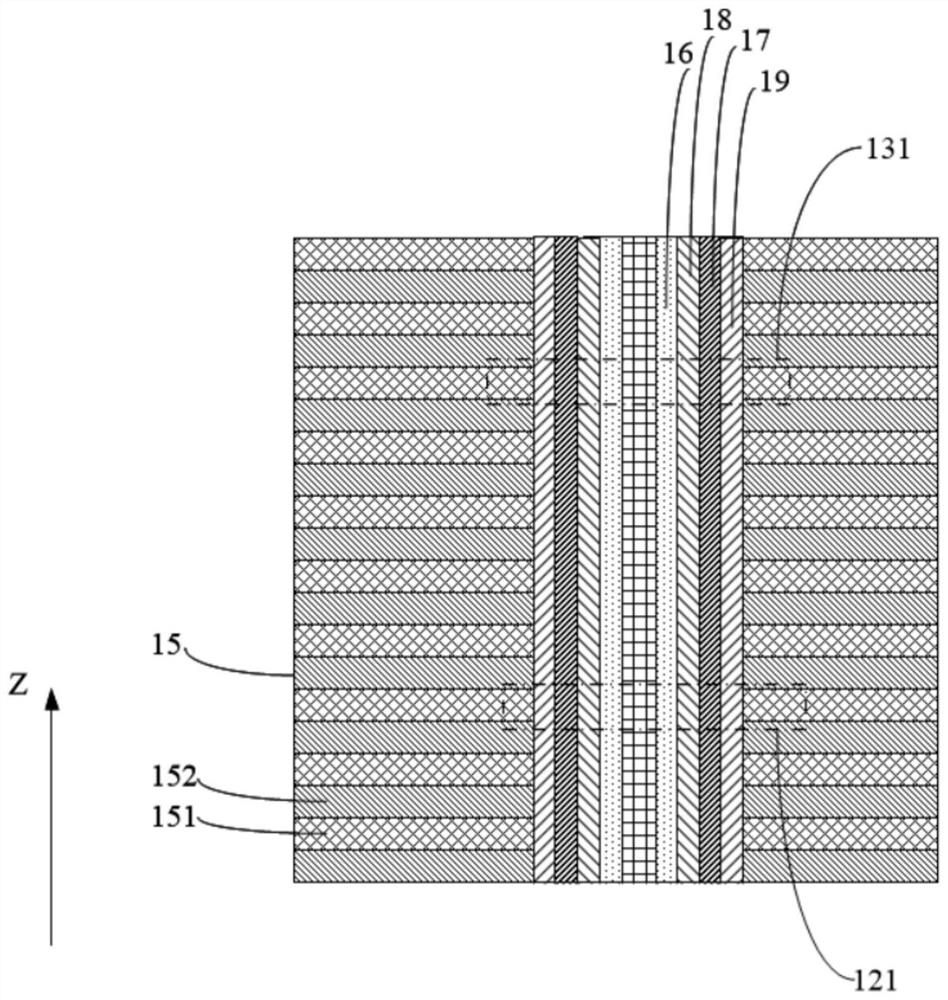

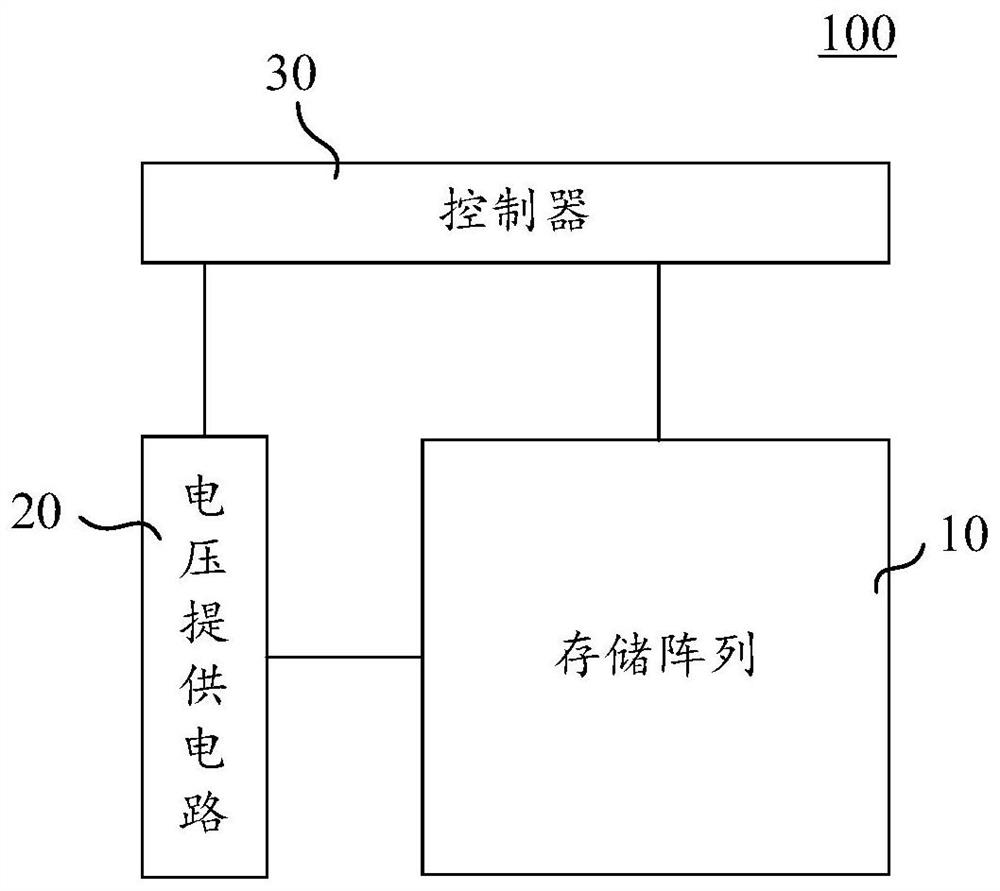

Programming operation method and device of memory

ActiveCN112802505ALow densityProgram disturbSolid-state devicesRead-only memoriesMemory cellSoftware engineering

The invention relates to a programming operation method and device of a memory; the memory comprises a first input end, a first storage string, a second storage string and a second input end which are sequentially arranged in a preset direction; the first storage string comprises a plurality of first storage units which are connected in series, and the second storage string comprises a plurality of second storage units which are connected in series. The programming operation method comprises the steps of performing pre-charging of programming operation, including providing a first preset voltage for a first input end and providing a second preset voltage for a gate layer of a first memory cell so as to pre-charge a channel in a first memory string; performing programming operation to program the second storage unit, so that when the programming operation is carried out on the second storage string, the charge density of a channel can be effectively reduced in the pre-charging stage of the programming operation, and the programming interference is further reduced.

Owner:YANGTZE MEMORY TECH CO LTD

Split-gate flash memory unit and forming method thereof

ActiveCN102347281BReduce height differenceReduce voltageSolid-state devicesSemiconductor/solid-state device manufacturingCouplingMiniaturization

The invention provides a split-gate flash memory unit and a forming method thereof. The split-gate flash memory unit comprises a semiconductor substrate, a source line polycrystalline silicon layer which is located on the surface of the semiconductor substrate, a source electrode which is located in the semiconductor substrate aligned to the source line polycrystalline silicon layer, a coupling oxide layer and a floating gate which are sequentially located on the semiconductor substrate surfaces at two sides of the source polycrystalline silicon layer, a side wall medium layer which is used for electrically isolating the source wire line polycrystalline silicon from the coupling oxide layer and the floating gate, a coupling oxide layer which is located on the side wall of the floating gate far away from the source line polycrystalline silicon layer, an epitaxial layer which is located on the surface of the semiconductor substrate at one side of the coupling oxide layer far away from the source line polycrystalline silicon layer, tunneling oxide layers which are located on the surface of the epitaxial layer and on the side wall of the side medium layer far away from the source line polycrystalline silicon layer, word line polycrystalline silicon layers which are located on the surfaces of the tunneling oxide layers, and drainage electrodes which are located in the epitaxial layer at one side of the word line polycrystalline silicon layer far away from the floating gate and the semiconductor substrate. With the adoption of the split-gate flash memory unit provided by the invention, the programming efficiency of the split-gate flash memory unit can be improved and the miniaturization is easy to realize.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

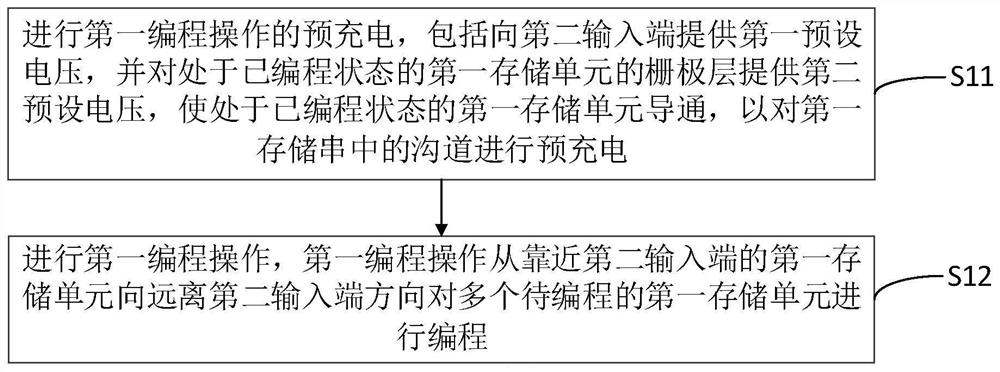

Programming operation method and device of memory

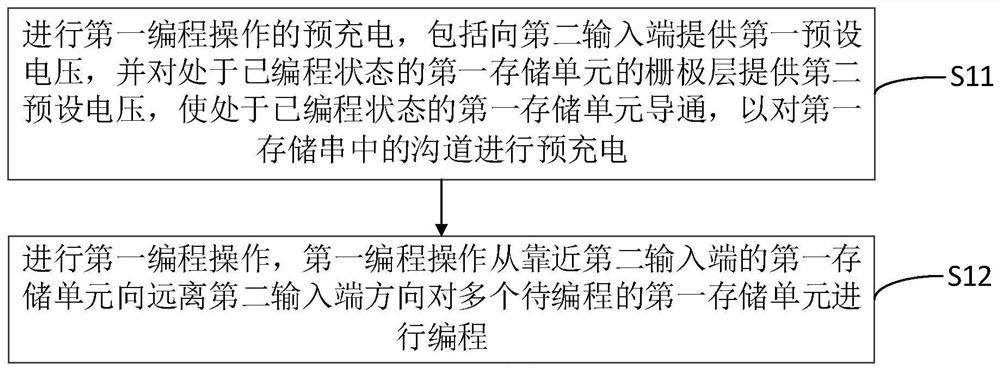

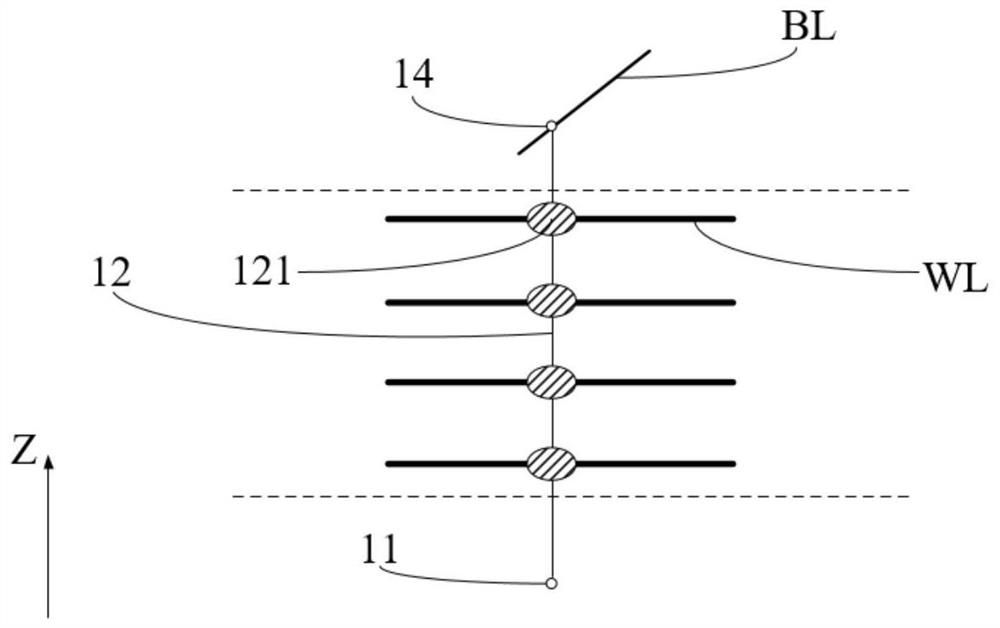

ActiveCN112820329AAvoid the problem of not being able to effectively increase the channel potentialProgram disturbRead-only memoriesMemory cellParallel computing

The invention relates to a programming operation method and device of a memory, the memory comprises a first memory string, a first input end and a second input end, the first input end and the second input end are located at the two ends of the first memory string, the first memory string comprises a plurality of first memory cells connected in series, and the programming operation method comprises the following steps: performing pre-charging of a first programming operation, providing a first preset voltage for a second input end, and providing a second preset voltage for a gate layer of a first memory cell in a programmed state, so that the first memory cell in the programmed state is conducted, and a channel in a first memory string is pre-charged; carrying out first programming operation, wherein the first programming operation carries out programming on the multiple to-be-programmed first storage units from the first storage unit close to the second input end to the direction away from the second input end, and therefore when programming operation is carried out on the storage string, the charge density of a channel can be effectively reduced in the pre-charging stage of the programming operation. And the programming interference is further reduced.

Owner:YANGTZE MEMORY TECH CO LTD

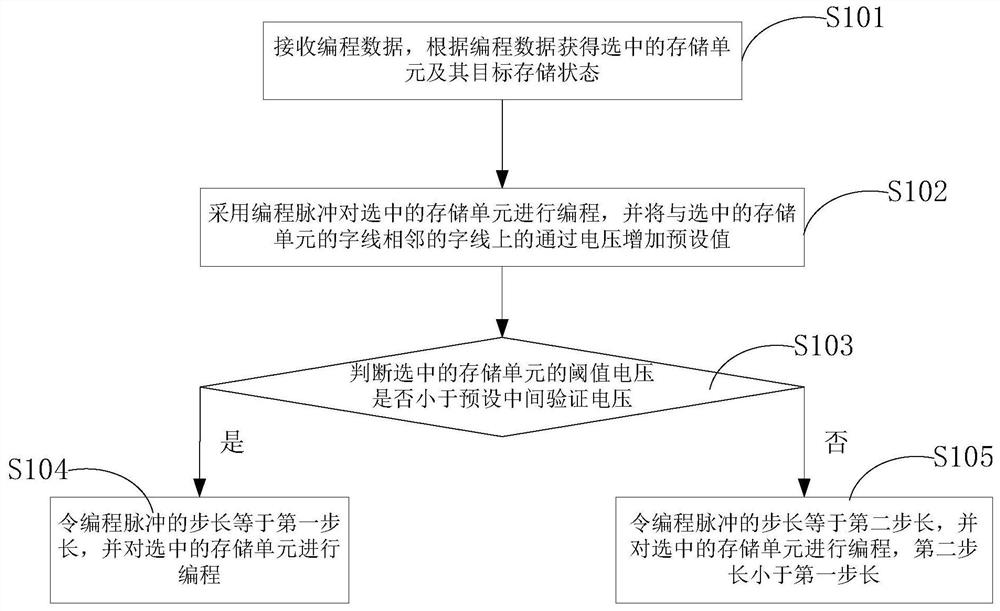

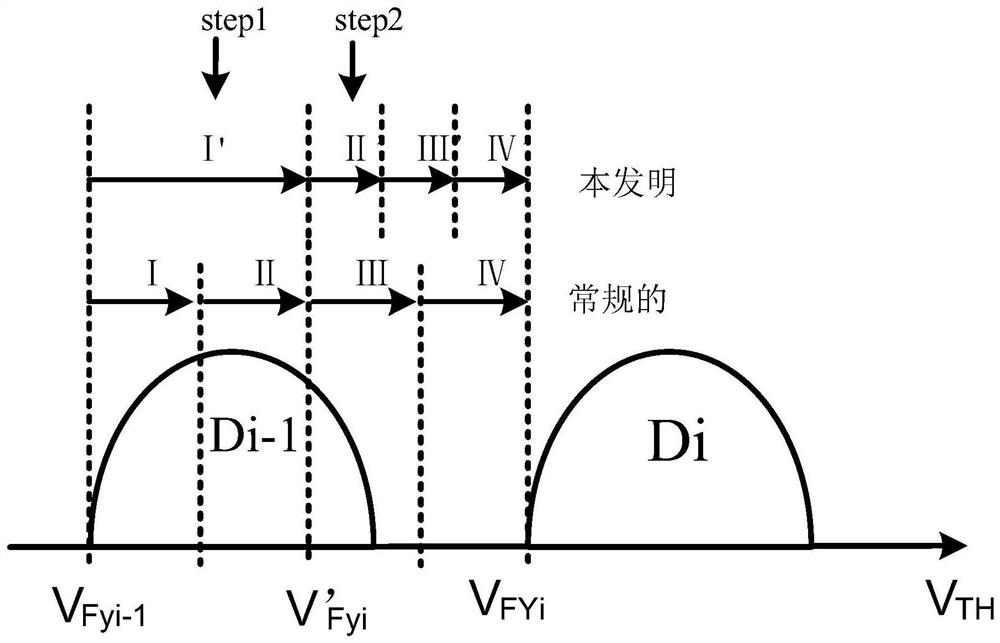

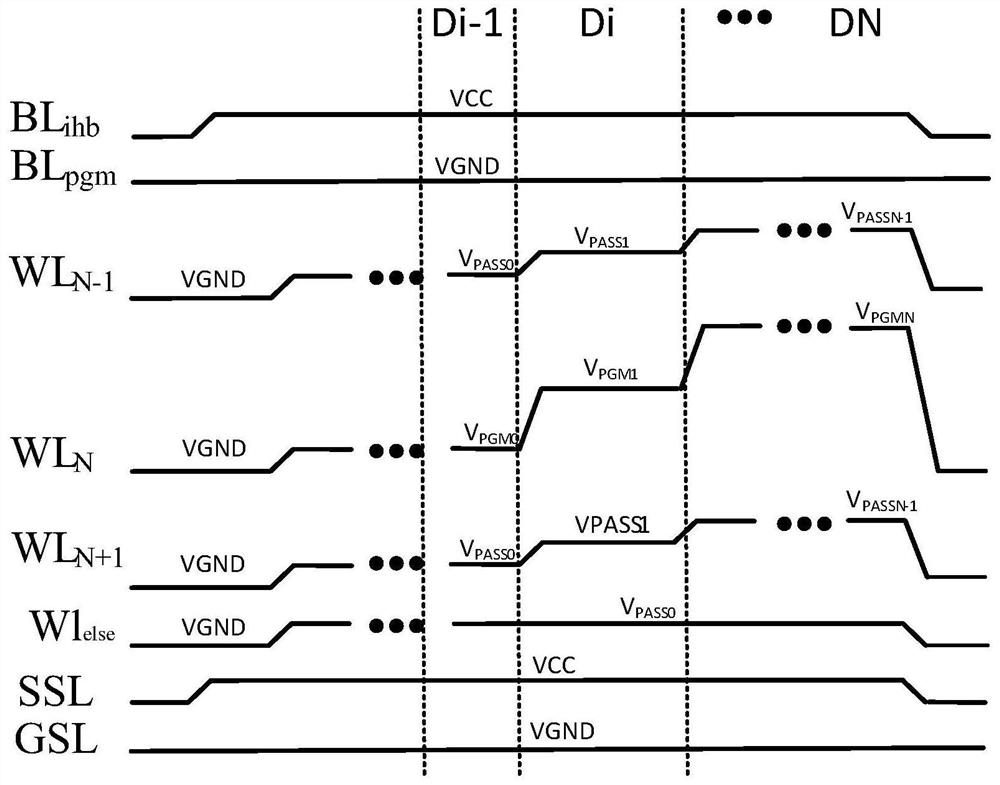

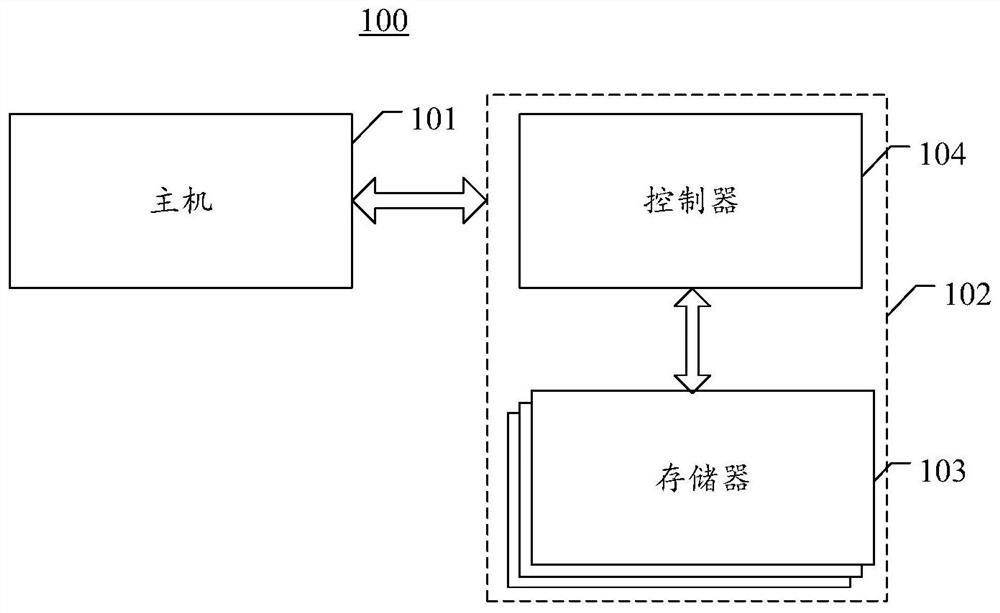

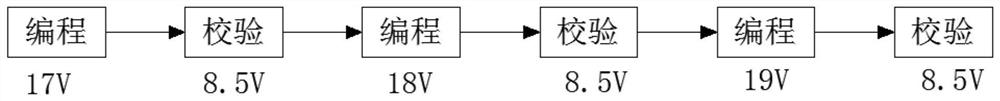

A memory programming method and programming system

ActiveCN110993007BShorten programming timeProgram disturbRead-only memoriesProgramming languageMemory cell

The programming method and programming system of the memory provided by the present invention include: obtaining the selected storage unit and its target storage state, i.e. the i-th state, according to the programming data; The pass voltage on the word line adjacent to the word line of the unit is increased by a preset value; it is judged whether the threshold voltage of the selected memory cell is less than a preset intermediate verification voltage, and the preset intermediate verification voltage is less than the verification voltage of the i-th state and greater than the i-th verification voltage ‑1 state verification voltage; if yes, make the programming pulse step equal to the first step, and program the selected memory cell; if not, make the programming pulse step equal to the second step, and program the selected memory cell The unit is programmed with a second step size smaller than the first step size. Since the pass voltage on the adjacent word lines is increased when programming is started in the present invention, the programming interference of the word line of the selected memory cell to the adjacent word lines can be reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Memory, memory system and pre-charging method

The embodiment of the invention discloses a memory, a storage system and a pre-charging method, and belongs to the technical field of storage. The pre-charging method comprises the following steps: applying a pre-charging voltage to a source line connecting end; applying a voltage to the gate of each memory cell in the memory cell stack; wherein the voltage applied to the grid electrode of the programmed storage unit is greater than the threshold voltage of the programmed storage unit, and the voltage applied to the grid electrode of the non-programmed storage unit is greater than the threshold voltage of the non-programmed storage unit. According to the method, the electrons in the doped region and the electrons in the channel of the memory cell coupled with the selected word line can be fully attracted to the source line connecting end under the condition that the programmed memory cell exists in the memory cell stack, so that the non-selected memory string can be fully pre-charged; and the programming interference suffered by the memory unit coupled with the selected word line in the memory unit stack is reduced.

Owner:YANGTZE MEMORY TECH CO LTD

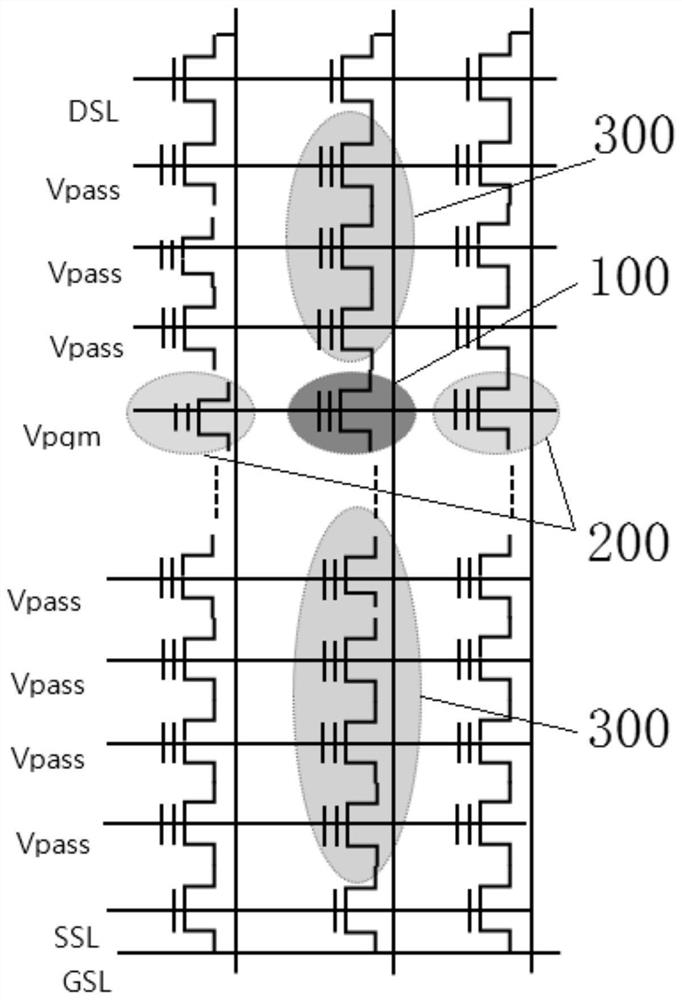

Programming method capable of reducing programming interference of memory cell difficult to program

The invention relates to a programming method capable of reducing programming interference of a storage unit difficult to program. The method comprises the following steps of S1, programming operationbeing conducted on the storage unit of a storage area of an NAND FLASH through programming voltage; S2, performing first verification operation on the programmed memory cell by adopting the first verification voltage, and if the verification succeeds, entering the step S3; if the verification fails, returning to the step S1; S3, performing a second verification operation on the programmed memorycell by adopting a second verification voltage, and if the verification is successful, ending; if the verification fails, entering the step S4; wherein the first verification voltage is smaller than the second verification voltage; S4, adding 1 to the number of cycles for counting, and ending if the number of cycles reaches a preset number-of-cycles threshold value; if not, executing the step S5;and S5, increasing the programming voltage, and then returning to the step S1. The programming method is novel in design, and programming interference can be effectively reduced.

Owner:XTX TECH INC

Memory programming operation method and device

ActiveCN112820329BAvoid the problem of not being able to effectively increase the channel potentialProgram disturbRead-only memoriesComputer hardwareComputer architecture

The present invention relates to a programming operation method and device for a memory. The memory includes a first storage string, a first input terminal and a second input terminal located at both ends of the first storage string, and the first storage string includes a plurality of first memory strings connected in series. The unit, the programming operation method includes: performing the precharging of the first programming operation, including providing the first preset voltage to the second input terminal, and providing the second preset voltage to the gate layer of the first memory cell in the programmed state , turn on the first memory cell in the programmed state, so as to precharge the channel in the first memory string; perform the first programming operation, the first programming operation is from the first memory cell close to the second input terminal to far away The direction of the second input terminal is used to program a plurality of first memory cells to be programmed, so that when the memory string is programmed, the charge density of the channel can be effectively reduced in the pre-charging stage of the programming operation, thereby reducing the programming interference.

Owner:YANGTZE MEMORY TECH CO LTD

Memory programming operation method and device

ActiveCN112802505BLow densityProgram disturbSolid-state devicesRead-only memoriesComputer hardwareComputer architecture

Owner:YANGTZE MEMORY TECH CO LTD

Memory system and programming method thereof

ActiveCN113284541BLower programming voltageProgram disturbRead-only memoriesDigital storageMemory cellParallel computing

The application provides a storage system and a programming method. Each word line of the memory is connected to a plurality of storage units, the plurality of storage units include a first storage unit and a second storage unit except the first storage unit, and the programming method includes: performing level 1 programming, so that the first storage unit The threshold voltage of the cell is programmed to be greater than or equal to the final verification voltage of the first memory cell, and the threshold voltage of the second memory cell is programmed to be greater than or equal to the first-level intermediate verification voltage, wherein the first-level intermediate verification voltage of the memory cell is lower than the final verification voltage voltage, the threshold voltage of the first memory cell is greater than the threshold voltage of the second memory cell; and performing Nth level programming, configuring the threshold voltage of a plurality of second memory cells to be greater than or equal to the final verification voltage, where N≥2.

Owner:YANGTZE MEMORY TECH CO LTD

Method for Inhibiting Programming Disturbance of Flash Memory

InactiveUS20140017870A1Programming speed is not affectedEasy to implementSemiconductor/solid-state device manufacturingSemiconductor devicesDopantManufacturing technology

Disclosed herein is a method for inhibiting a programming disturbance of a flash memory, which relates to a technical field of a non-volatile memory in ultra-large-scale integrated circuit fabrication technologies. In the present invention, an dopant gradient of a PN junction between a substrate and a drain is reduced by adding a step of performing an angled ion implantation of donor dopants into a standard process for a flash memory, so that an electric field of the PN junction between the substrate and the drain is reduced, and consequently the programming disturbance is inhibited. Meanwhile, a dopant gradient of the PN junction between a channel and the drain is maintained, so that an electric field of the PN junction between the channel and the drain, which is necessary for programming, is maintained, and thus the programming efficiency and the programming speed can be ensured. The programming disturbance can be effectively inhibited without increasing numbers of masks used for photolithography according to the invention, thus the present invention is significantly advantageous to the improvement of the flash memory reliability.

Owner:PEKING UNIV

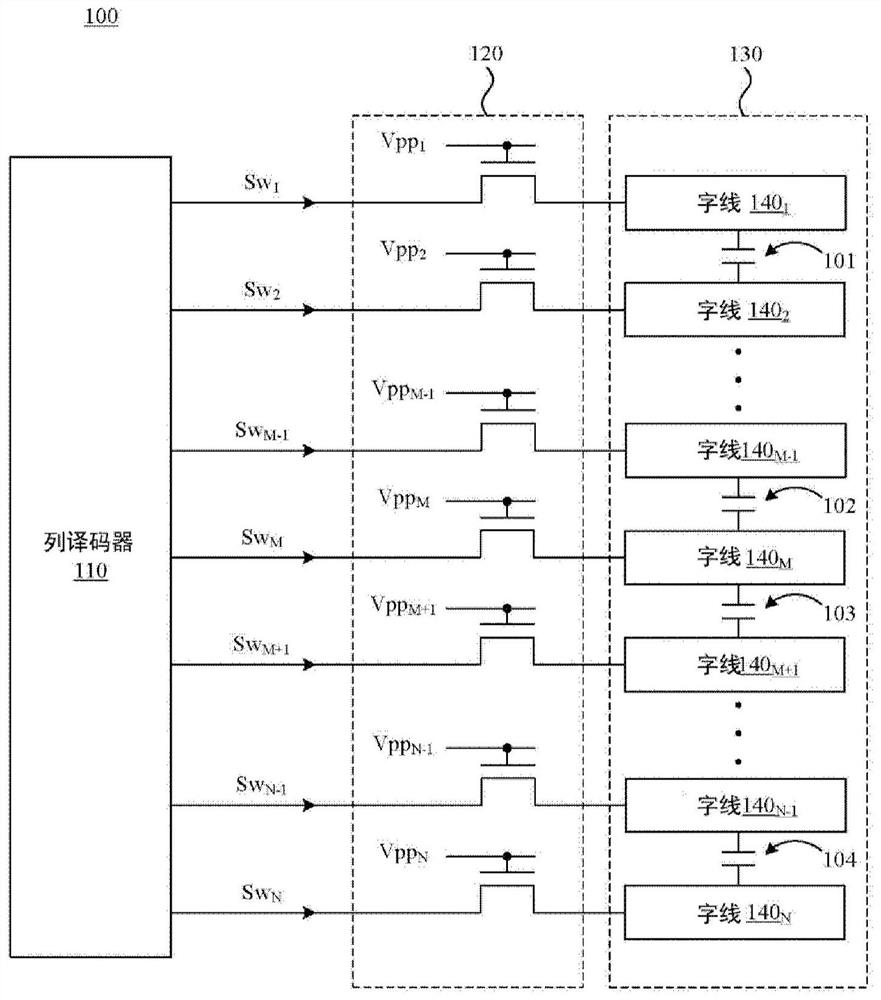

Operation method of non-volatile memory device

ActiveCN112053721AImprove programming efficiencyProgram disturbRead-only memoriesDigital storageEmbedded systemBus

The invention discloses an operation method of a non-volatile memory device. The operation method is suitable for a non-volatile memory device which includes a column decoder and a memory array. The operation method of the non-volatile memory device comprises the following steps of: transmitting a plurality of word signals to the memory array by using the column decoder; switching a selected wordsignal in the plurality of word signals from a preset voltage level to a programming voltage level by using the column decoder according to a bus; switching at least one auxiliary word signal in the plurality of word signals from a preset voltage level to a first pass voltage level by using the column decoder; when the selected word signal is maintained at the programming voltage level, utilizingthe column decoder to switch at least one auxiliary word signal from the first pass voltage level to a second pass voltage level, wherein the second pass voltage level is higher than the first pass voltage level.

Owner:MACRONIX INT CO LTD

Method for reducing programming interference of 3d NAND memory

ActiveCN110211625BProgram disturbReduce differential pressureRead-only memoriesMemory cellSoftware engineering

A method for reducing programming interference of 3D NAND memory. When programming, a selected memory string is used as a selected string, and other memory strings are used as non-selected strings, and a certain memory cell in the selected string is programmed. Apply a programming voltage on the control gate corresponding to the memory cell to be programmed, use the control gate to which the programming voltage is applied as a selection layer, and control gates of other layers as a non-selection layer; A first bias voltage is applied to at least one of the non-selected layers, and a second bias voltage is applied to the remaining selected layers, the first bias voltage is smaller than the second bias voltage, and the first bias voltage and The second bias voltages are all lower than the programming voltage. The method of the present invention reduces the programming disturbance to the memory cell in the non-selected string which is located in the same layer as the programmed memory cell.

Owner:YANGTZE MEMORY TECH CO LTD

Non-volatile memory

ActiveUS10283511B2Avoid it happening againOperation efficiency can be improvedSemiconductor/solid-state device detailsSolid-state devicesEngineeringNon-volatile memory

A non-volatile memory including memory cells is provided. Each of the memory cells includes a substrate, a floating gate structure, a select gate structure, and a first doped region. The floating gate structure is disposed on the substrate. The select gate structure is disposed on the substrate and located at one side of the floating gate structure. The first doped region is disposed in the substrate at another side of the floating gate structure. The first doped regions between two adjacent memory cells are adjacent to one another and separated from one another.

Owner:EMEMORY TECH INC