Method for reducing programming interference of 3d NAND memory

A programming interference and memory technology, applied in static memory, read-only memory, information storage, etc., can solve problems such as memory cell programming interference, and achieve the effect of reducing programming interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] As mentioned in the background art, in the prior art, when programming a certain memory cell in a certain channel hole, it is easy to cause programming interference to other corresponding memory cells in the same layer in other channel holes.

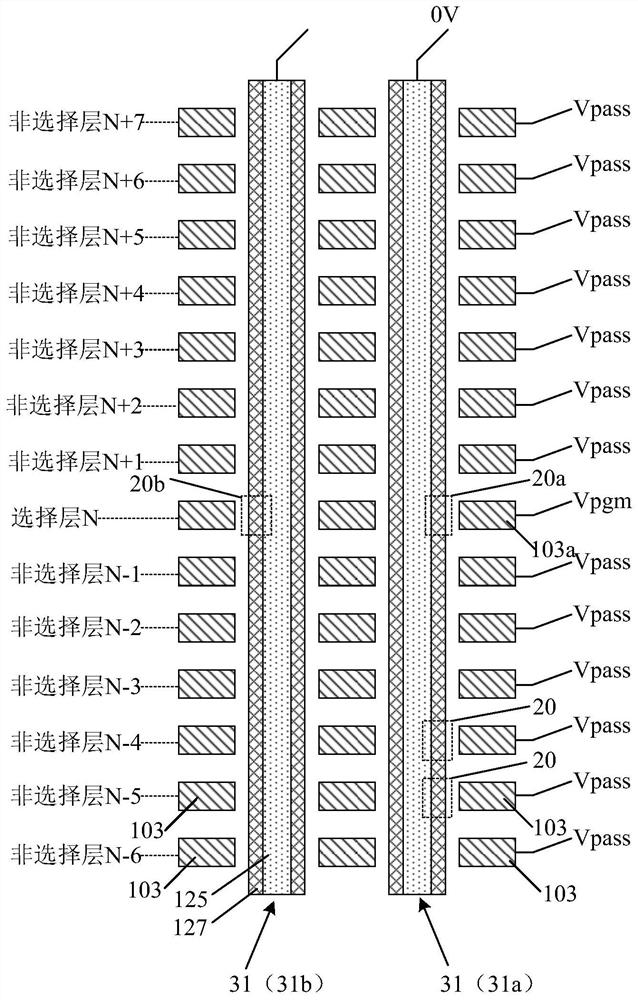

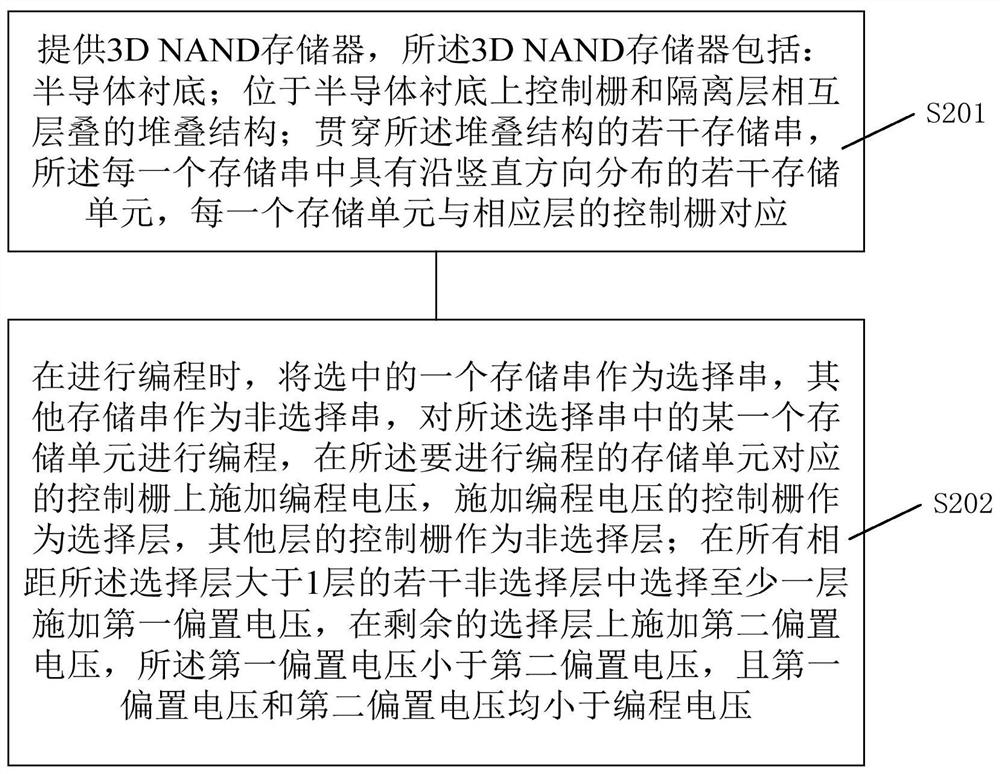

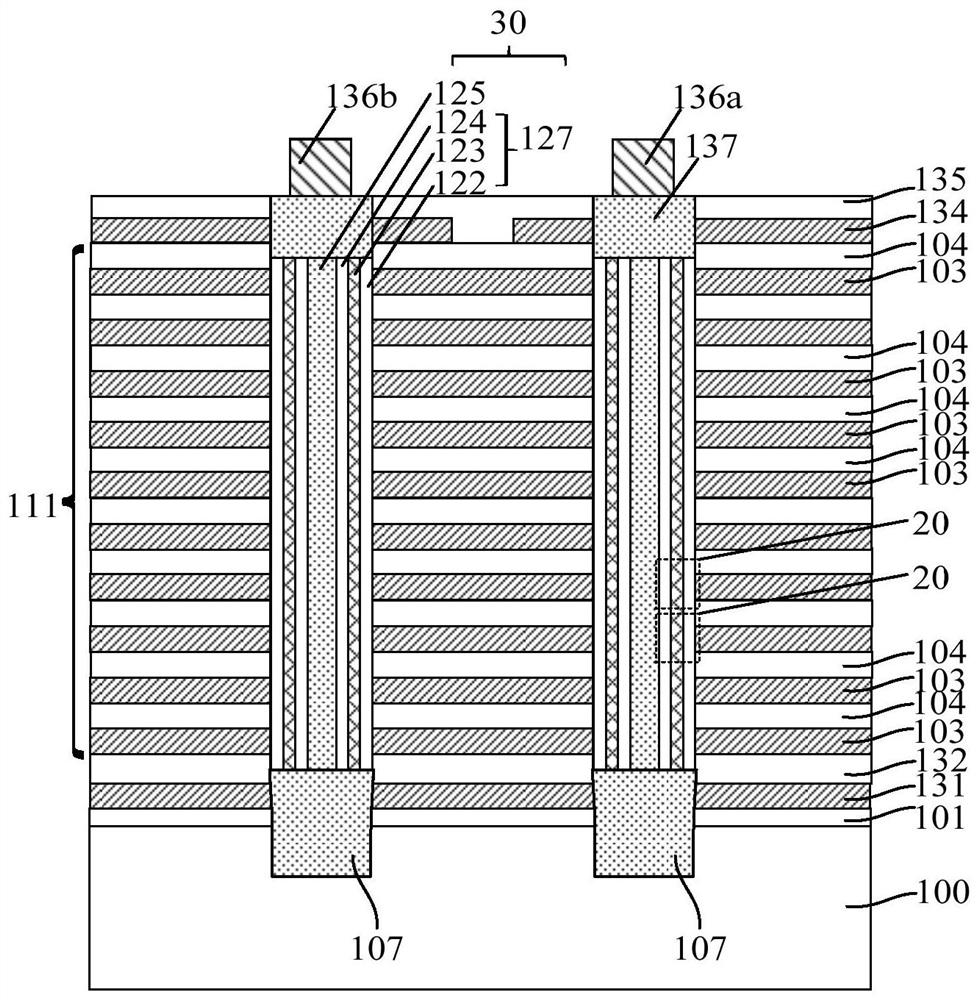

[0032]To this end, an embodiment of the present invention provides a 3D NAND memory programming method, including: providing a 3D NAND memory, refer to figure 1 , the 3D NAND memory includes: a semiconductor substrate; a stack structure in which the control gate 103 and the isolation layer are stacked on the semiconductor substrate; a number of storage strings 30 running through the stack structure, and each storage string 30 includes a channel Layer 125 and the storage layer 125 located on the sidewall of the channel layer, the position of the storage layer 125 corresponding to the control gate 103 of the corresponding layer is a storage unit 20, so that each storage string has several storage cells distributed along the vertical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More